Preparation method for LED chip capable of forming light spots with specific planar geometric patterns through illumination, and structure of LED chip

A technology of LED chips and geometric figures, applied to electrical components, circuits, semiconductor devices, etc., can solve problems such as normal light intensity, uneven light distribution, and uneven spatial distribution of light

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The method and structure of an LED chip that irradiates light spots of a specific plane geometric pattern proposed by the present invention will be described in detail below with reference to the accompanying drawings and specific embodiments. It should be noted that the drawings of the present invention all adopt very simplified and inaccurate scales, which are only used to facilitate and clearly illustrate the present invention.

[0054] For ease of understanding, first briefly describe the whole process of preparing a LED chip with a vertical structure proposed by the present invention:

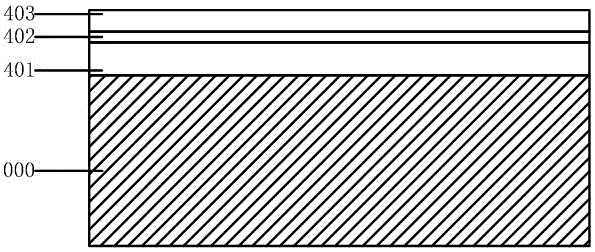

[0055] A. Grow gallium nitride-based LED thin films on the substrate material, that is, prepare epitaxial wafers;

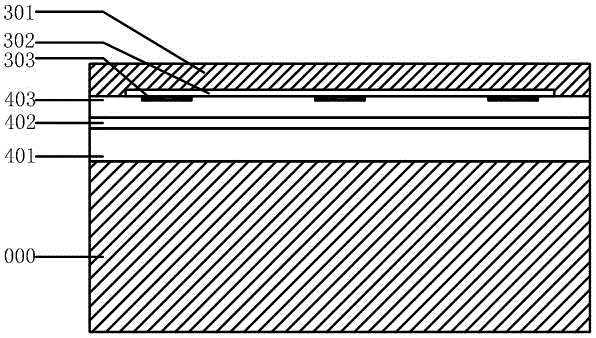

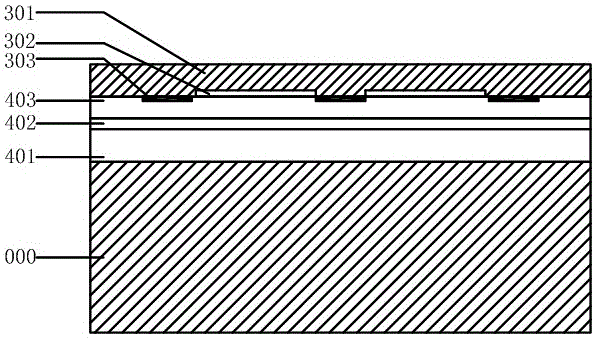

[0056] B. Prepare a complementary structure on the surface of the epitaxial wafer so that it corresponds to the n-electrode pattern or contains a specific plane geometry;

[0057] C. Depositing a reflective metal contact layer on the surface of the epitaxial...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More