Chip packaging structure

A chip packaging structure and chip technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of low integration and anti-interference ability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

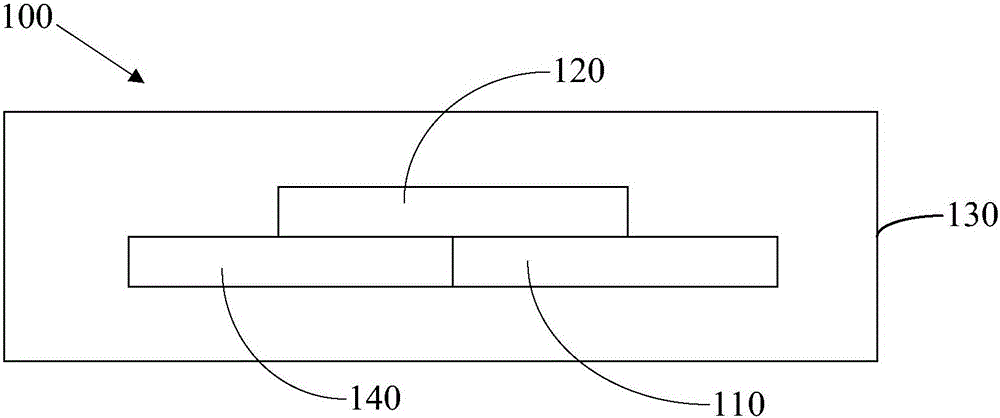

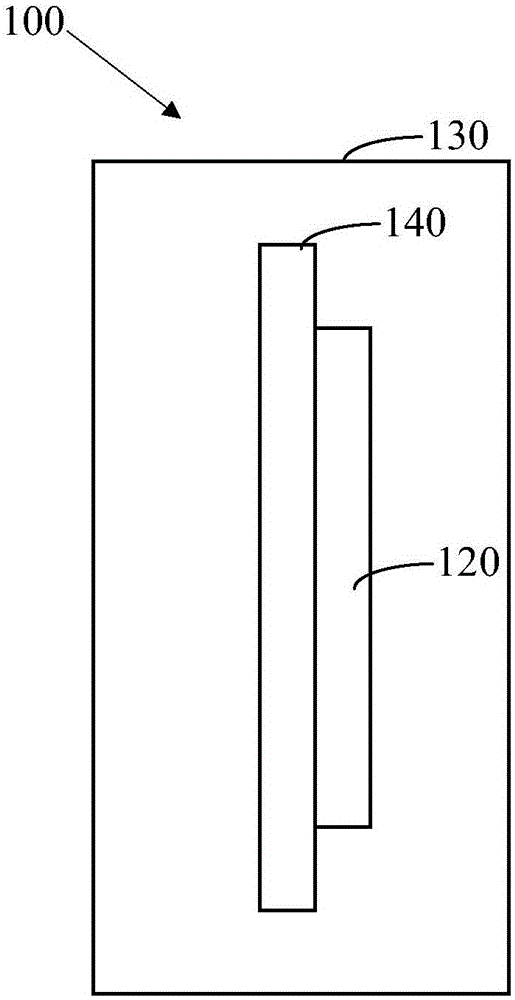

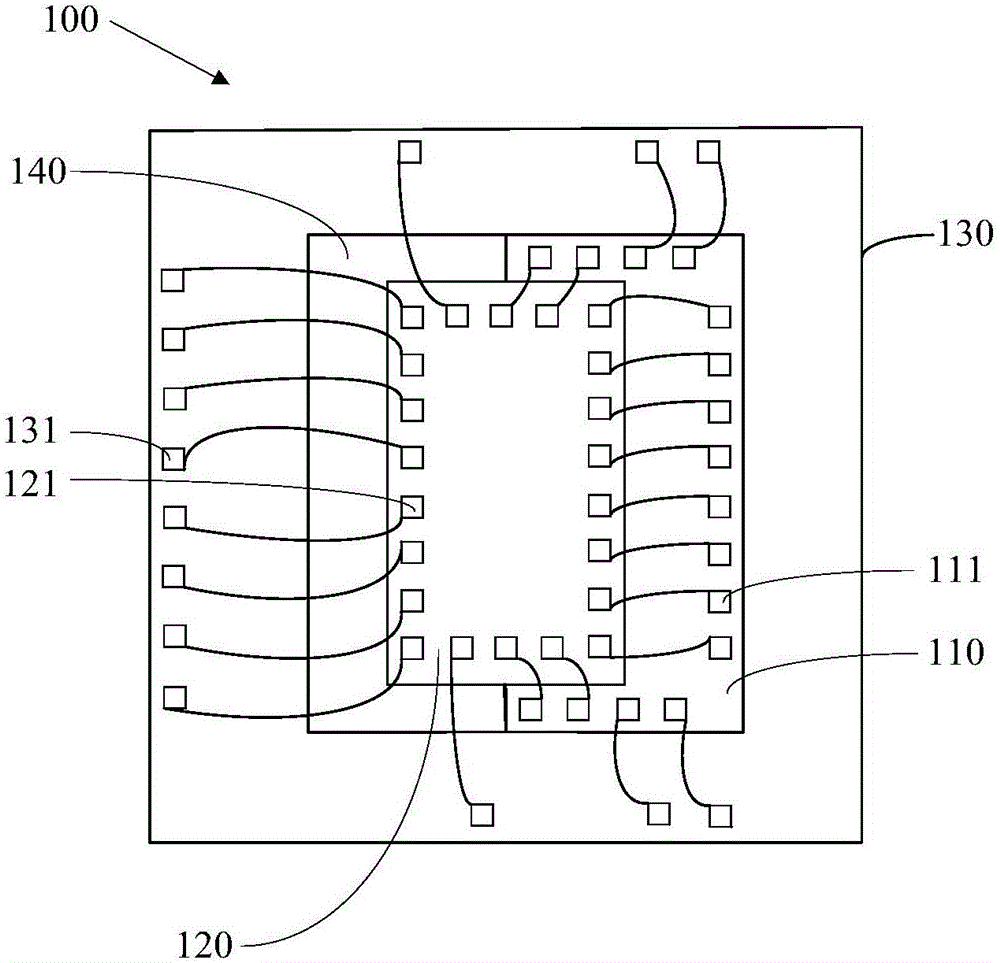

[0037] In order to make the technical solution of the present invention more clear, the technical solution of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0038] First of all, it should be noted that the first chip and the second chip mentioned in the present invention refer to various functional chips in the integrated circuit, such as: FLASH (flash memory) chip, SRAM (static random access memory) chip and DRAM (Dynamic Random Access Memory) chips, etc. No more examples here.

[0039] Wherein, both the first chip and the second chip have a circuit surface and a reverse surface opposite to the circuit surface. The circuit side refers to a side provided with a corresponding circuit layout. That is to say, the first chip in the present invention has a first circuit surface and a first reverse surface opposite to the first circuit surface. Correspondingly, the second chip has a second ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More