Compatibility scan chain compression method based on at least clique covering

A compression method and scan chain technology, applied in the direction of electrical components, code conversion, etc., can solve the problems of reduced compression effect and only one, and achieve the effect of compressing width and reducing length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in further detail below according to the drawings and embodiments.

[0029] The present invention, refer to Figure 4 , a compatible scan chain compression method based on least clique coverage, the steps include:

[0030] Without loss of generality, the original test data of multiple scan chains and multiple bit sequences of each scan chain are shown in Table 1.

[0031] Table 1 scan chain arrangement

[0032]

[0033]

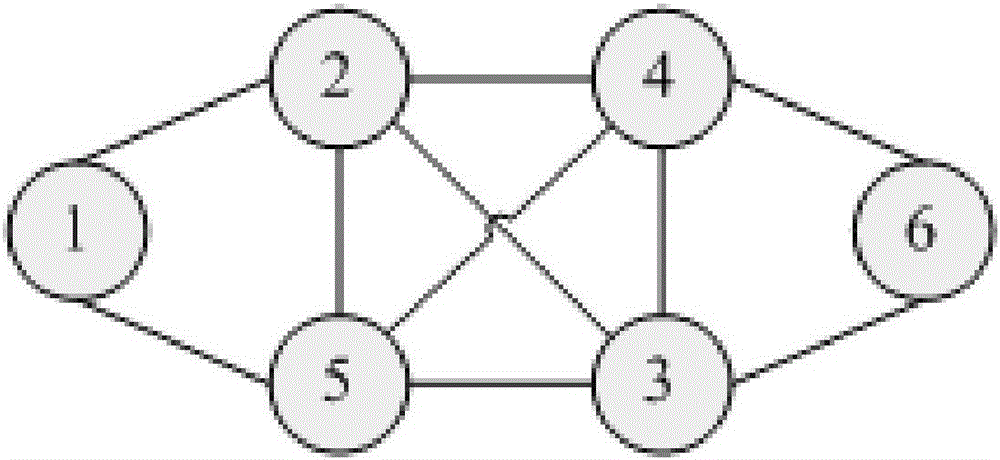

[0034] (a) Construct an undirected graph G. Treat each scan chain as a vertex of the graph, and add an edge between the two vertices if the two scan chains are compatible. According to this method, the compatibility relationship of the scan chain can be constructed as an undirected graph G=(V, E), where V is a set of vertices, and E is a set of edges. The undirected graph G constructed according to the compatibility relationship of the scan chain in Table 1 is as figure 1 shown.

[0035] (b) Copy the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com