Clock synchronization method

A clock synchronization and clock technology, applied in the direction of electrical components, automatic power control, generation/distribution of signals, etc., can solve problems such as difficult timing design, achieve the effect of easy timing design and ensure delay time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] Hereinafter, the clock synchronization method of the present invention will be described in detail according to preferred embodiments shown in the accompanying drawings.

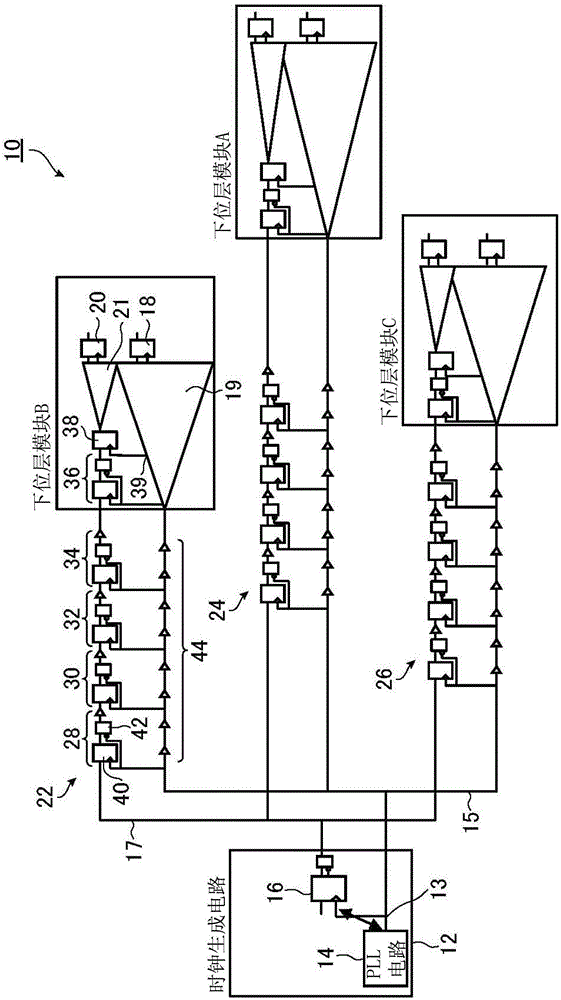

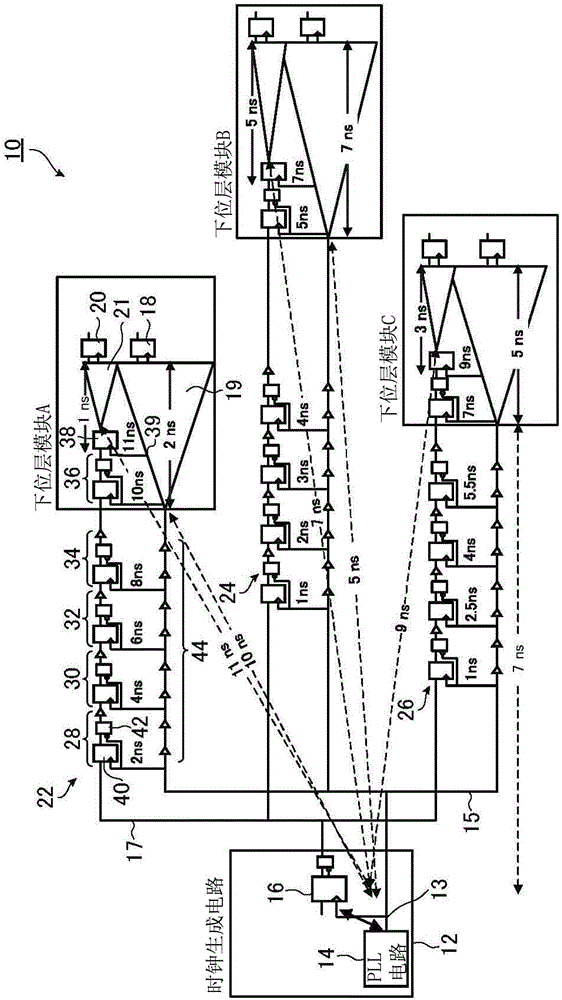

[0062] figure 1 It is a circuit diagram showing one embodiment of the structure of a semiconductor integrated circuit designed by applying the clock synchronization method of the present invention. The semiconductor integrated circuit 10 shown in this figure is a circuit designed by applying the clock synchronization method of the present invention and by a hierarchical layout design method, and has three lower layer modules A, B, C, and modules A, B, and C in addition to the lower layer modules. Top-level modules other than B and C.

[0063] The top module includes a clock generating circuit 12, the clock generating circuit 12 includes a PLL circuit 14 that generates a reference clock 15 with a constant cycle (frequency), and divides the reference clock 15 generated by the PLL circuit 14 by n (n is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More