Compact three-dimensional memory

A technology of memory and storage devices, applied in static memory, instruments, electric solid state devices, etc., can solve problems such as difficult wiring of substrate circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

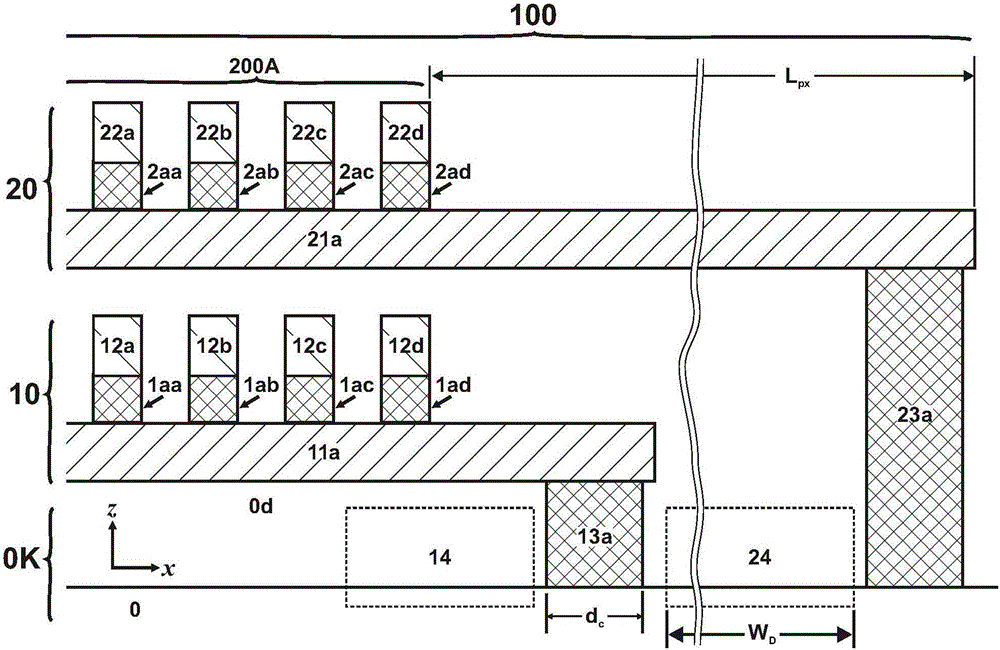

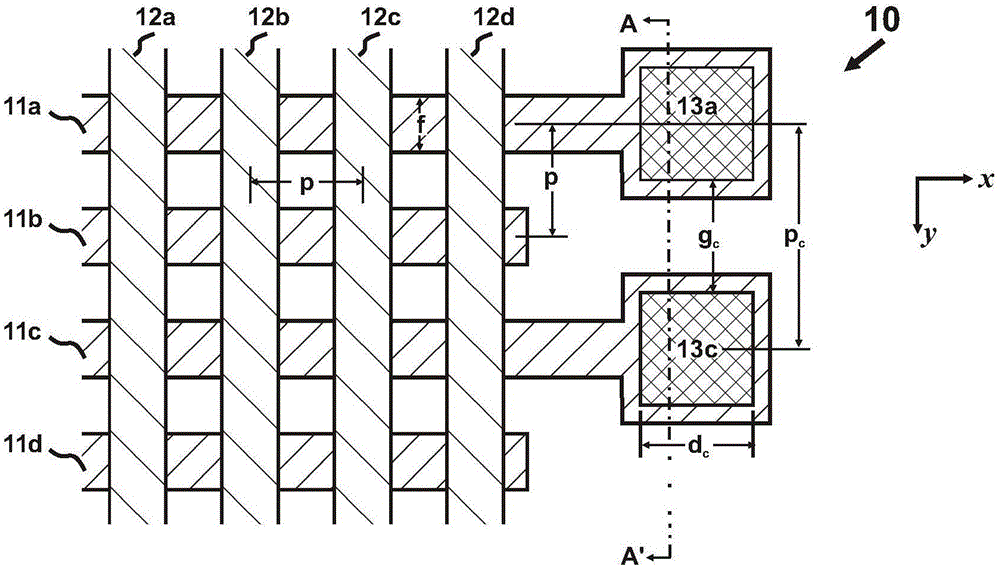

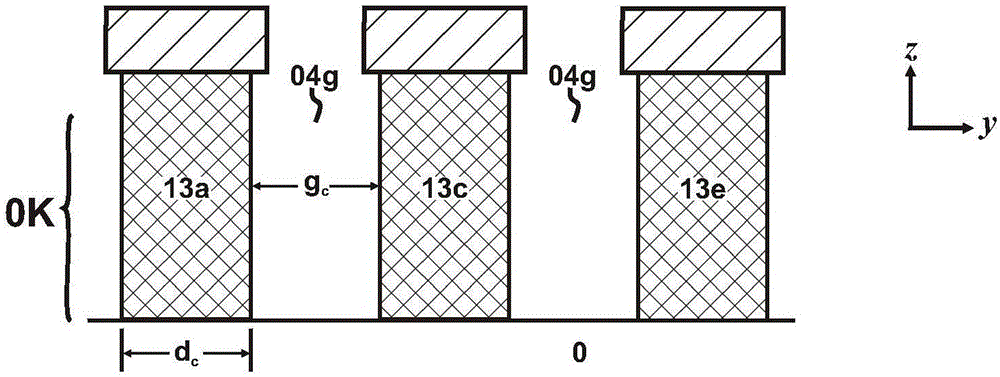

[0040] Figure 2A-Figure 2E described the first compact three-dimensional memory (3D-M C ), which includes an inner decoding stage. The 3D-M C Contains two storage layers 10, 20 stacked on the substrate 0 ( Figure 2C ). The storage layer 10 contains a storage array 100A and an intra-layer decoding stage 100P (see Figure 2A The circuit diagram in and Figure 2D top view of the ). Memory array 100A contains a plurality of x address lines 11a-11h, a plurality of y address lines 12a-12d, and a plurality of memory devices 1aa-1ad ( Figure 2A ). The intra-layer decoding stage 100P selects one address line from the two address lines of the same storage layer. It contains two control lines 17a, 17b and a plurality of simple switching devices 3aa, 3cb, 3ea, 3gb and so on. Switching device 3aa is formed at the intersection of control line 17a and x-address line 11a, between memory devices 1aa-1ad and contact via hole 13a ( Figure 2D ). The switching device 3aa is generally ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More