DES algorithm round iteration system and method based on coarse-grained reconfigurable architecture

A coarse-grained, iterative technology, applied in the field of embedded reconfigurable systems, can solve problems such as method and system inapplicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] Below in conjunction with accompanying drawing and specific embodiment, further illustrate the present invention, should be understood that these examples are only for illustrating the present invention and are not intended to limit the scope of the present invention, after having read the present invention, those skilled in the art will understand various aspects of the present invention All modifications of the valence form fall within the scope defined by the appended claims of the present application.

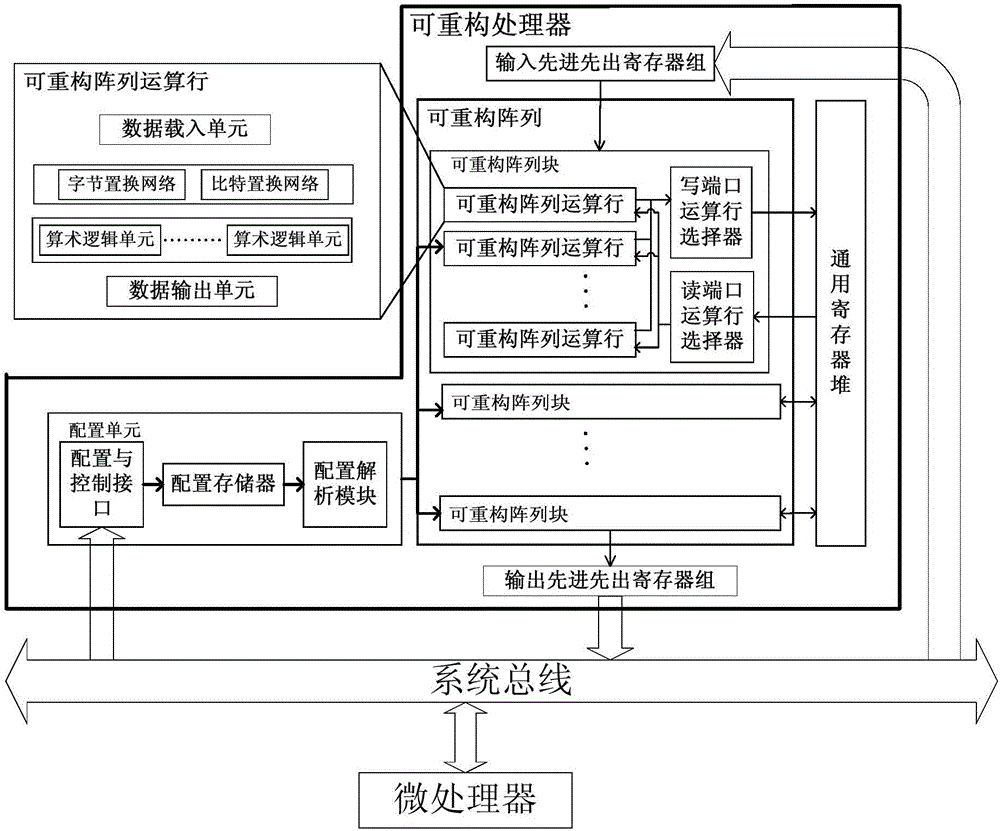

[0068] A DES algorithm round iteration system based on a coarse-grained reconfigurable architecture, such as figure 1 shown, including the system bus, reconfigurable processor, and microprocessor. The microprocessor sends plaintext data to the reconfigurable processor through the system bus, and the plaintext data will be stored in the input FIFO register group, and after the final calculation is completed, the ciphertext data will be output to the output FIFO regist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More