Semiconductor device

A semiconductor and conductive technology, applied in the direction of semiconductor devices, diodes, electrical components, etc., can solve the problems of high aspect ratio and poor coverage of electrode terminal steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

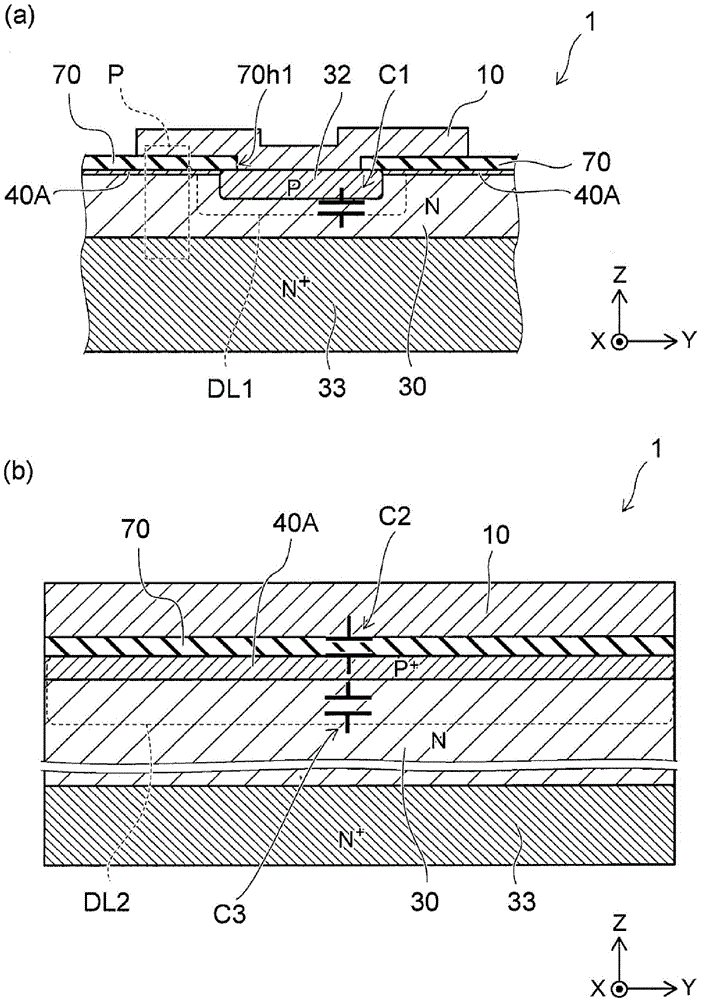

[0016] figure 1 (a) is a schematic sectional view showing a main part of the semiconductor device of the first embodiment, figure 1 (b) is figure 1 An enlarged view of the area enclosed by the dotted line P in (a).

[0017] The semiconductor device 1 according to the first embodiment is an LGA (Land Grid Array) type semiconductor chip including electrode pads (hereinafter, wiring layer 10 ) having a relatively wide area on the surface side.

[0018] The semiconductor device 1 includes an N-type first semiconductor region (hereinafter, for example, the semiconductor region 30 ), a P-type second semiconductor region (hereinafter, for example, the semiconductor region 32 ), a P-type semiconductor region, and a P-type semiconductor region. + type third semiconductor region (hereinafter, eg, semiconductor region 40A), the insulating layer 70 having the first opening (hereinafter, eg, opening 70h1 ), and the wiring layer 10 .

[0019] The semiconductor region 32 is selectively pr...

no. 2 approach

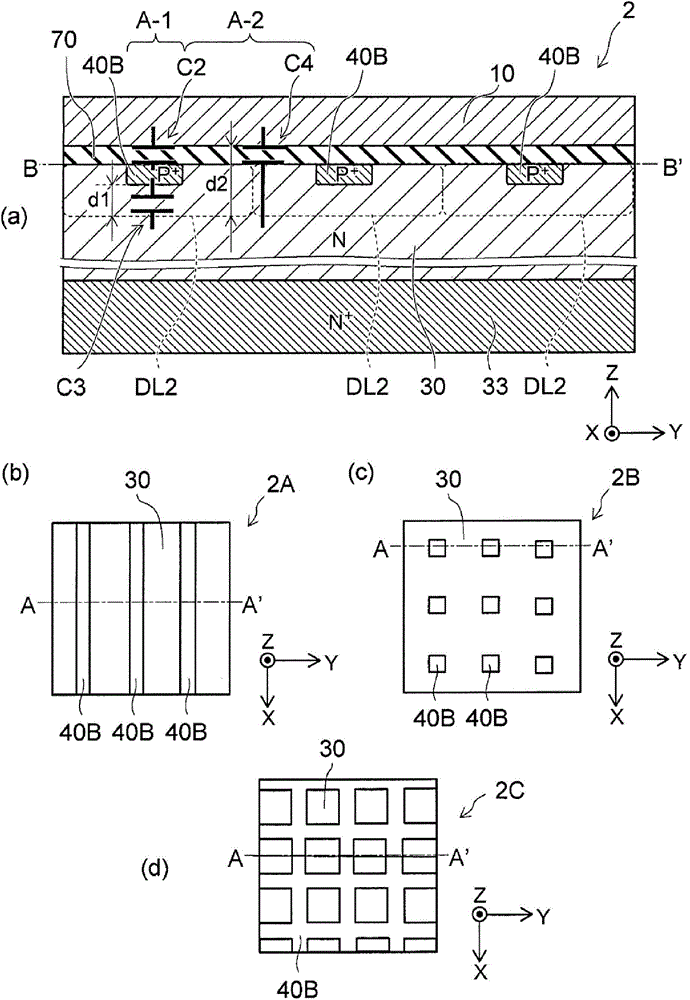

[0036] image 3 (a) shows the main part of the semiconductor device of the second embodiment, and is image 3 (b), (c), (d) schematic cross-sectional view of the line A-A', image 3 (b), (c), (d) are looking down image 3 (a) Schematic plan view taken along the BB' line cut section. Furthermore, image 3 (a) Same as that shown in the first embodiment figure 1 Corresponds to the area surrounded by the dotted line P in (a). A cross-sectional view of this region is shown in the second embodiment, and the characteristics of this region will be described.

[0037] In the semiconductor device 2 of the second embodiment, P + A plurality of semiconductor regions 40B of type are provided under the insulating layer 70 . P + The type semiconductor region 40B includes a plurality of regions. A plurality of regions are arranged at regular intervals, for example. The semiconductor region 40B is in contact with the N-type semiconductor region 30 . The semiconductor region 40B is in ...

no. 3 approach

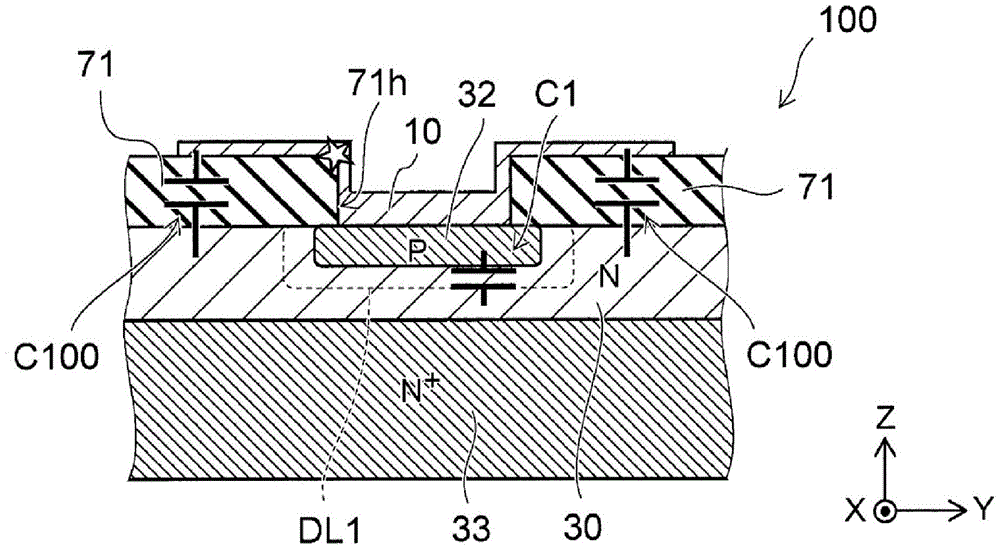

[0045] Figure 4 It is a schematic cross-sectional view showing the main part of the semiconductor device of the third embodiment.

[0046] In the semiconductor device 3 of the third embodiment, P + A plurality of N-type semiconductor regions 40B are provided in the N-type semiconductor region 30 . According to this configuration, the depletion layer DL2 spreads on the lower side of the semiconductor region 40B, and the depletion layer DL2 also spreads on the upper side of the semiconductor region 40B.

[0047] Therefore, the junction capacitance C3 formed by the junction of the semiconductor region 40B and the semiconductor region 30 is a capacitance in which the junction capacitance C3 - 1 and the junction capacitance C3 - 2 are connected in series. That is to say, the junction capacitance C3 of the semiconductor device 3 is further lower than the junction capacitance C3 of the semiconductor device 2 .

[0048] The planar structure of the semiconductor region 40B of the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com