FPGA-based BISS-C protocol universal controller

A controller and storage controller technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem of limited number of slave devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments, wherein the schematic embodiments and descriptions are only used to explain the present invention, but not as improper limitations to the present invention.

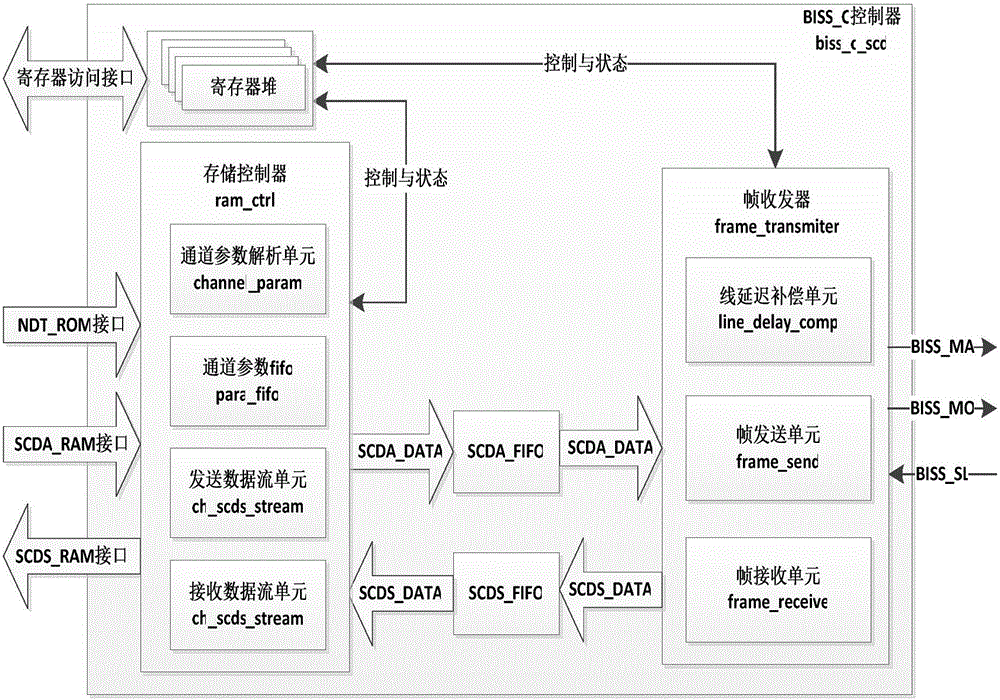

[0035] The overall design of the controller of the invention is compact in structure, powerful in function and flexible in application. It can be easily integrated into mainstream FPGA devices such as xlinx, Altera, and Lattice, and can be directly integrated into verilog circuits, or further packaged into peripheral IP cores of processors. The BISS-C protocol controller of the present invention realized with Lattice FPGA (model is: LCMXO2-1200HC-4TG100C), wherein, the occupancy rate of the register resource of FPGA is 28%, the utilization rate of SLICE resource is 58%, and the utilization rate of LUT4 resource The utilization rate is 57%, meeting the design requirements.

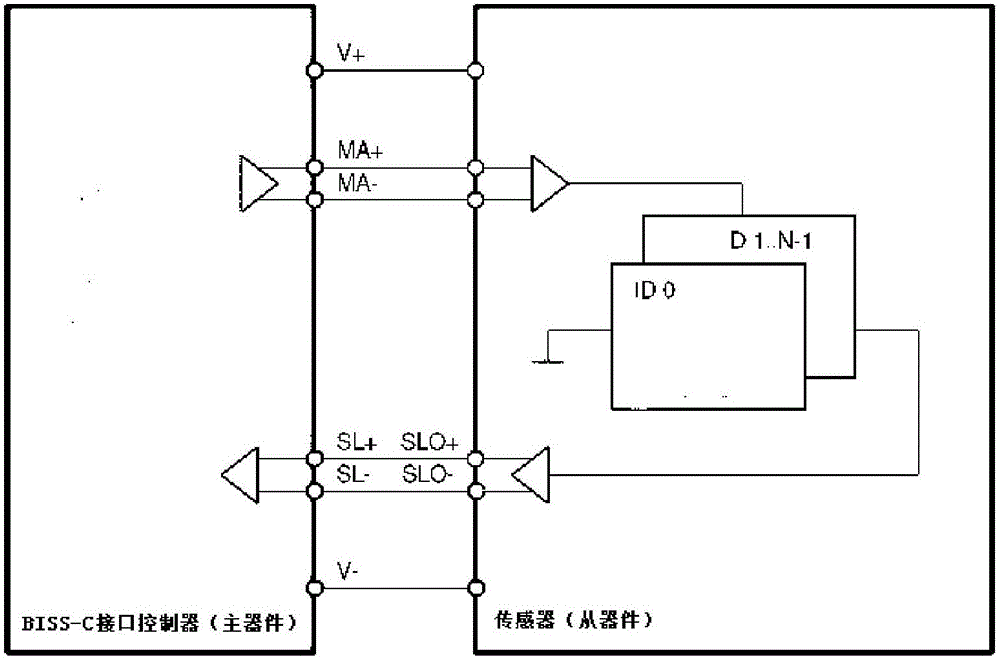

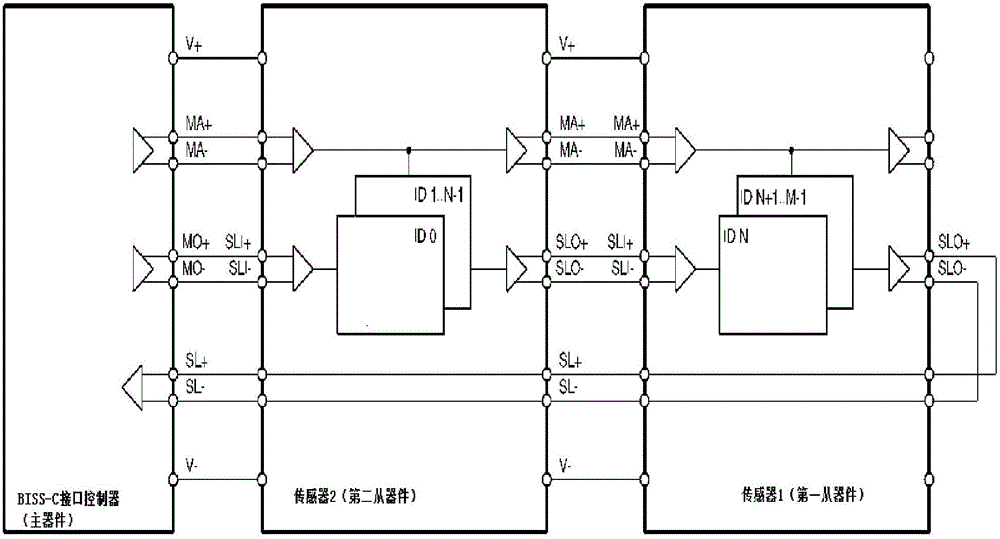

[0036] see f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com