Super junction power device and manufacturing method thereof

A power device and main junction technology, applied in the field of superjunction power devices and manufacturing, can solve the problems of reduced breakdown voltage, reduced ion concentration, and reduced surface breakdown voltage of superjunction power devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] A super junction power device related to this embodiment includes an active region, a voltage divider region, a cutoff ring region, and a scribing track region. The voltage divider region is arranged on the periphery of the active region, and the cutoff ring region is arranged At the periphery of the active area, the scribe track area is arranged at the periphery of the stop ring area. The super junction power device will be described in detail below.

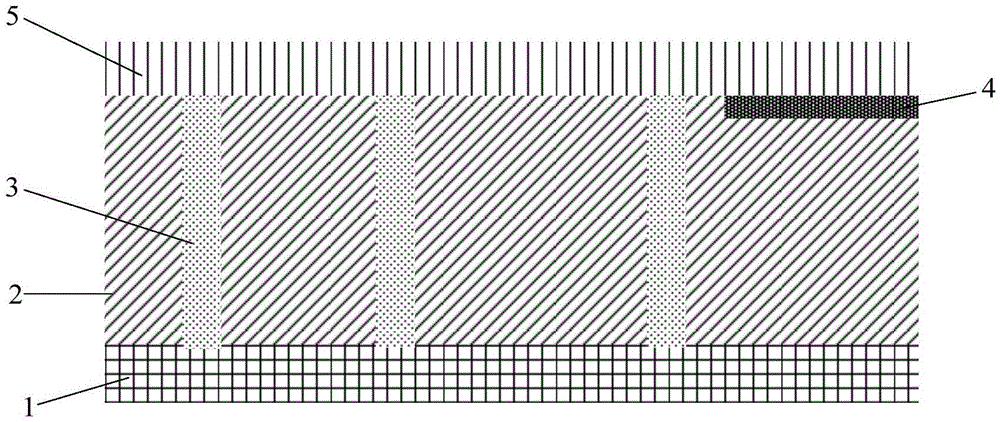

[0030] Such as figure 2 As shown, the voltage division area of the super junction power device provided by the present invention includes a plurality of P pillars, and the density of the P pillars on the side close to the active area in the voltage division area is greater than that on the side close to the stop ring area The P column density; The P column density refers to the number of P columns per unit area of the partial pressure region.

[0031] The super-junction power device of the present invention adopts P-pill...

Embodiment 2

[0043] The present invention also provides a method for a super junction power device, which includes the following steps:

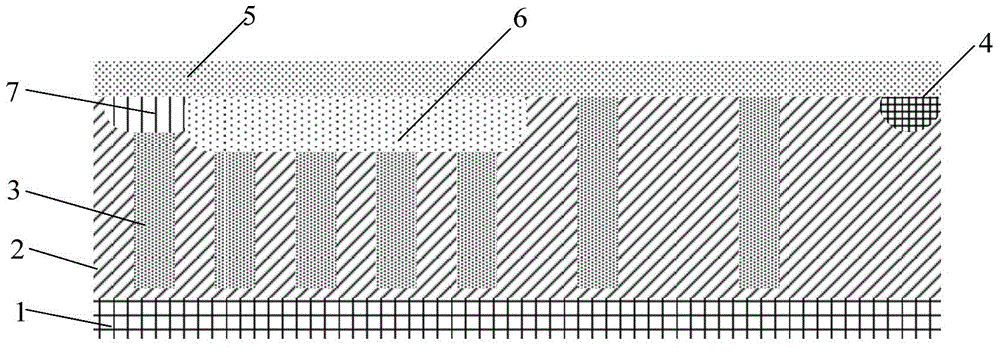

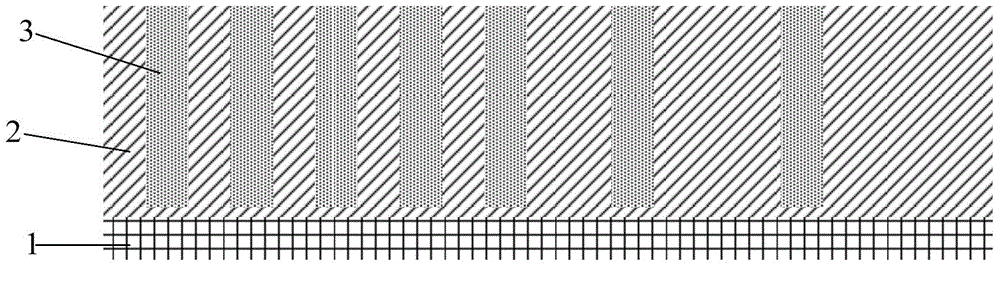

[0044] Step 1, as shown in Figure 3(a), a plurality of P pillars are formed in the partial pressure area on the surface of the silicon wafer. The P-pillar spacing on the side close to the active region in the voltage dividing region is the same, and the P-pillar spacing on the side close to the cut-off region gradually increases from the active region to the cut-off region;

[0045] In this embodiment, the ion concentration of each P column is the same, and the width is also the same. In this embodiment, using P-pillars with different distances in the voltage division region will reduce the surface electric field strength of the power device, thereby increasing the breakdown voltage;

[0046] Step two, as shown in FIG. 3(b), a shallow P-type implanted junction is implanted on the side close to the active region in the partial pressure region, and the shallow P...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More