Multi-channel lvds clock line detection method and system

A line detection and clock technology, used in static indicators, instruments, etc., can solve the problems of abnormal display images and low detection reliability, and achieve the effect of avoiding abnormal images and improving reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

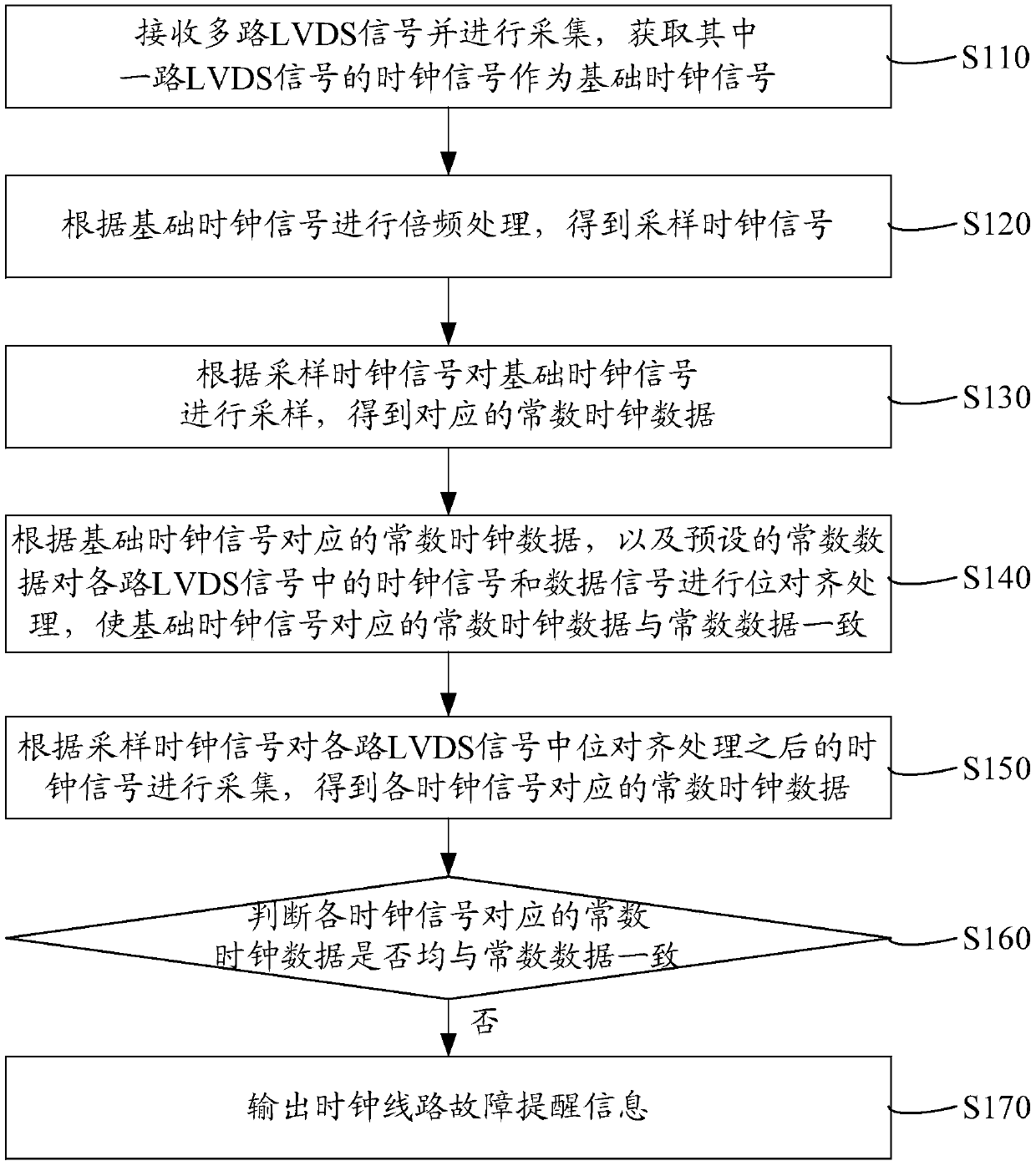

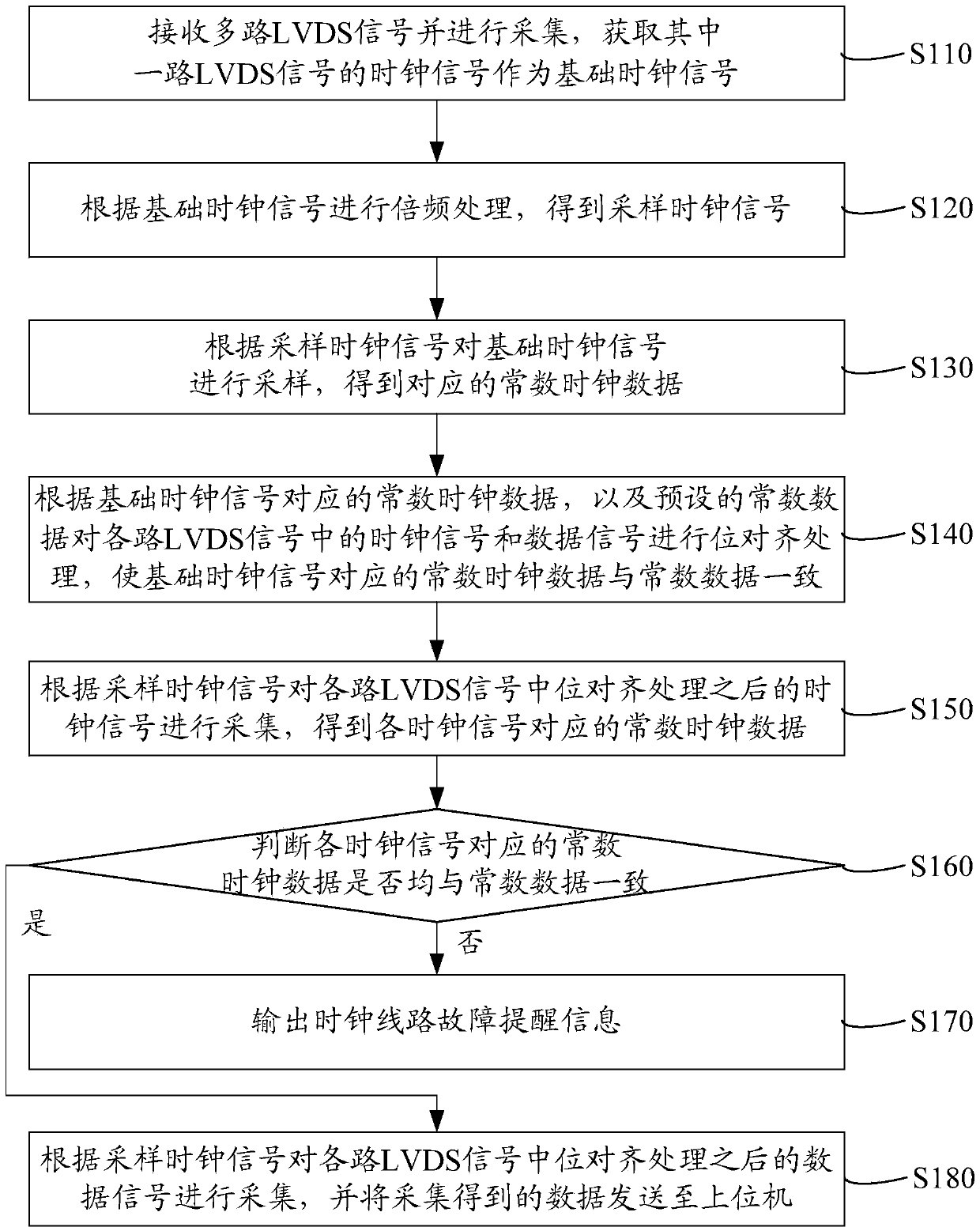

[0027] In one embodiment, a multi-channel LVDS clock line detection method, such as figure 1 shown, including the following steps:

[0028] Step S110: Receive and collect multiple LVDS signals, and acquire a clock signal of one of the LVDS signals as a basic clock signal.

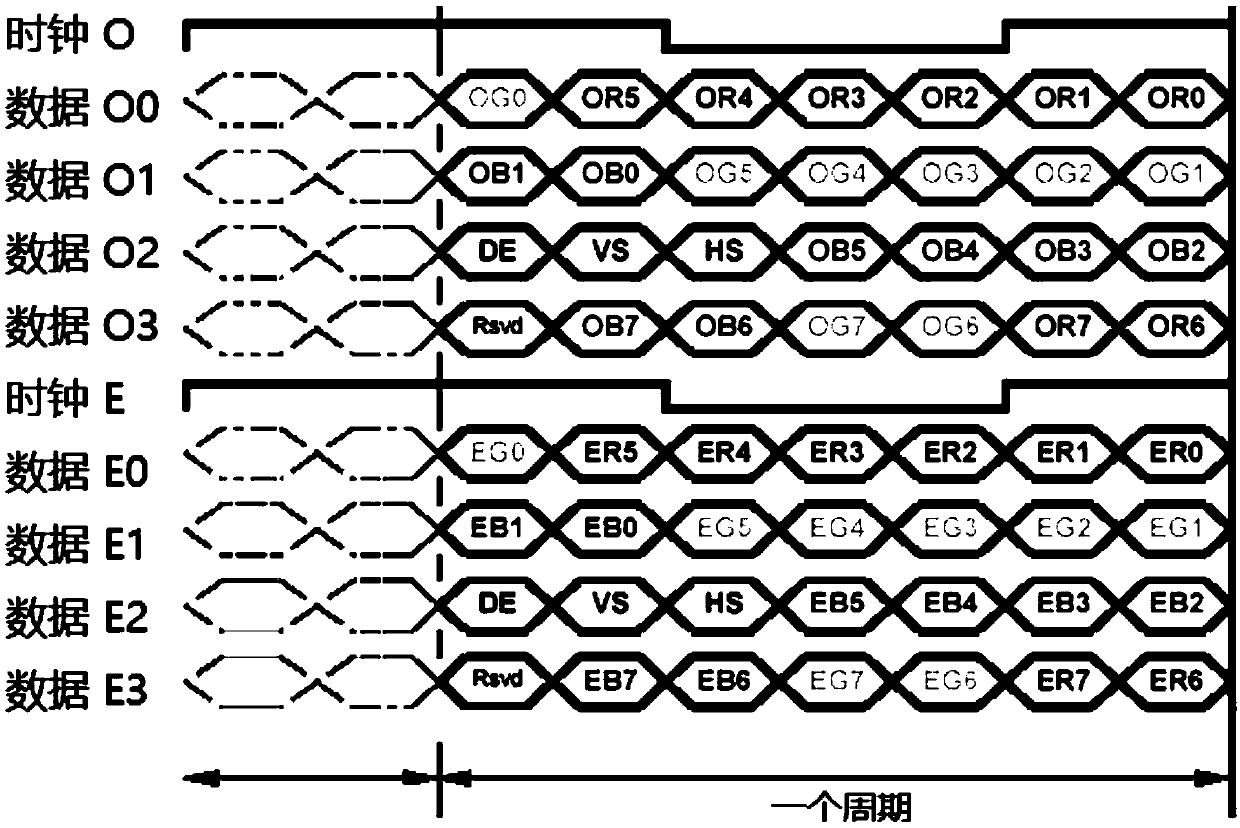

[0029] In the display interface, the LVDS data format is that each pair of data lines has 7 bits of data per clock cycle, and each clock cycle contains data of one pixel point. The red, green, blue signals and control signals of the image are divided into the way that every 7 bits occupy a pair of data lines. A color depth of 6 bits requires 3 pairs of data lines; a color depth of 8 bits requires 4 pairs of data lines; a color depth of 10 bits requires 5 pairs of data lines; a color depth of 12 bits requires 6 pairs of data lines. In order to reduce the frequency of LVDS signals, for the case of high resolution and high refresh rate, LVDS adopts a grouping method, and each LVDS channel has 1 pair of clock...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More