FPGA realization system of LZ lossless compression algorithm based on low delay

A lossless compression and system implementation technology, applied in the field of FPGA implementation system, can solve the problems of not giving full play to the advantages of hardware, small search window, low compression rate, etc., to improve the defect of uncertain output delay, stable output delay, The effect of fast compression

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Below in conjunction with accompanying drawing, the technical content of invention is described in detail:

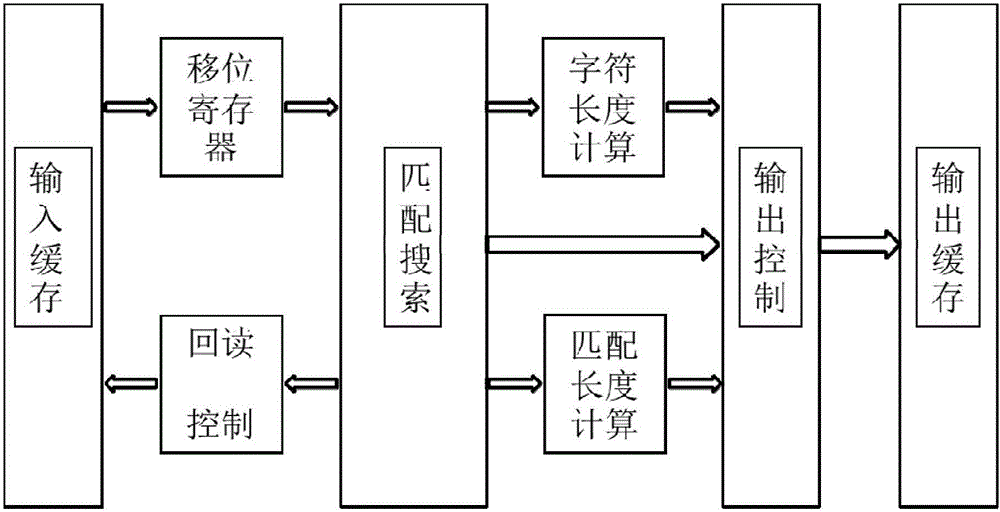

[0041] Such as figure 1As shown, the present invention discloses a FPGA implementation system based on a low-latency LZ lossless compression algorithm, including an input buffer module, an output buffer module, a shift register, a readback control module, a matching search module, a character length calculation module, A matching length calculation module and an output control module; the input buffer module is connected with the shift register and the readback control module respectively and then connected with the matching search module, and the matching search module is respectively connected with the character length calculation module and the matching length calculation module and then connected with the output The control module is connected, and the output control module is connected with the output buffer module; the input buffer module is used for buffer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More