Patents

Literature

32results about How to "Output delay is small" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

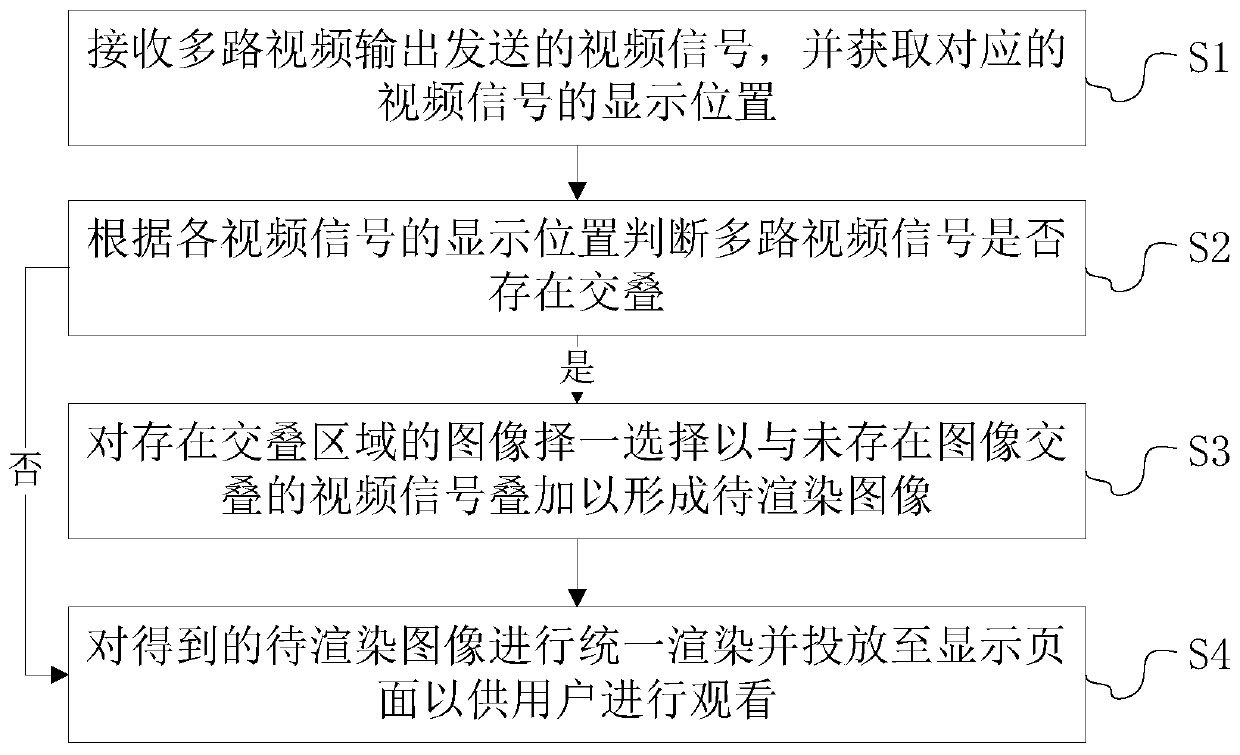

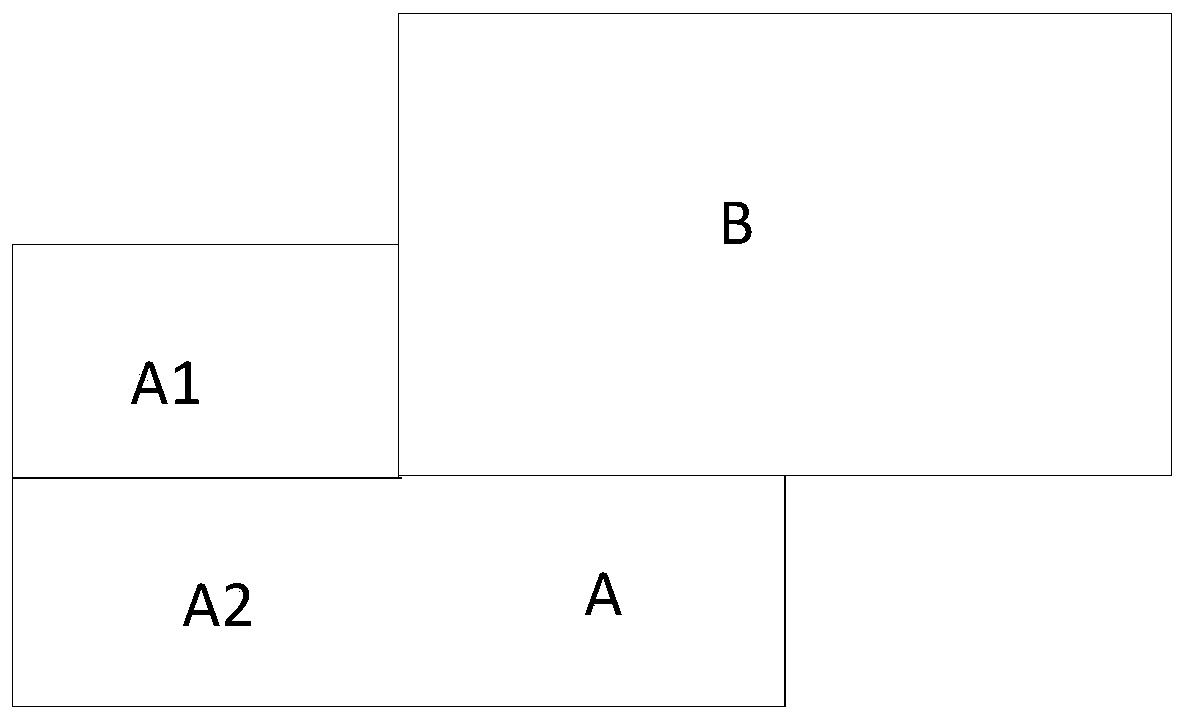

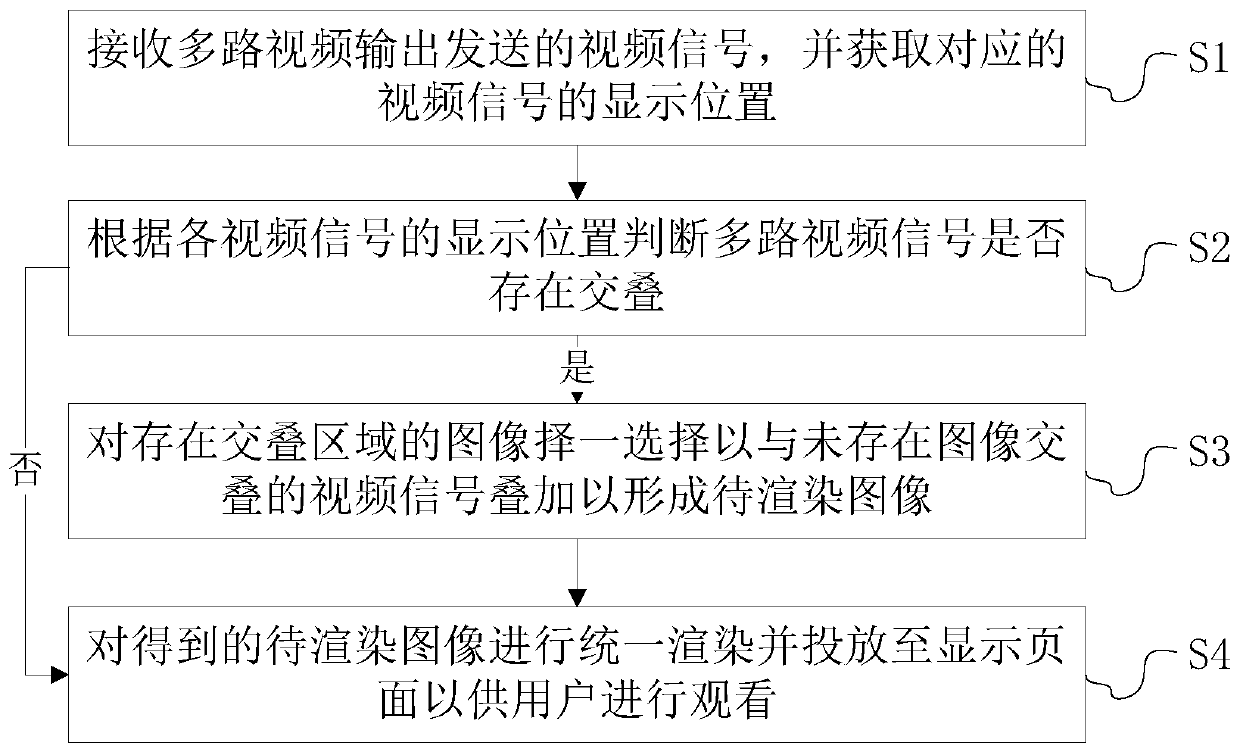

Multi-channel video window overlapping display method, electronic equipment and storage medium

ActiveCN111147770AOutput delay is smallSolve the display exceptionTelevision system detailsColor television detailsComputer graphics (images)Image resolution

The invention discloses a multi-channel video window overlapping display method, which comprises the following steps of: receiving video signals output and sent by multiple channels of videos, and acquiring display positions of the corresponding video signals; judging whether the multiple paths of video signals are overlapped or not according to the display positions of the video signals; selecting one of the images with the overlapping area to be overlapped with the video signal without the overlapping area to form an image to be rendered; and performing unified rendering on the obtained to-be-rendered images and projecting the to-be-rendered images to a display page for a user to watch. The invention further provides electronic equipment and a computer readable storage medium. Accordingto the multi-channel video window overlapping display method disclosed by the invention, the overlapping result can be displayed by combining the overlapped video inputs of the multi-channel display window together and then only performing output rendering once; the method disclosed by the invention has the advantages of higher processing speed and lower video output delay; the method can effectively solve the problem of abnormal display of the overlapping part of a high-resolution video window.

Owner:GUANGZHOU BAOLUN ELECTRONICS CO LTD

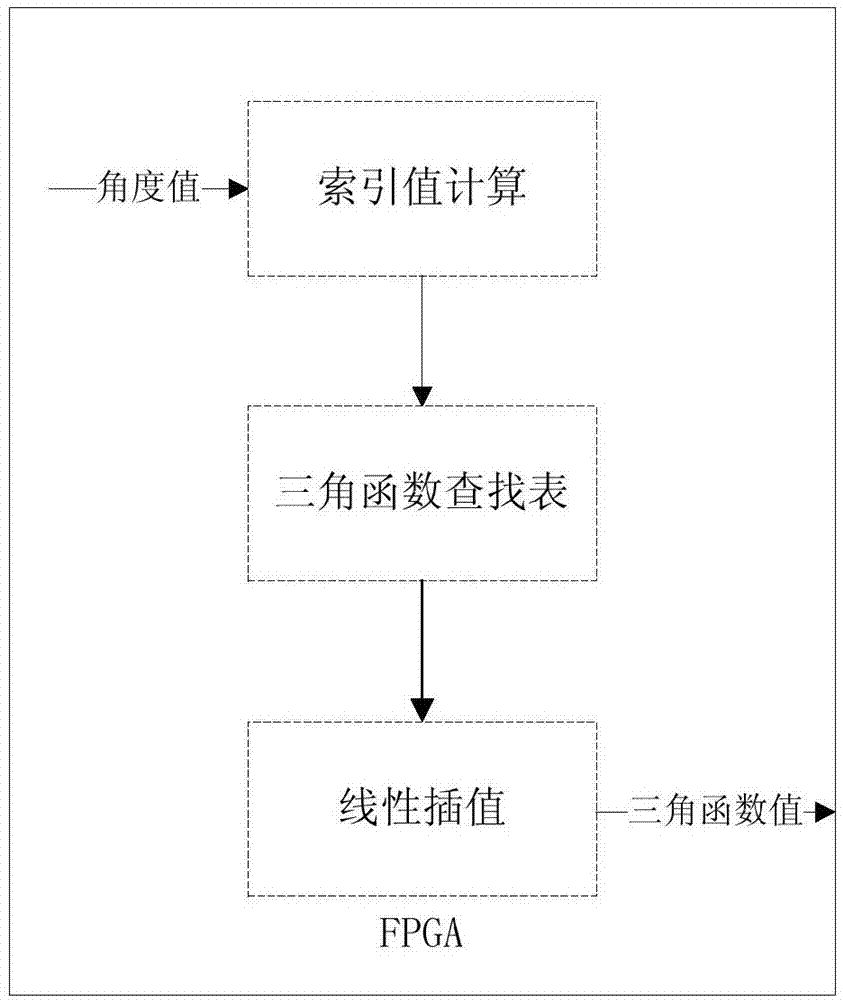

Method for achieving FPGA digital signal processing based on segmented lookup trigonometric function

InactiveCN104765713ASolve the accuracy problemSave storage spaceComplex mathematical operationsDigital signal processingLookup table

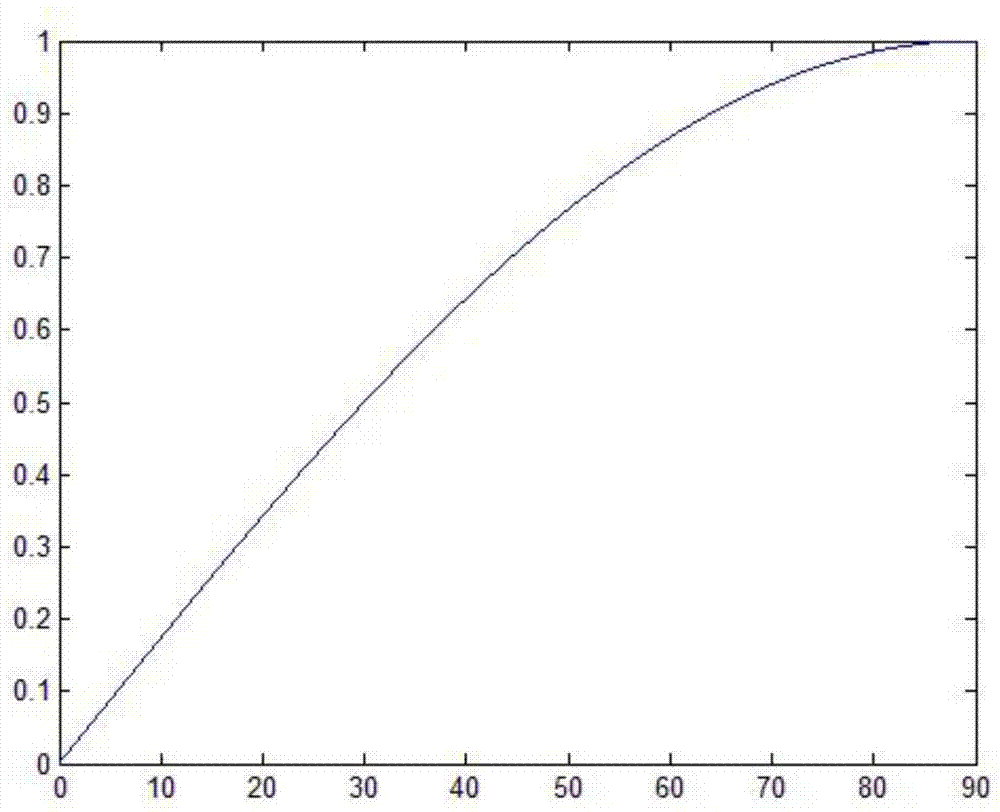

The invention provides a method for achieving FPGA digital signal processing based on a segmented lookup trigonometric function. The method for achieving the FPGA digital signal processing based on the segmented lookup trigonometric function comprises the following steps: dividing FPGA into 3 parts including an index value calculation module, a trigonometric function lookup table, and a linear interpolation module, wherein the trigonometric function lookup table includes correspondences among angles and trigonometric functions and is fixed in ROM storage resources of the FPGA; calculating an index position in the corresponding trigonometric function lookup table by the index value calculation module based on the inputted angle value; applying a linear interpolation to the trigonometric function value obtained from looking up the table by the linear interpolation module for obtaining a trigonometric function calculation value having a higher precision. In the method for achieving the FPGA digital signal processing based on the segmented lookup trigonometric function, the contradiction of calculating the trigonometric function value precision and the lookup table depth by the FPGA is solved by the segmented lookup, thereby saving the limited storage space of the FPGA.

Owner:XI'AN INST OF OPTICS & FINE MECHANICS - CHINESE ACAD OF SCI

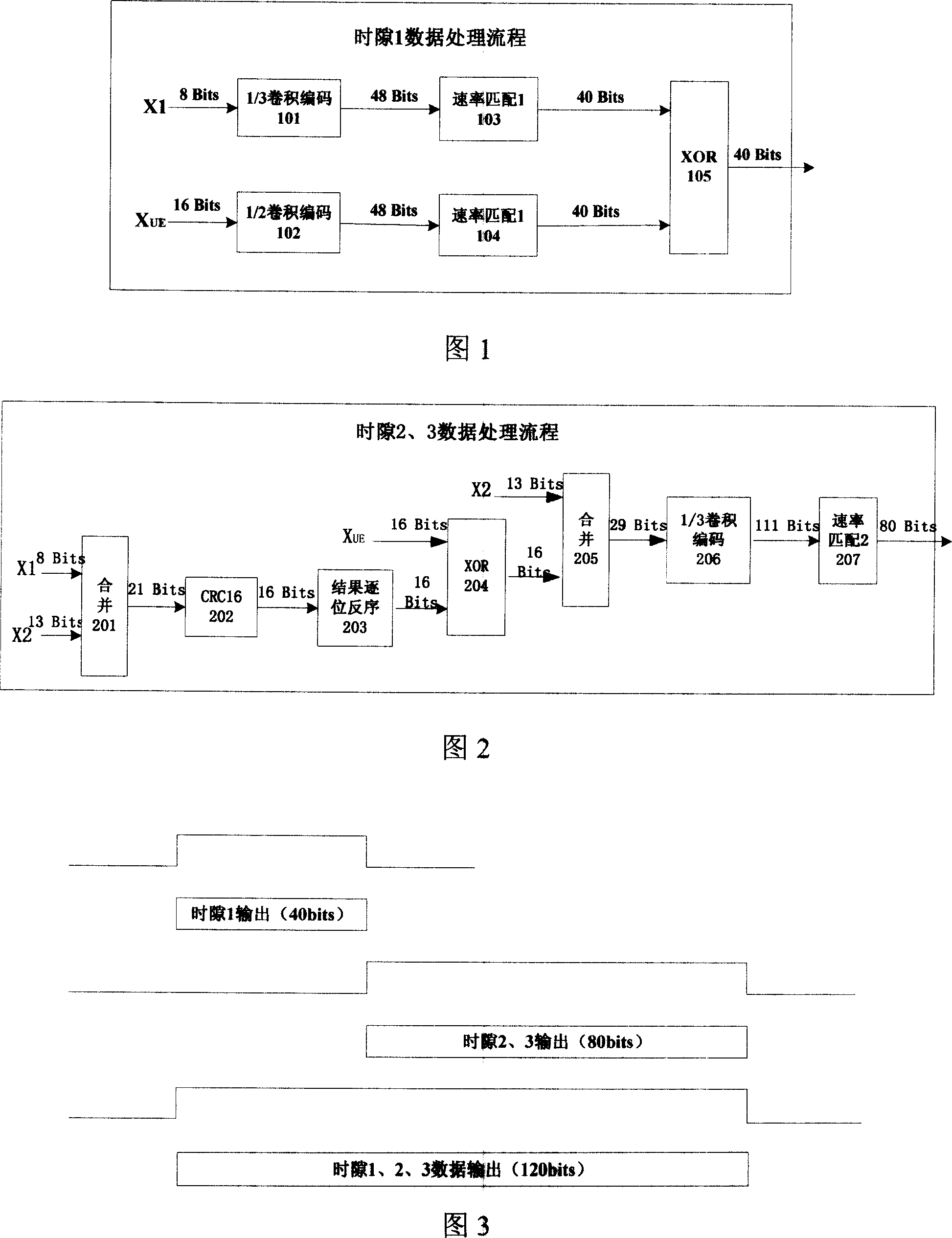

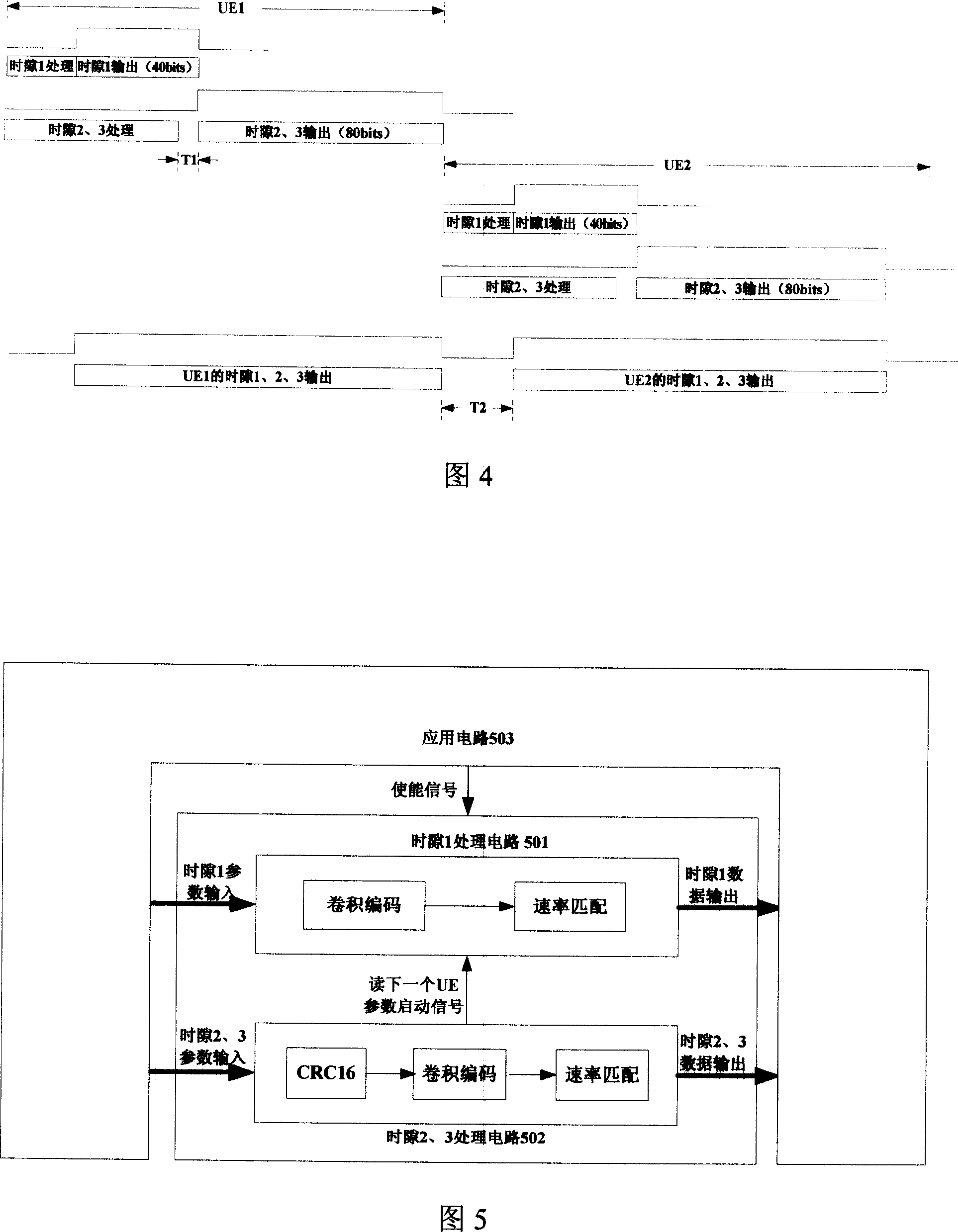

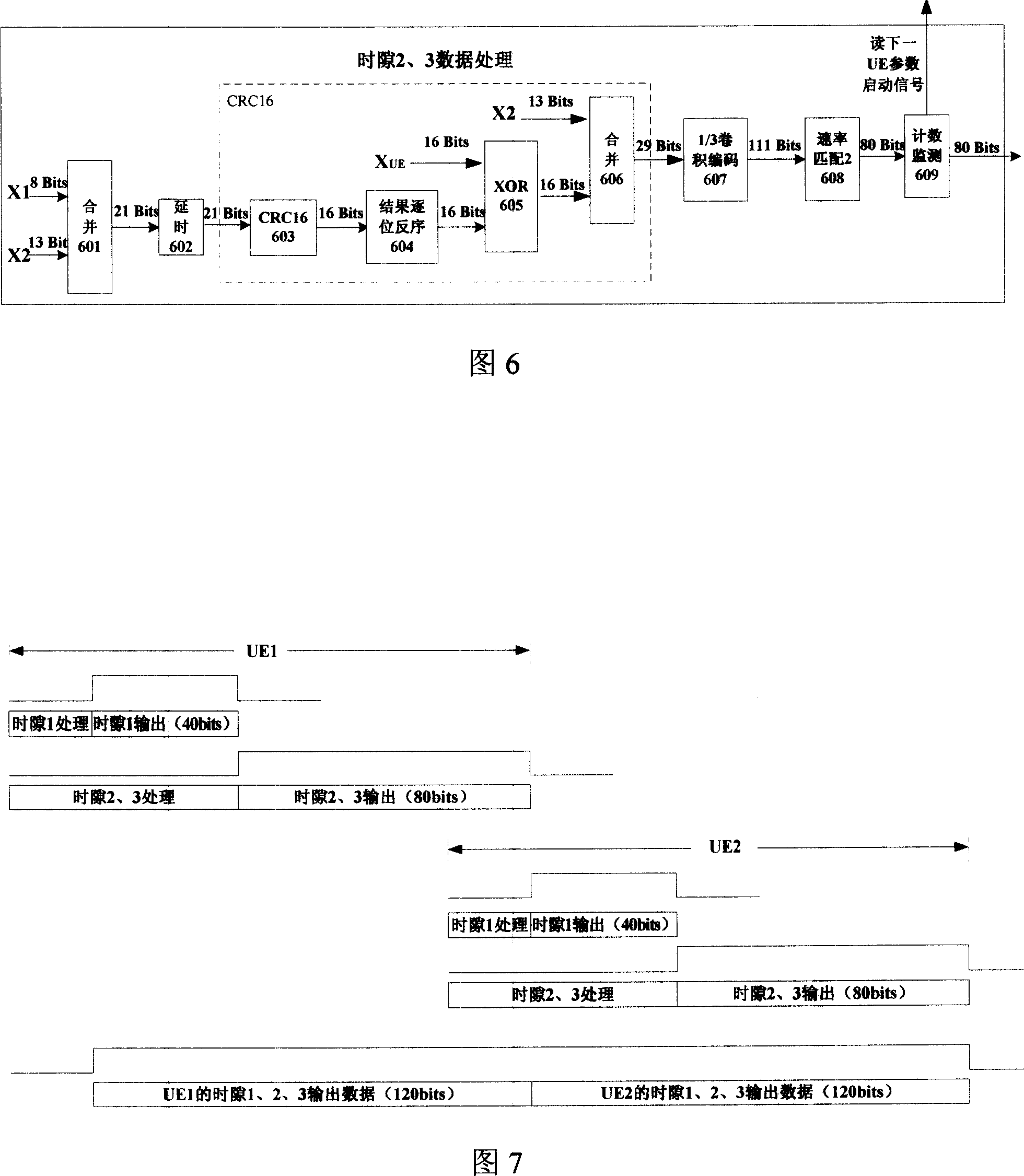

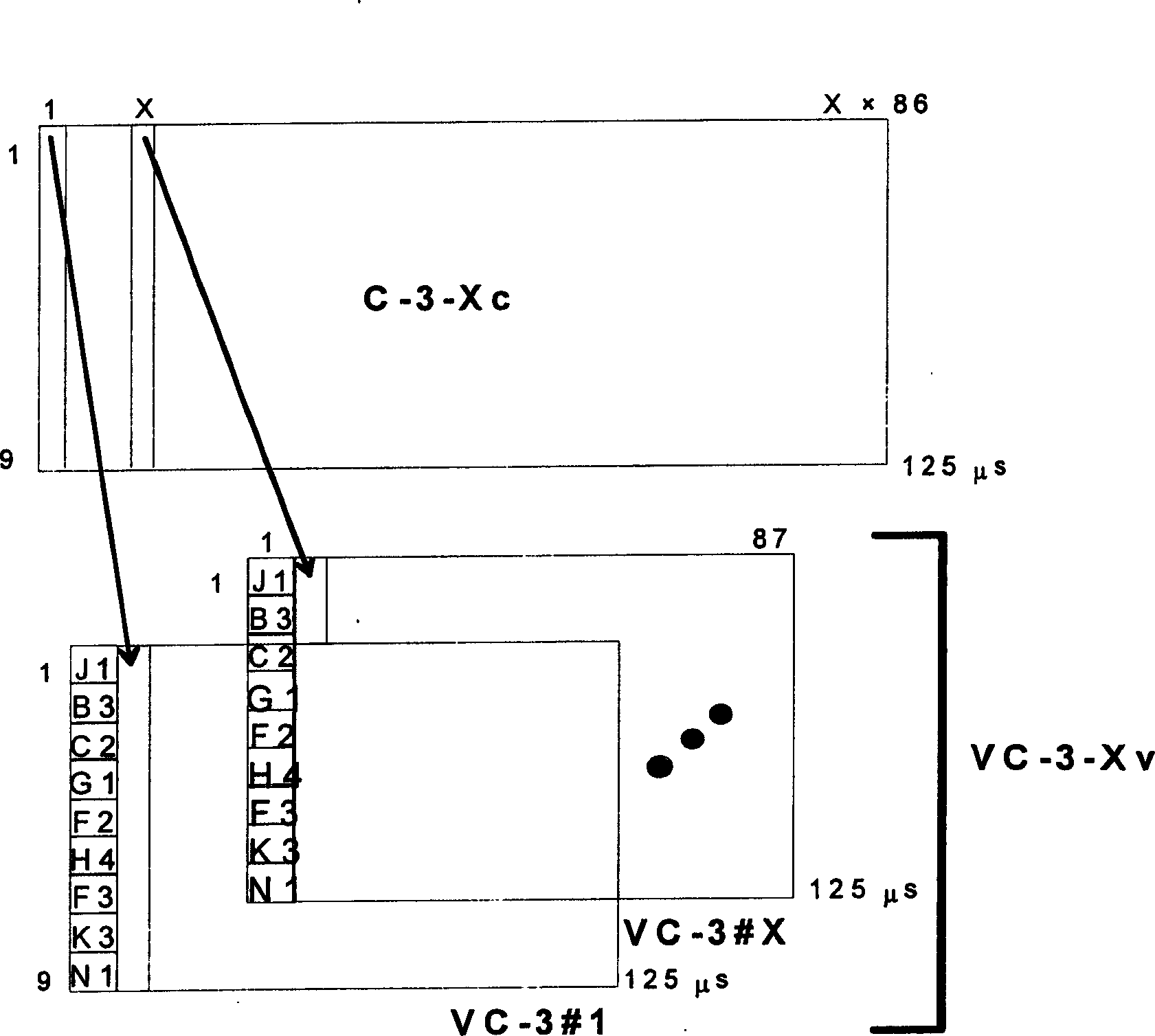

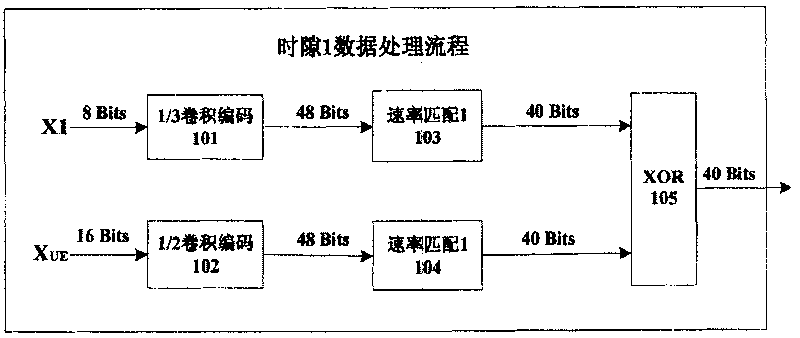

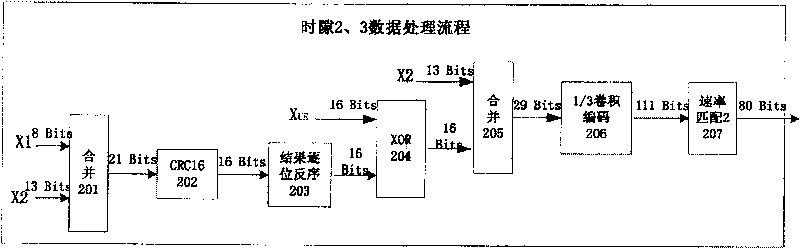

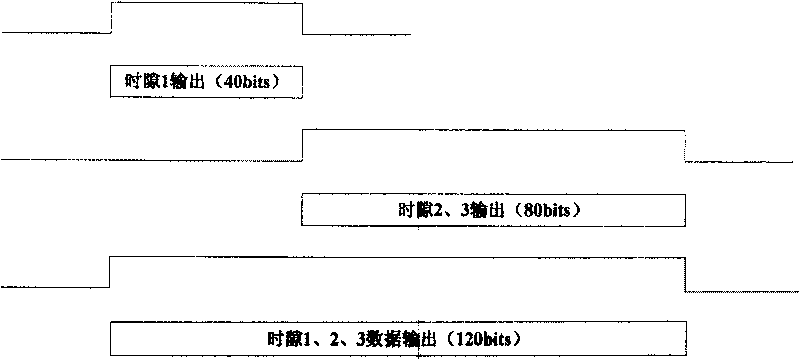

HS-SCCH channel coding device for high speed downlink packet access

ActiveCN101026412AIncrease profitOutput delay is smallError preventionRadio transmission for post communicationTime delaysComputer science

The encoding device for HS-SCCH channel makes the output data compact, reduces time delay, and raises circuit usage. The device includes first process circuit and second process circuit. The first process circuit includes the first convolutional coding unit (CCU), and first rate adaption unit (RAU). The first CCU encodes the input data; and RAU carries out rate matching or XOR process for the data, which are than outputted. Characters are that providing enable signal for the first process circuit to read next set of input data, the second process circuit includes following units: connected in sequence CRC16 circuit unit, second CCU, second RAU, counter monitoring unit, and time delay compensation unit located at one or several positions: in front of CRC16 circuit unit, between CRC16 circuit unit and second CCU, and between second CCU and second RAU.

Owner:SANECHIPS TECH CO LTD

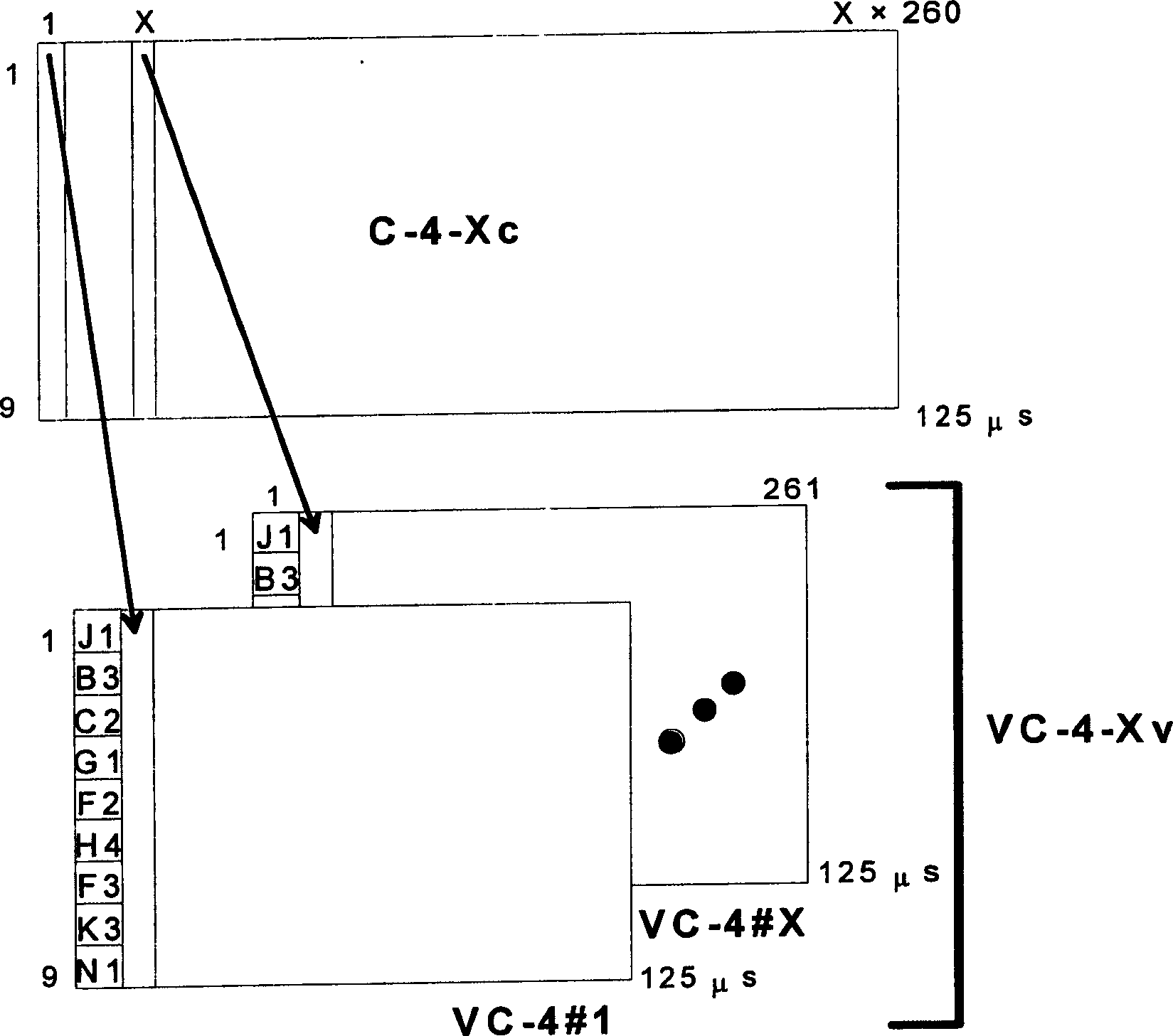

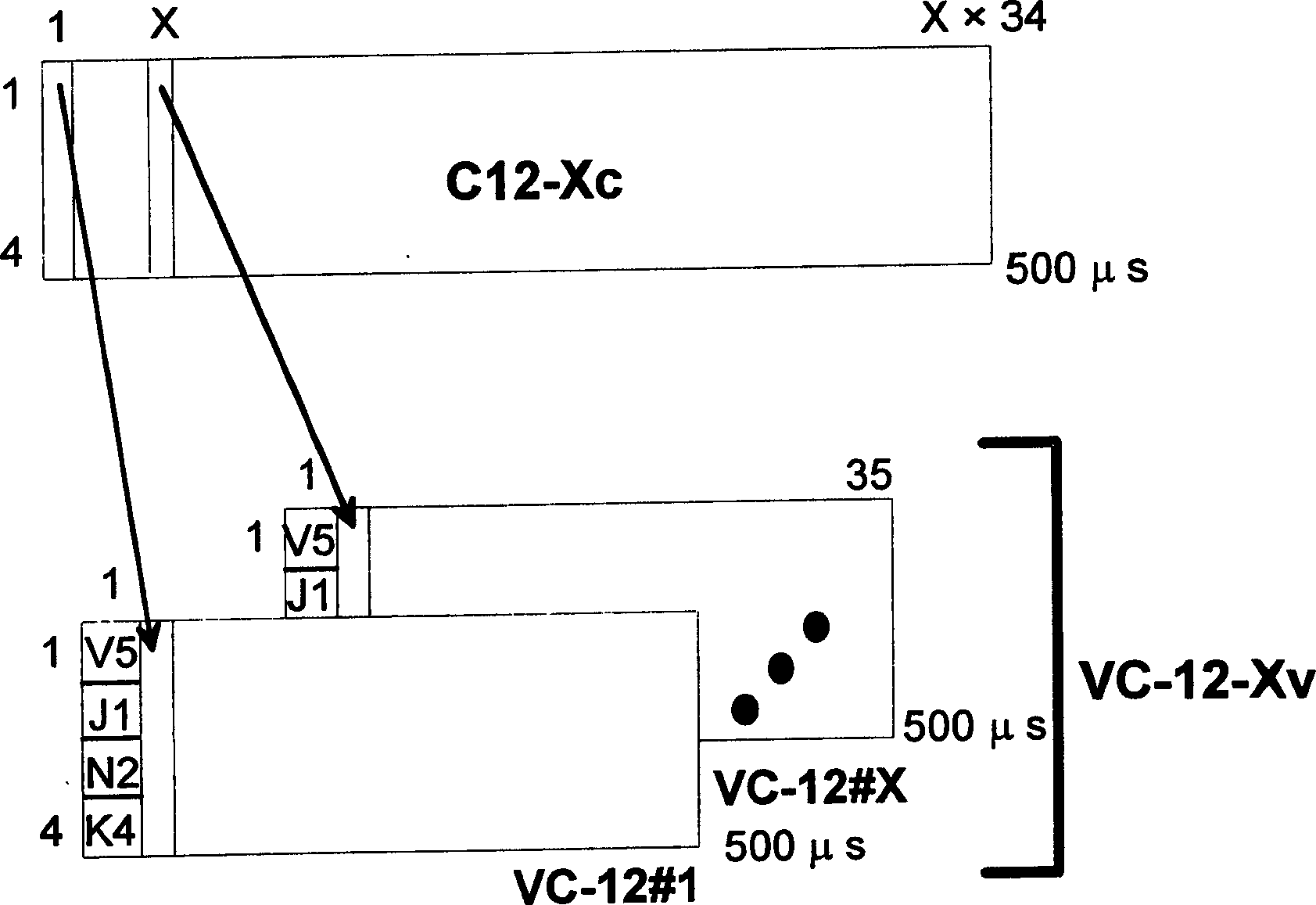

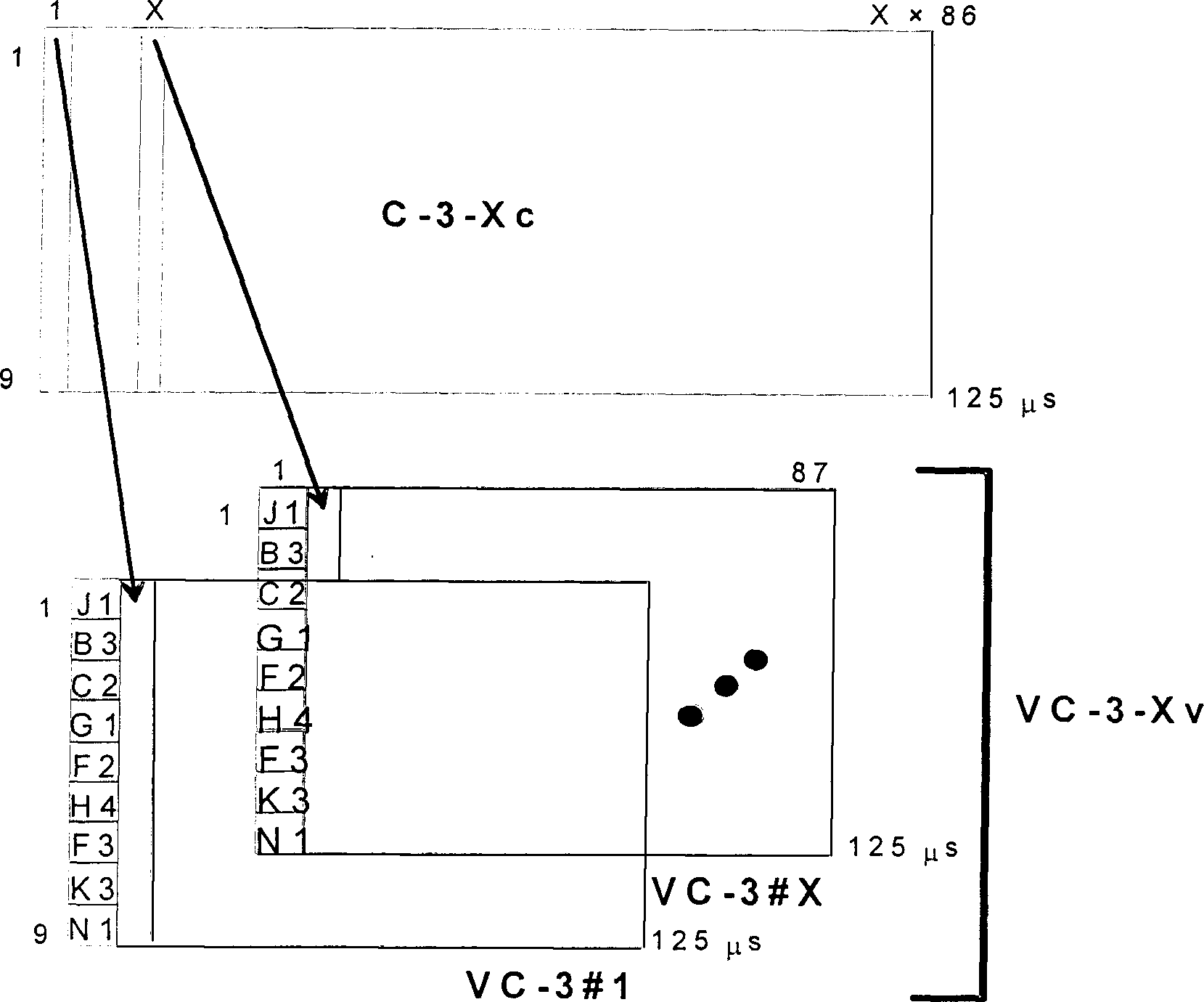

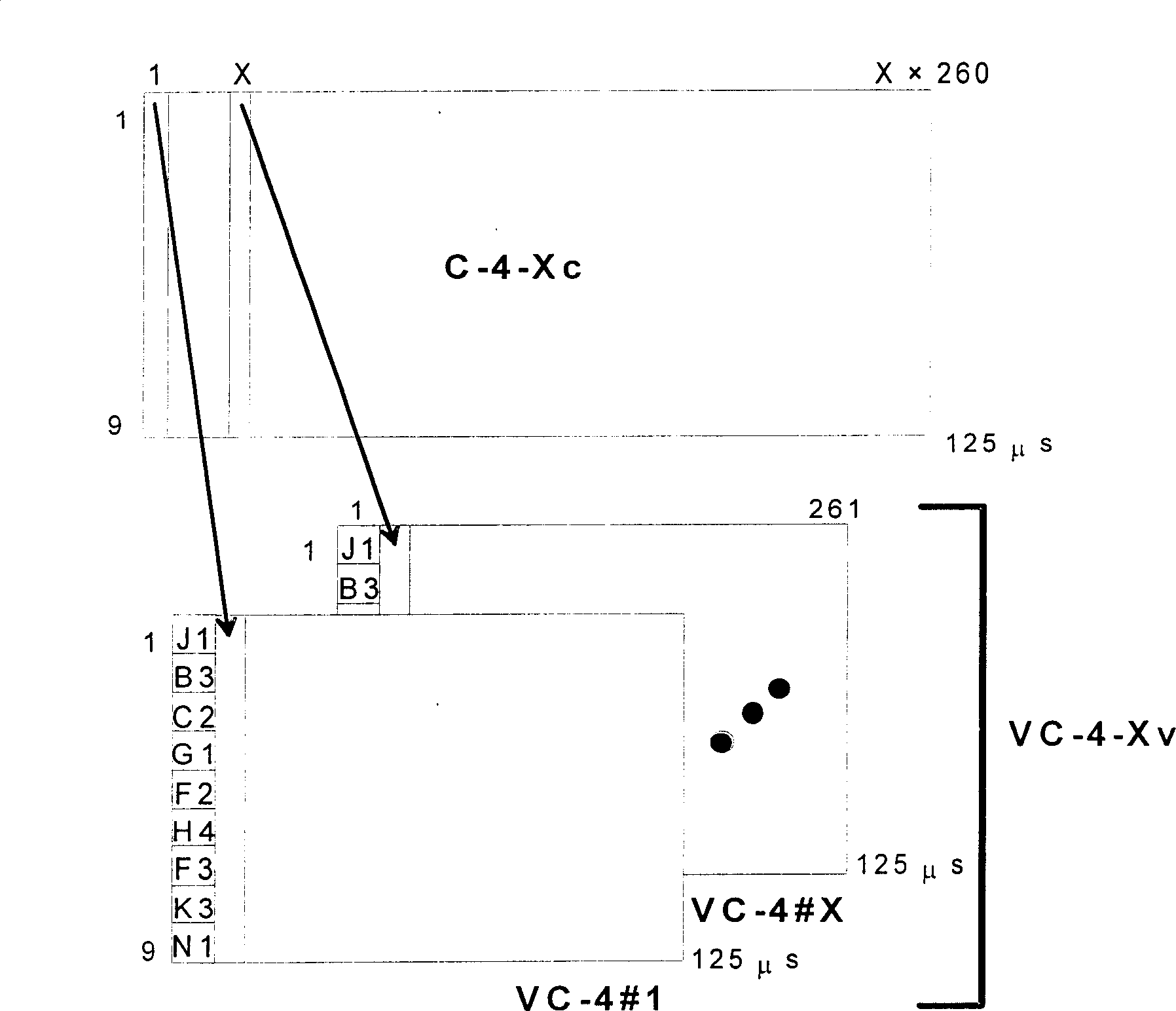

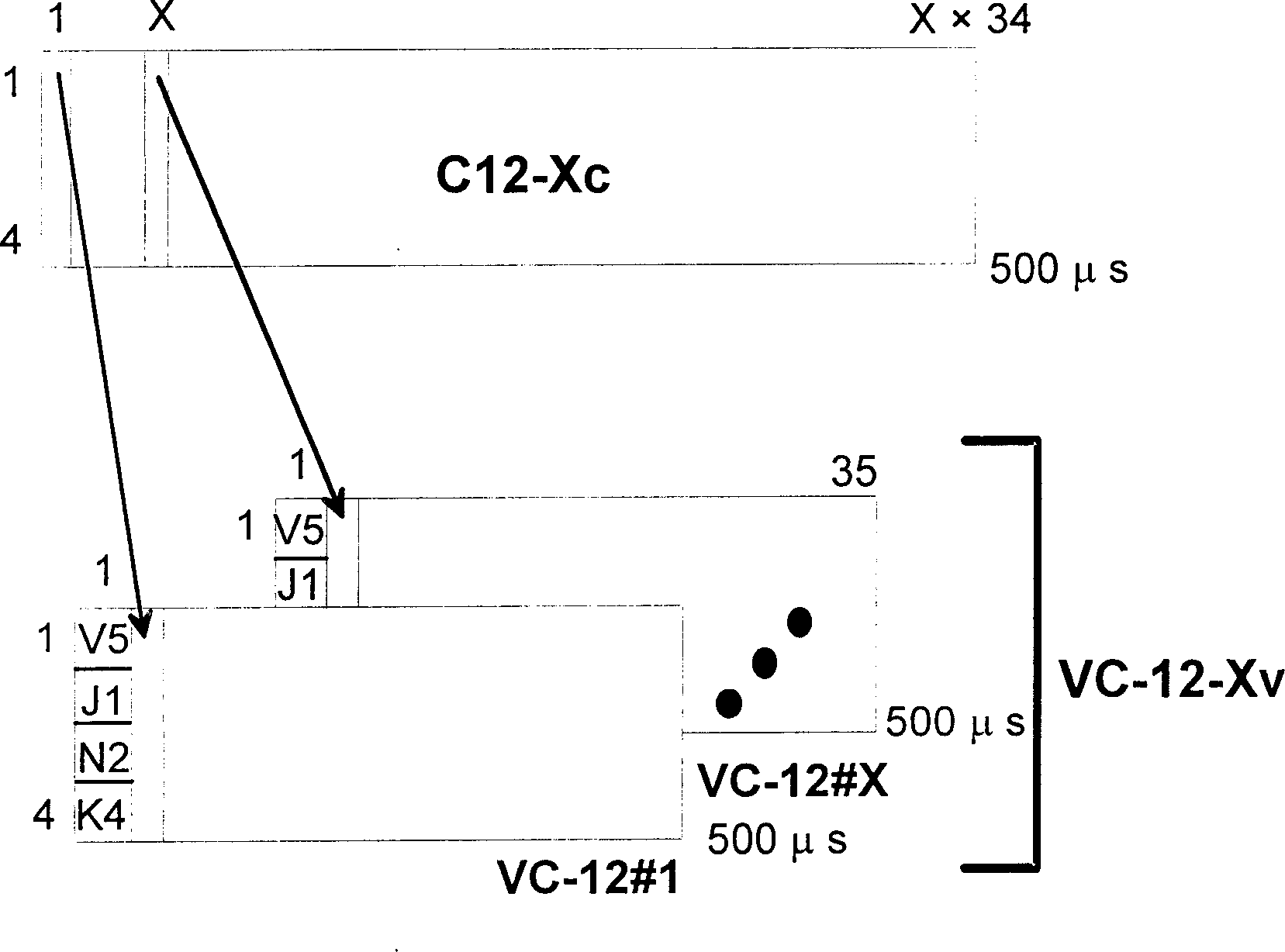

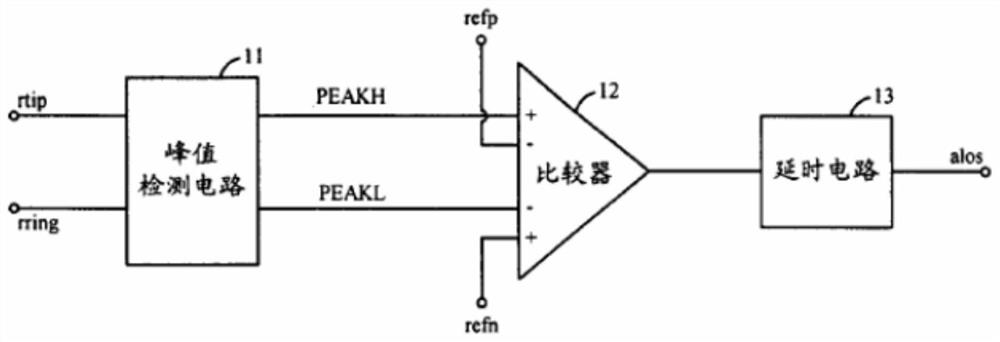

Virtual cascade time delay compensation restoring apparatus

InactiveCN1549533AOutput delay is smallHigh working reliabilityData switching detailsTime-division multiplexTime delaysSelf adaptive

The device consists of cascade multiframe detection circuit for carry on sequence number locking detection, cascade sequence automatic regulation circuit for regulating reservoir sequence based on sequence number of each different reservior in cascade set to make it be in accordance with its sequence at transmission end, buffer zone for making zone as per sequence number of reservior and cascade multiframe, write control circuit for writing content in sequenced reservior to relevant buffer zone, read control repositioning and adaptive circuit for regulating frequency and plase of reservoir and read control circuit for reading out data from buffer zone to finalize restoration of cascade as per command of abovesaid circuit.

Owner:GLOBAL INNOVATION AGGREGATORS LLC

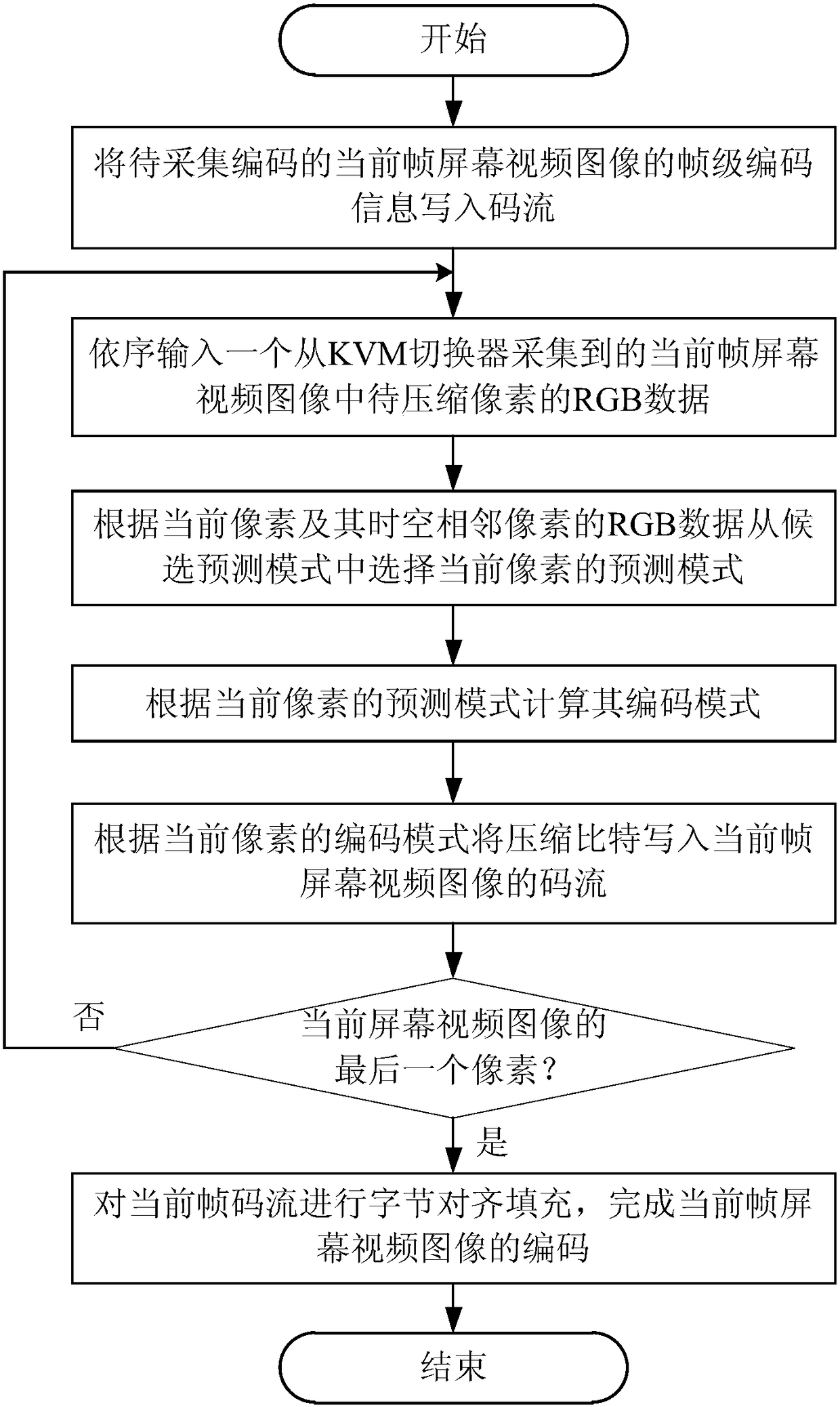

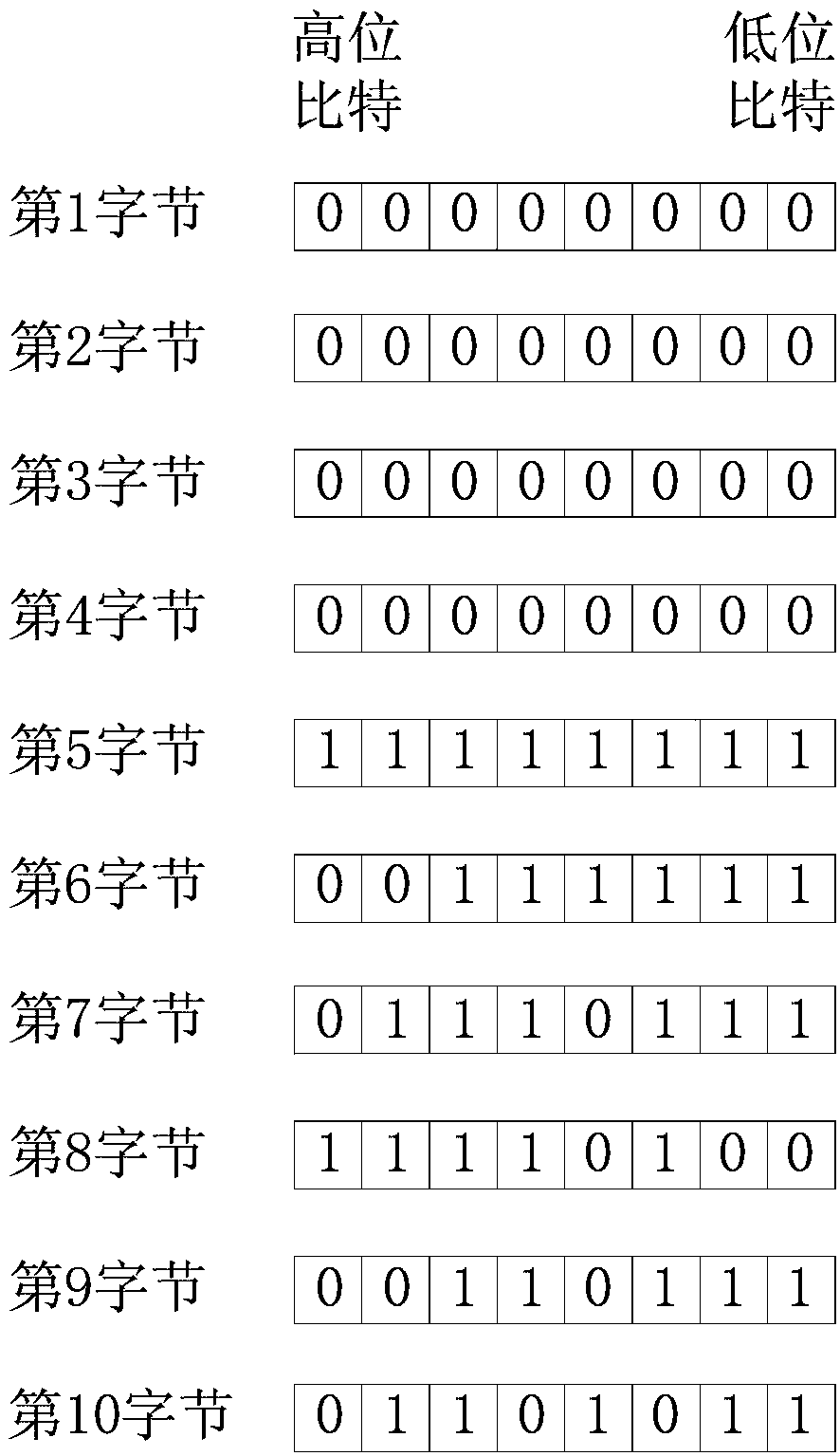

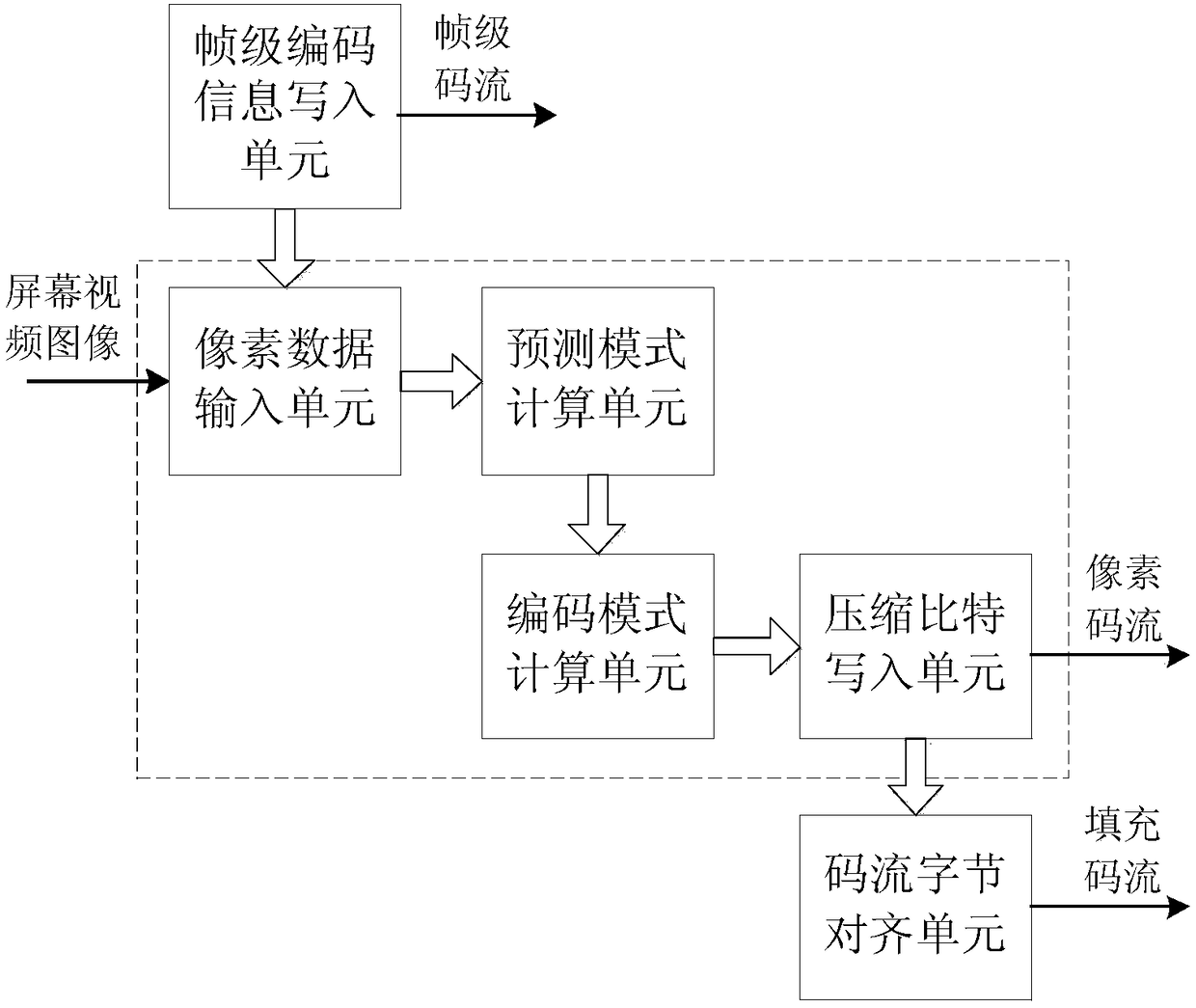

Lossless video compression method and system for digital KVM switcher having low delay and low complexity

ActiveCN106028029ALower latencyReduce computational complexityDigital video signal modificationStreaming dataComputation complexity

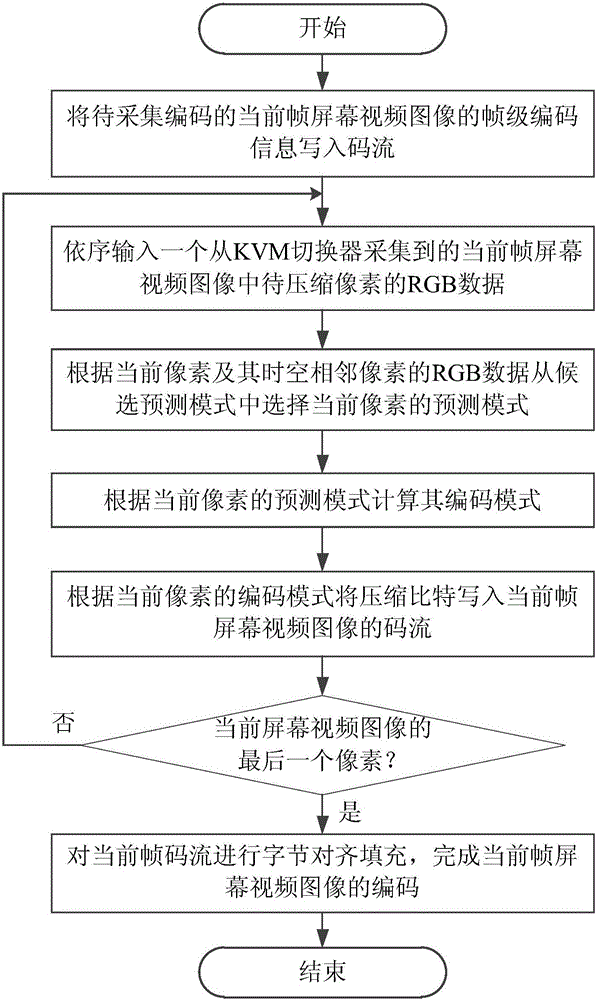

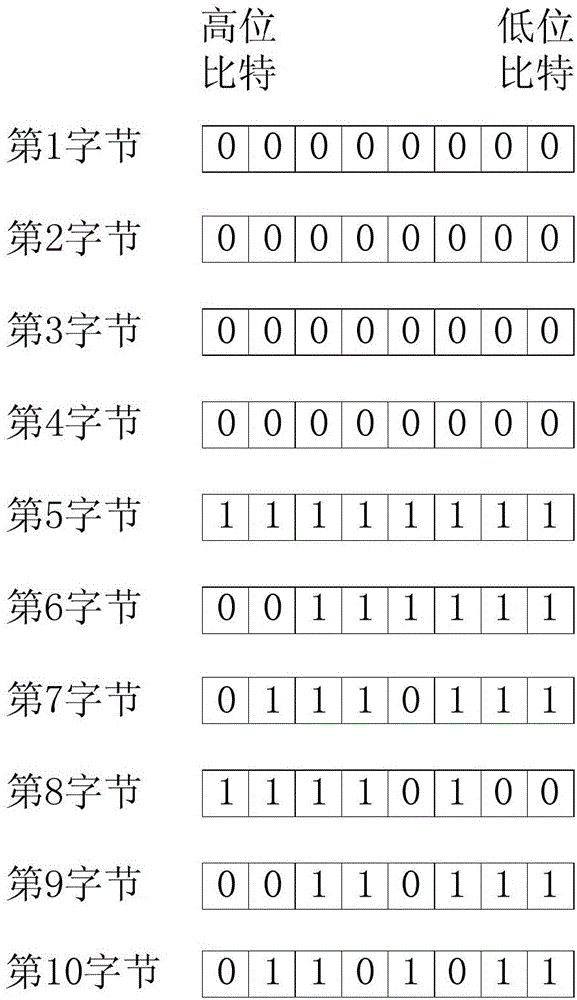

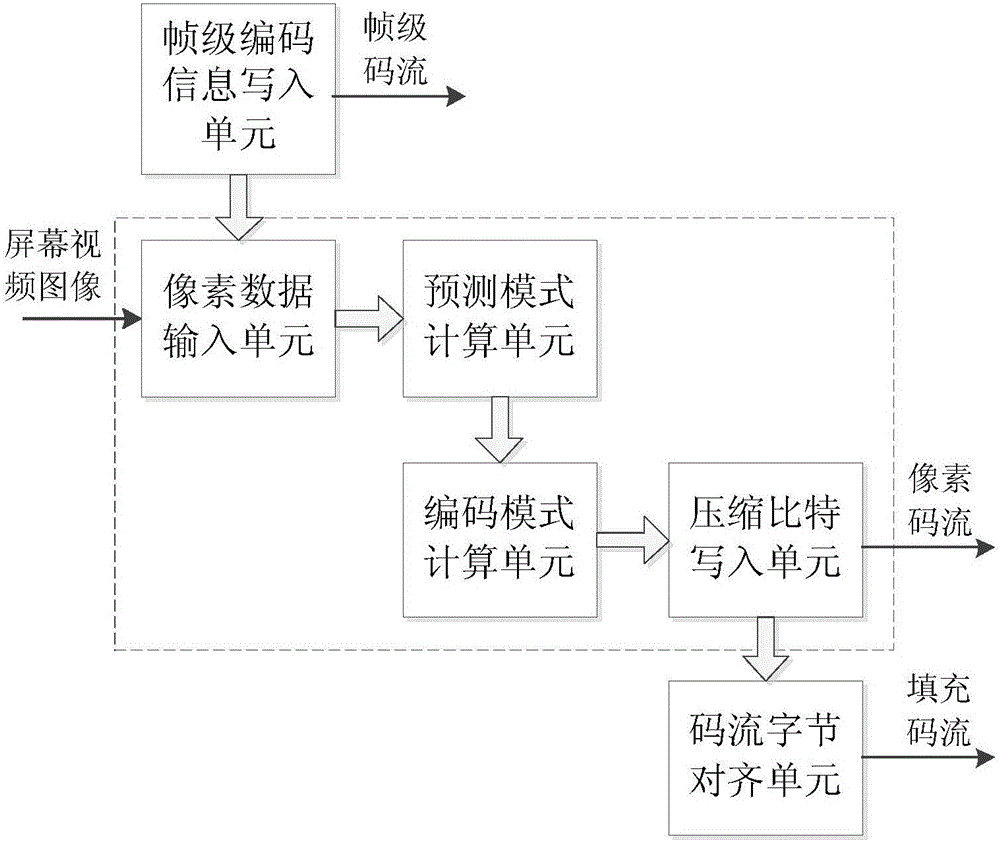

The invention discloses a lossless video compression method and system for a digital KVM switcher having low delay and low complexity. The lossless video compression method comprises the following steps of: (1), writing frame-level coding information of a screen video image in a code stream; (2), sequentially inputting RGB data of pixels to be compressed in the screen video image; (3), calculating the prediction mode of the current pixels according to the spatio-temporal correlation; (4), calculating the coding mode of the current pixels according to the prediction mode of the current pixels; (5), writing a compression bit in the code stream according to the coding mode of the current pixels; (6), repeating the steps (2)-(5), such that coding of all the pixels in the screen video image of the current frame is completed; and (7), performing byte alignment filling of the code stream of the current frame, such that coding of the screen video image of the current frame is completed. The method disclosed by the invention is applied to compression of the screen video image of the digital KVM switcher; the compression processing delay and the code stream data volume of the screen video image can be effectively reduced under the limited calculation complexity; and simultaneously, lossless video quality can be kept.

Owner:杭州比特瑞旺电脑有限公司

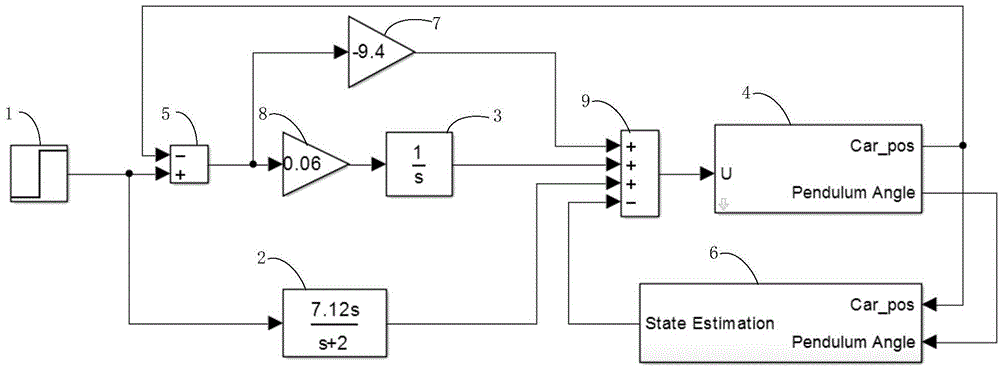

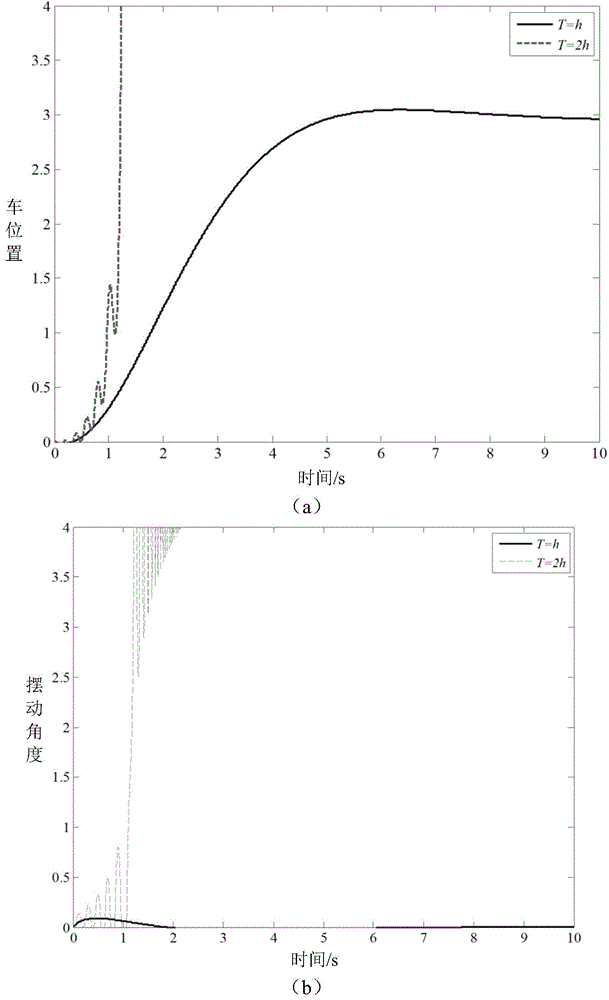

Distributed simulation method for continuous control system in unit operation

ActiveCN104570760ABounded errorConsistent stability characteristicsSimulator controlControl systemUnit operation

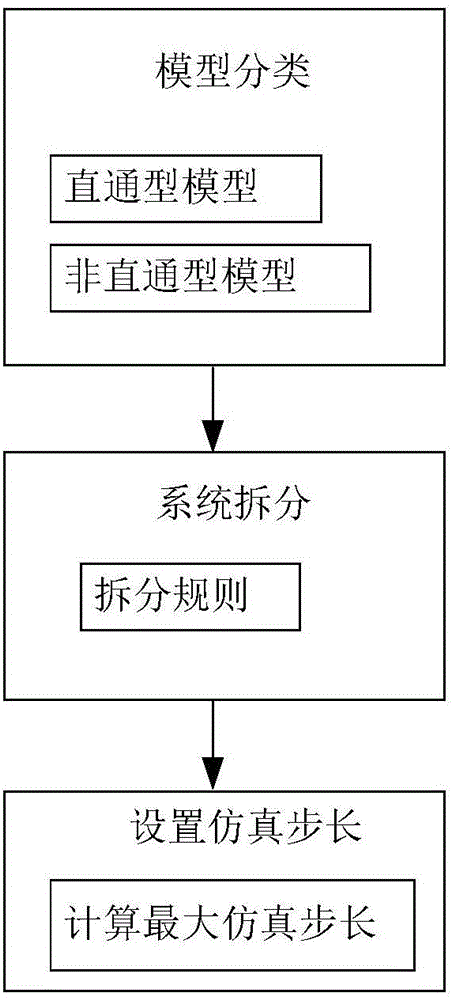

The invention discloses a distributed simulation method for a continuous control system in unit operation, and belongs to the technical field of computer simulation. The method comprises the following steps: firstly, dividing sub-models forming an initial system into two types namely straight-through models and non-straight-through models; secondly, splitting the initial system and deploying each split part on a separate simulation node to run to form a distributed simulation structure, wherein the straight-through model is prevented from being deployed on the separate simulation node during the splitting; finally, setting a simulation period in the distributed environment according to a calculated maximum simulation period. According to the method, the initial system is not required to be modified; data delay generated when the continuous control system in unit operation is converted into one in distributed operation due to the characteristics of parallel computation is reduced by the first two steps; the maximum simulation period is determined to enable the converted distributive system to keep the stability characteristic of the initial system; the data exchange frequency among all distributed simulation nodes is reduced to the greatest extent.

Owner:北京创奇视界科技有限公司

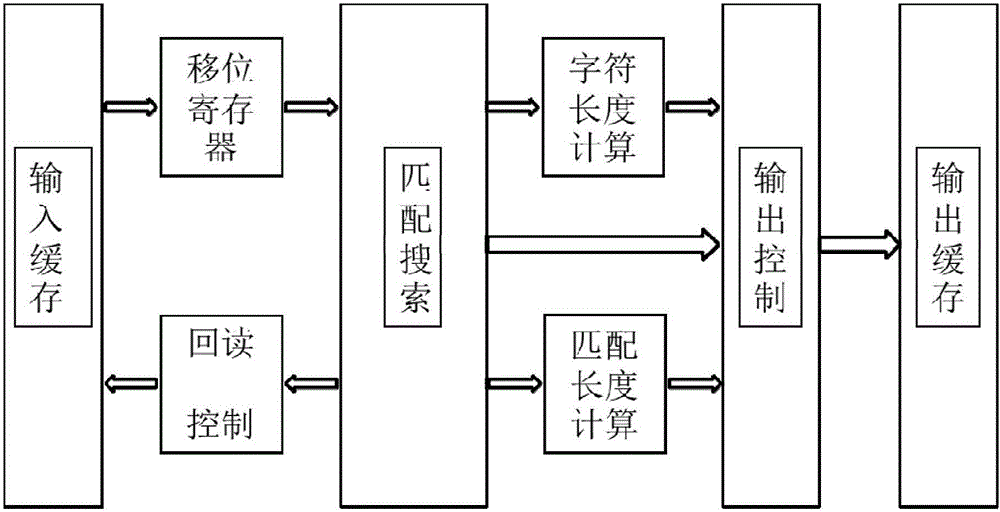

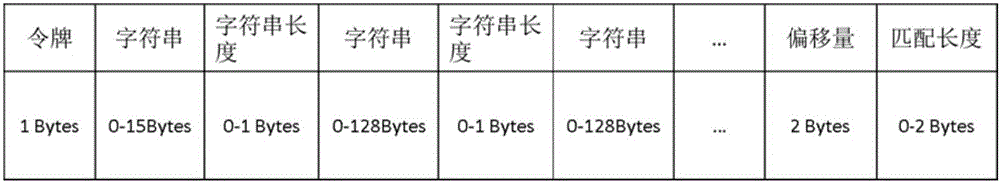

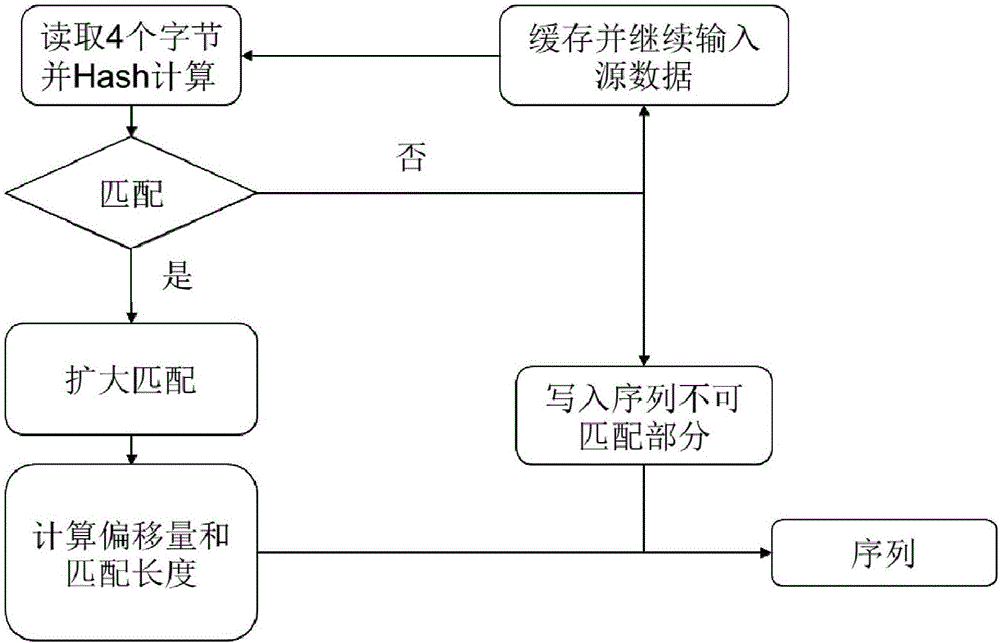

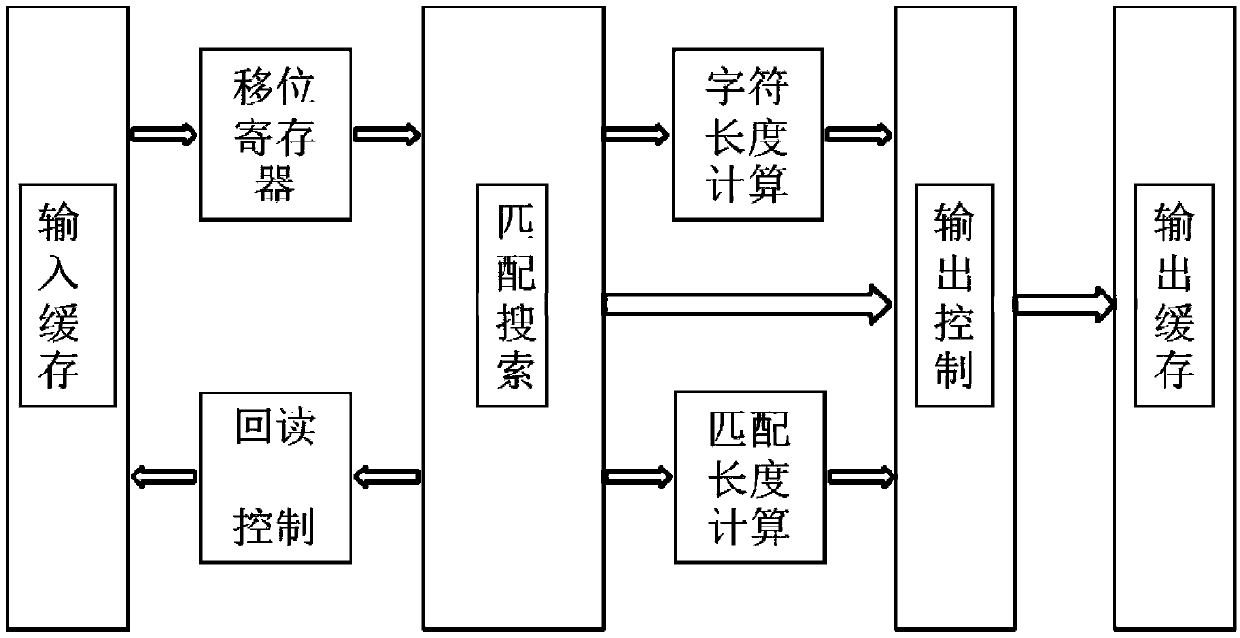

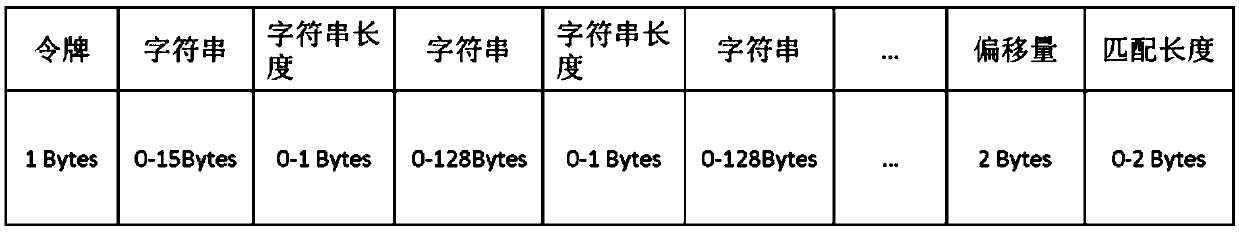

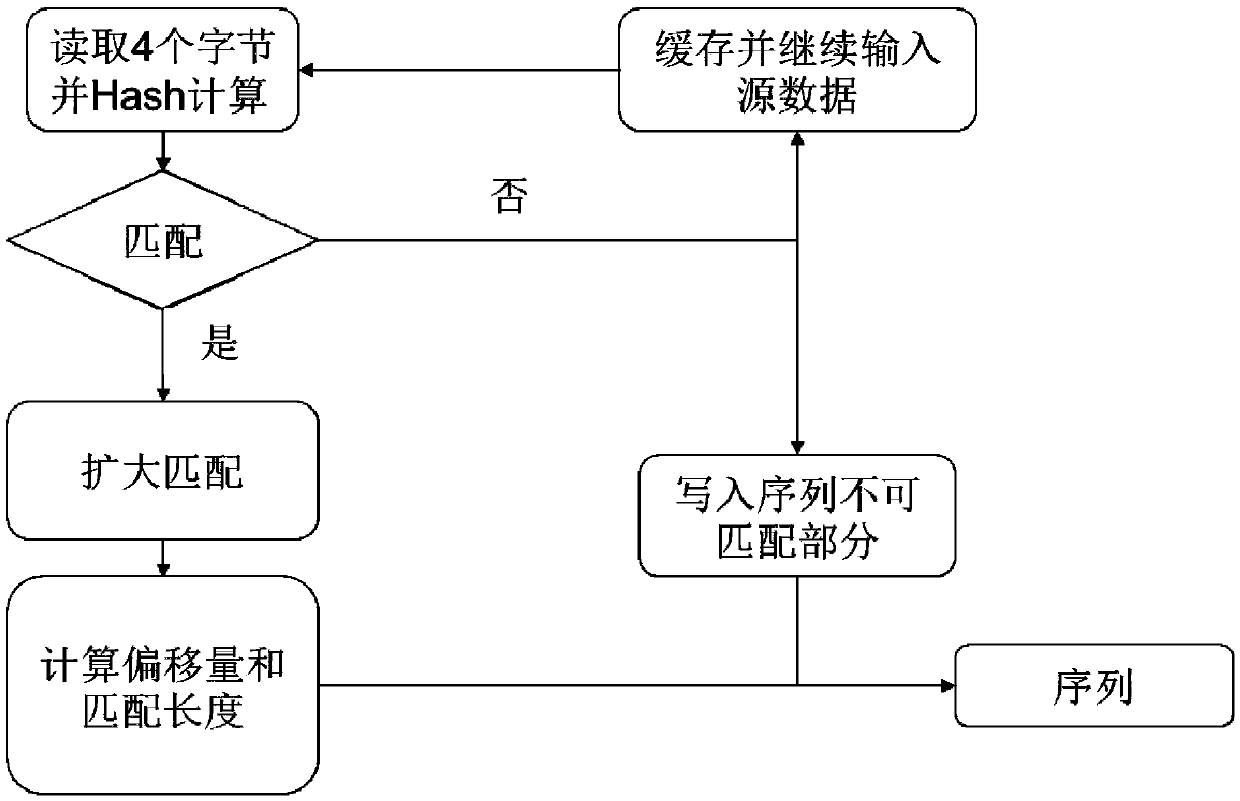

FPGA realization system of LZ lossless compression algorithm based on low delay

ActiveCN106385260AQuick compressionImprove the defect that the output delay is uncertainCode conversionShift registerHash function

The invention discloses an FPGA realization system of LZ lossless compression algorithm based on a low delay. The system comprises an input cache module, an output cache module, a shift register, a read-back control module, a matching search module, a character length calculation module, a matched length calculation module, and an output control module. The input cache module is used for caching input source data and addressing. The output cache module is used for caching output compressed data. The shift register is used for converting the input source data into 4-bit data needed by hash function calculation through shift. The read-back control module is used for carrying out read-back to obtain source data matched with a search need. The matching search module is used for carrying out matching searching of source data word-by-word hash calculation. The character length calculation module is used for calculating the length of a character which can be not matched in a compressed sequence. The matched length calculation module is used for calculating the length of the matched character in the compressed sequence.

Owner:中电莱斯信息系统有限公司

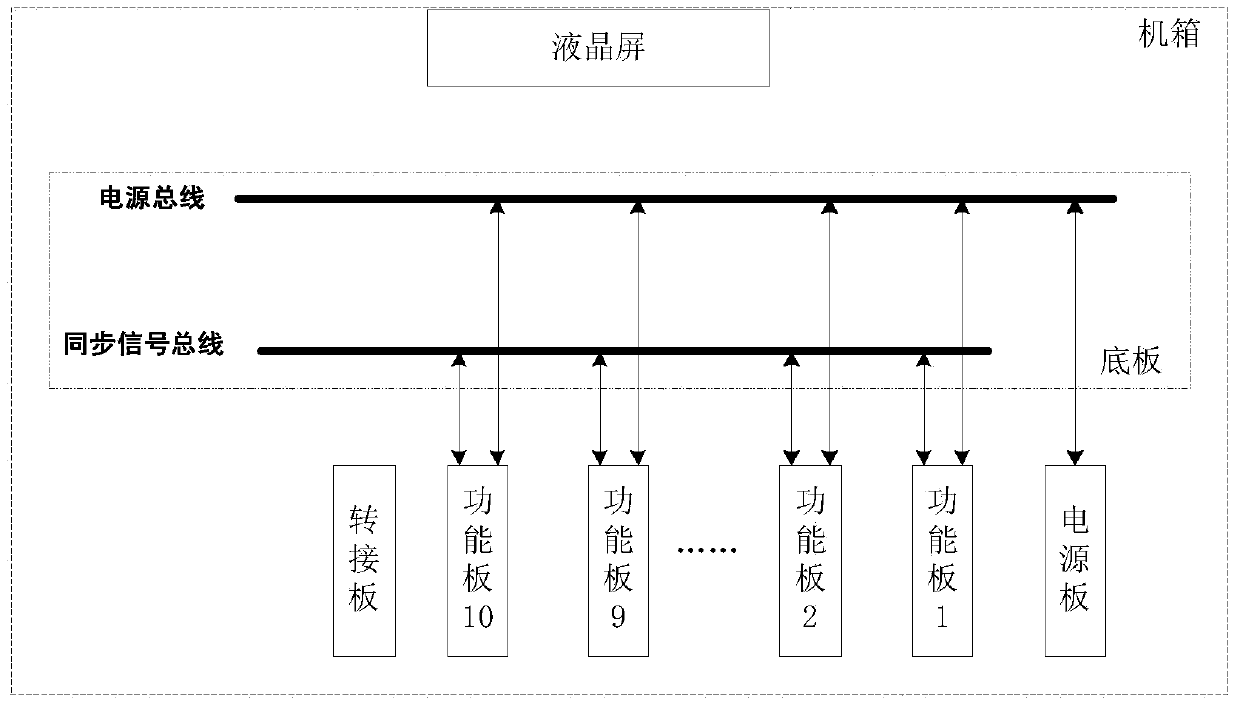

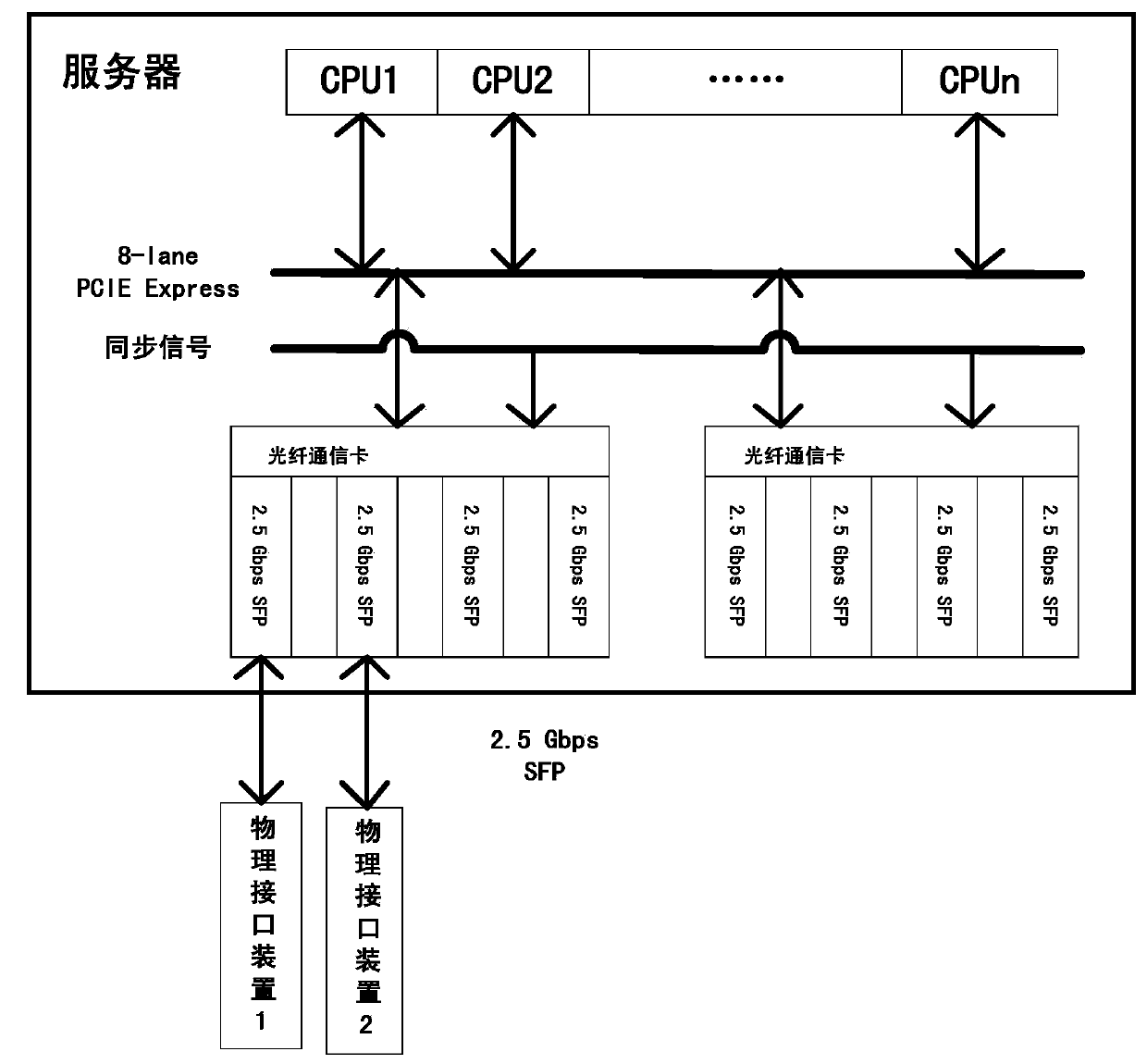

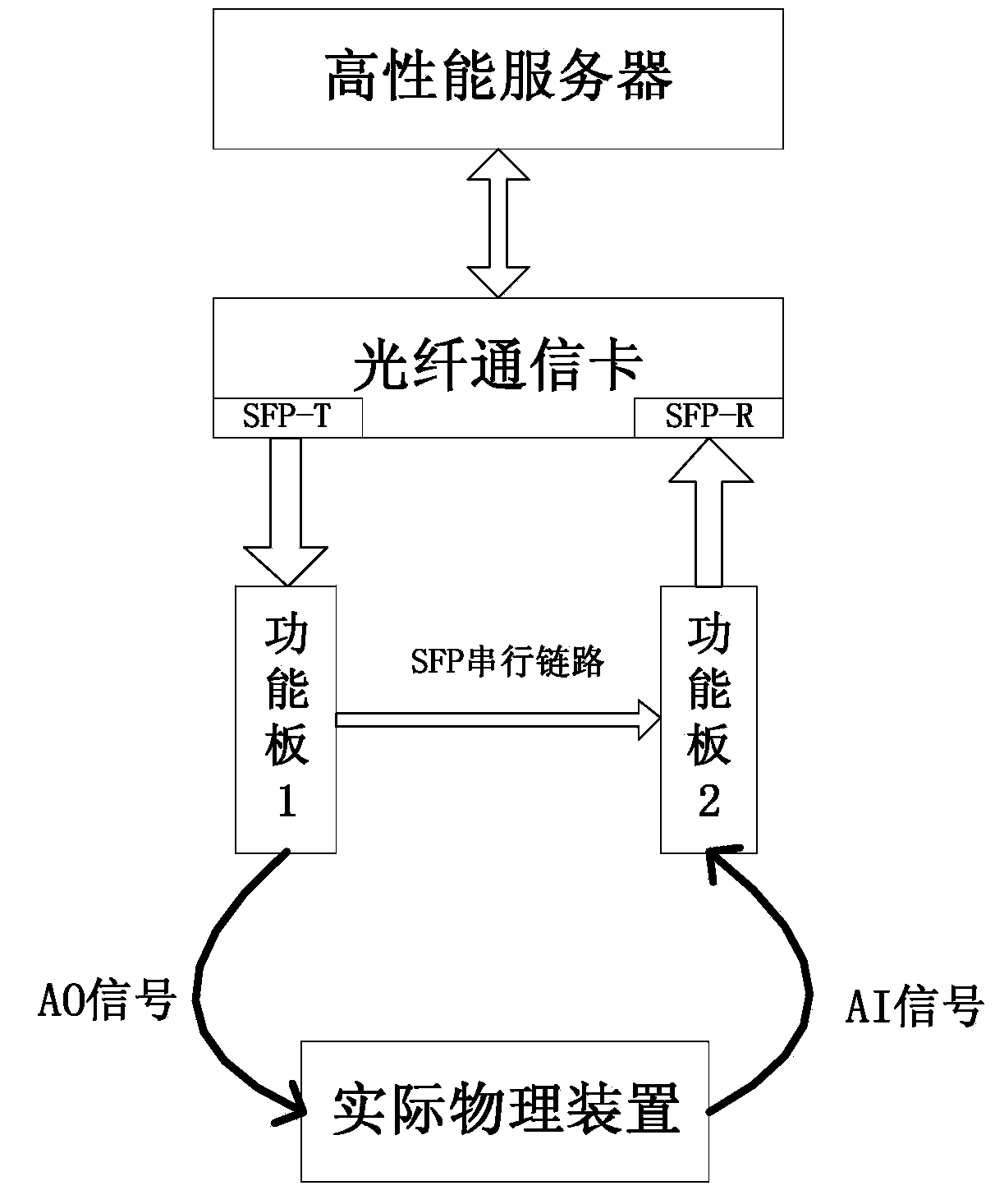

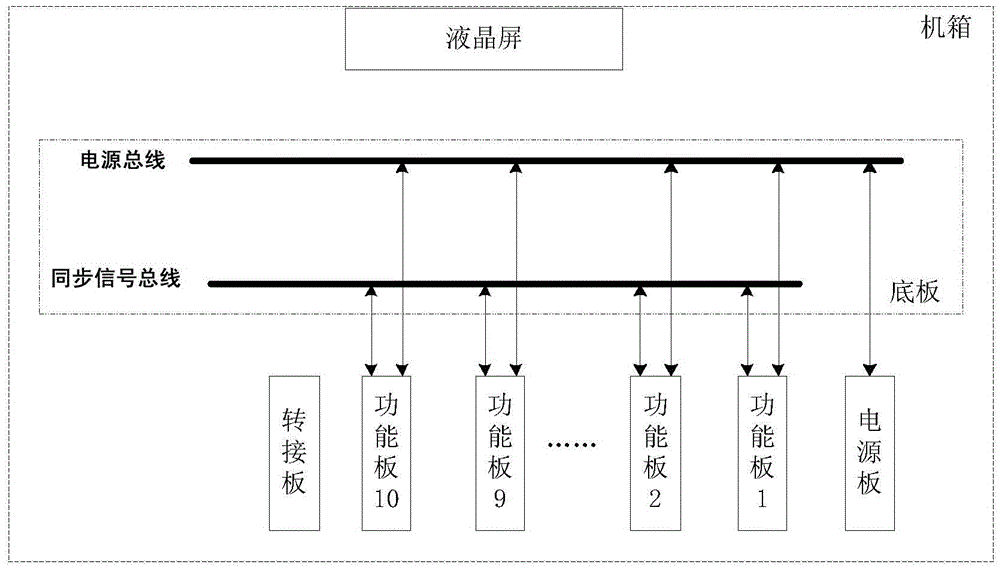

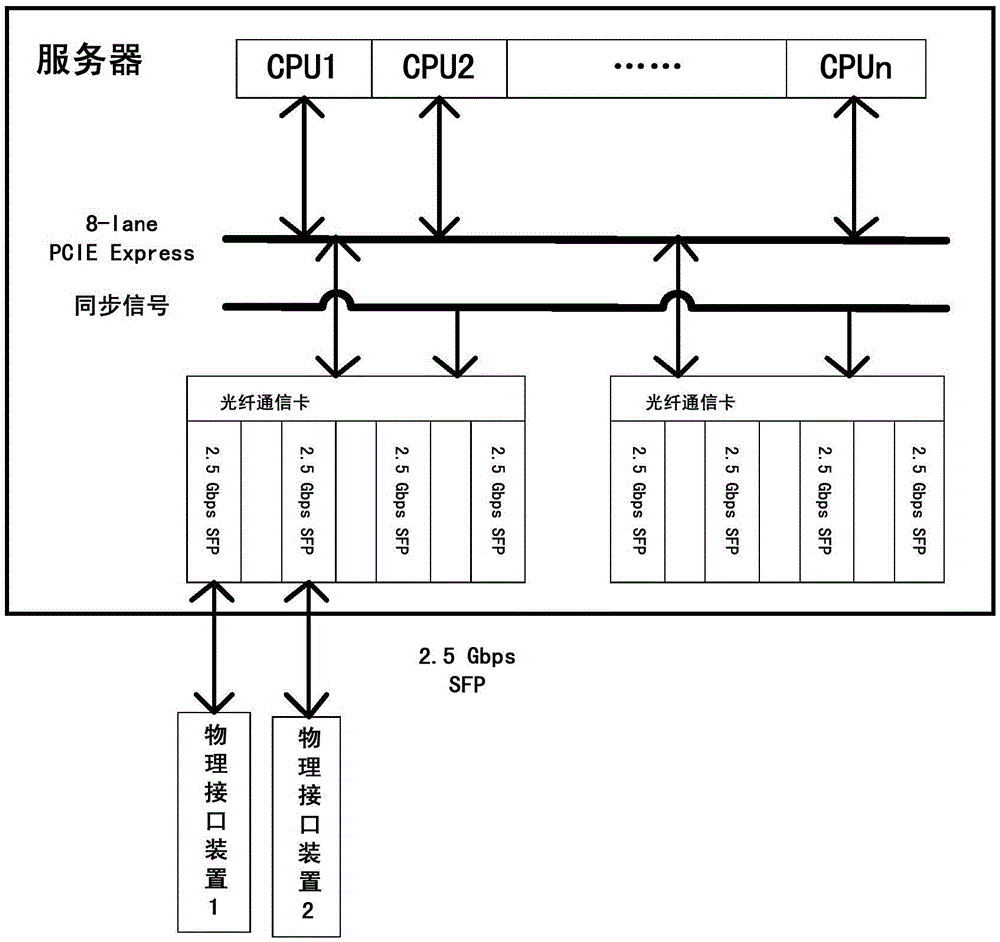

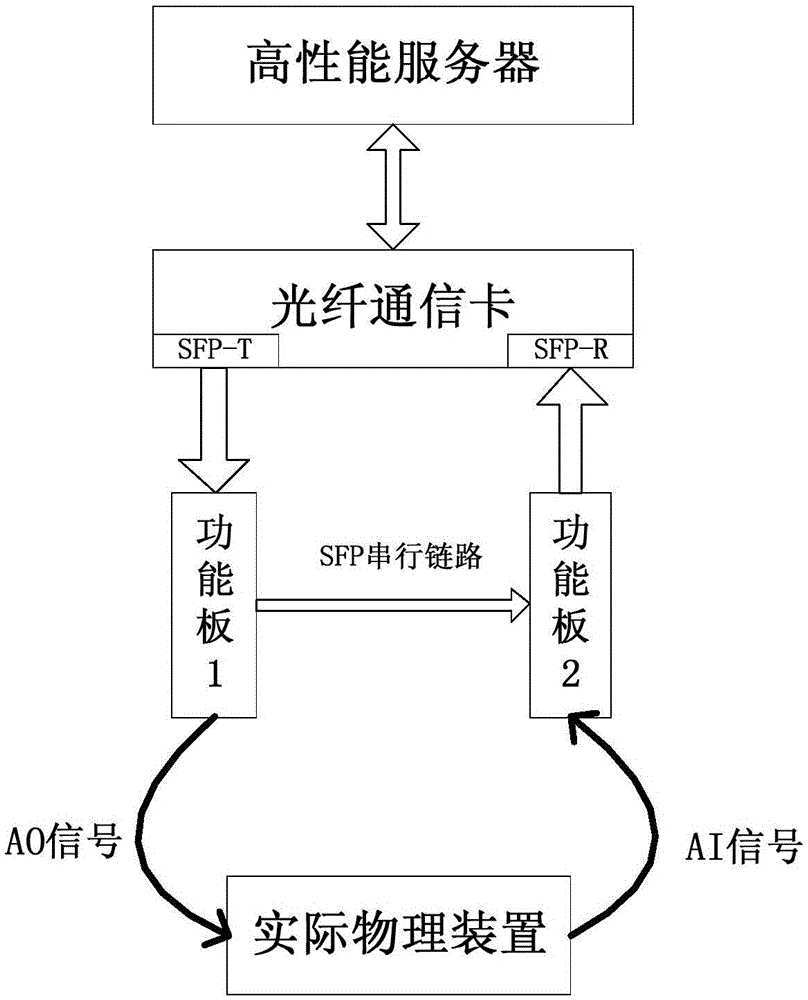

Digital real-time simulation physical port device of power system based on optical fiber communication

ActiveCN103472733AMeet real-time IO needsIncrease I/O scaleSimulator controlReal-time simulationElectric power system

The invention provides a digital real-time simulation physical port device of a power system based on optical fiber communication. The port device comprises a machine case, a bottom plate, a power plate, a functional plate and a liquid crystal screen, wherein the bottom plate, the power plate, the functional plate and the liquid crystal screen are located in the machine case. The bottom plate is vertical to an upper panel and a lower panel of the machine case, the power plate and the functional plate are respectively fixed through insertion grooves formed in the upper panel of the machine case, the lower panel of the machine case and the bottom plate, and the liquid crystal screen is installed on a front panel of the machine case and is connected with the bottom plate through a PCI bus. The digital real-time simulation physical port device of the power system based on optical fiber communication has the advantages of being large in port scale, high in sampling accuracy, high in data processing speed, high in synchronization precision and the like, and can meet new test requirements.

Owner:STATE GRID CORP OF CHINA +1

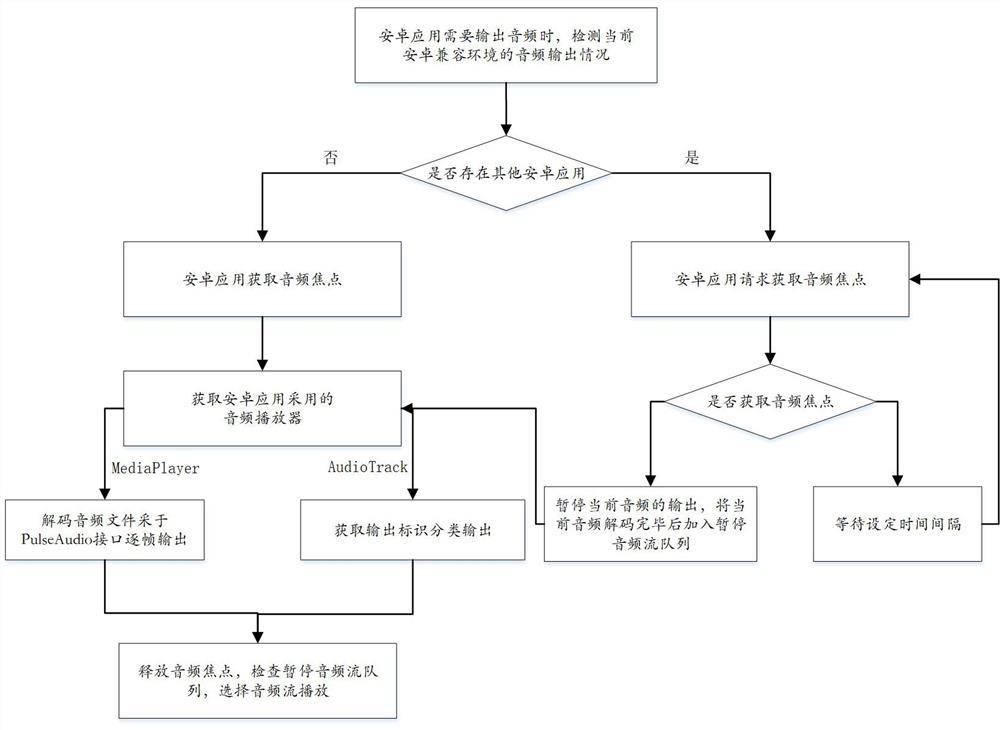

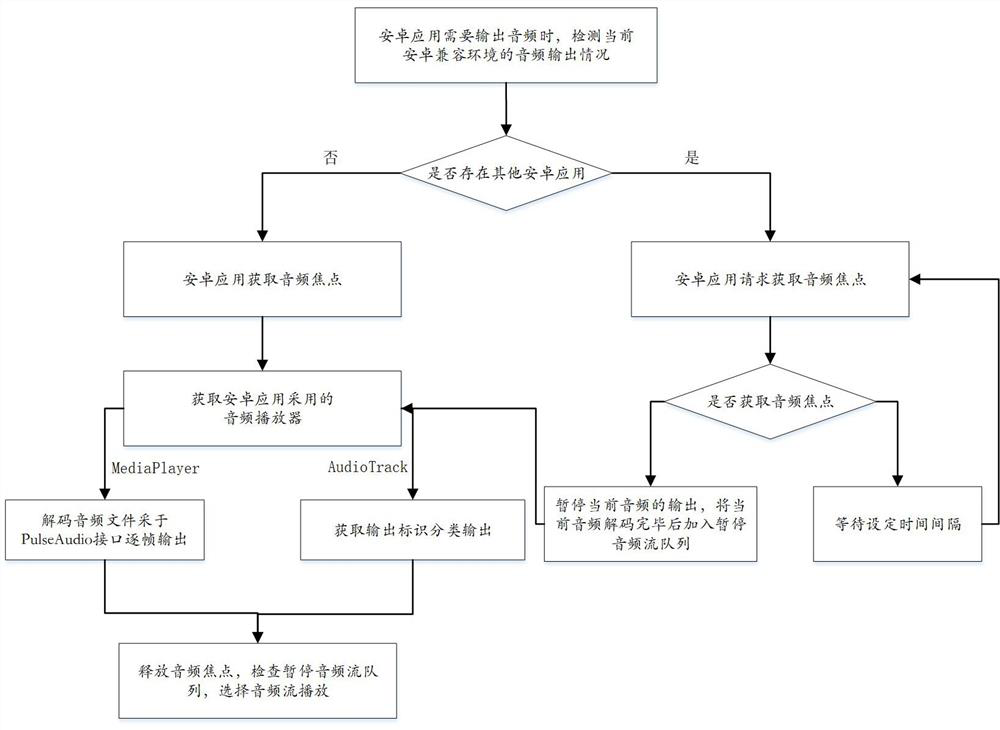

Low-delay audio output method for Android application on Linux platform

ActiveCN114333933AReduce processImprove audio output efficiencyDigital storageSound input/outputAndroid appDelay

The invention discloses a low-delay audio output method for an Android application on a Linux platform, and the method comprises the steps: determining an audio output mode through obtaining the type of an audio player adopted by the Android application in an Android compatible environment in a Linux system, and effectively reducing the processes involved by the Android application in an audio playing process through different output modes. According to the method, the data interaction between the processes is reduced, the audio output efficiency of the Android application is effectively improved, the output delay is reduced, and the user experience is improved.

Owner:北京麟卓信息科技有限公司

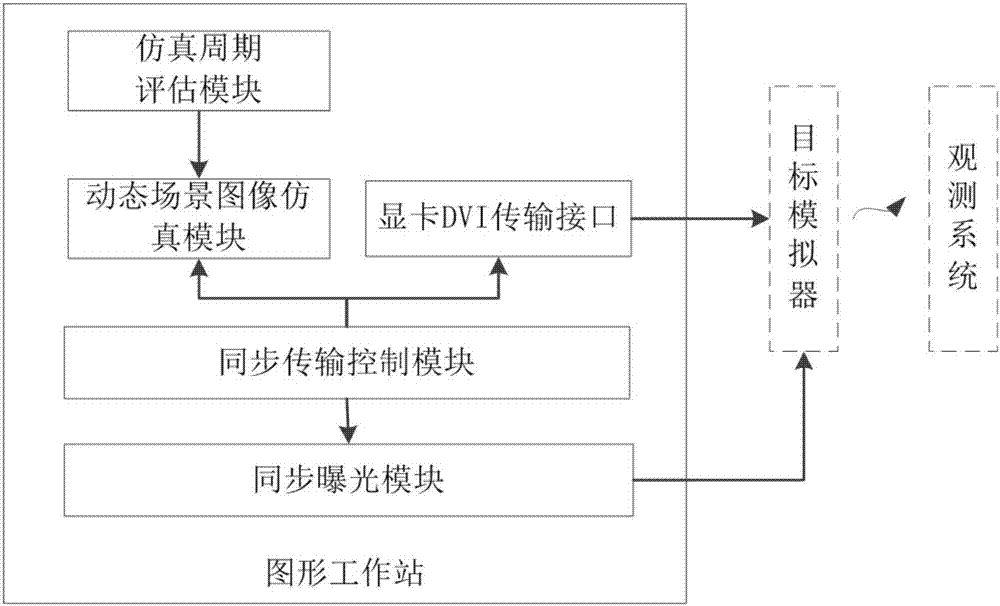

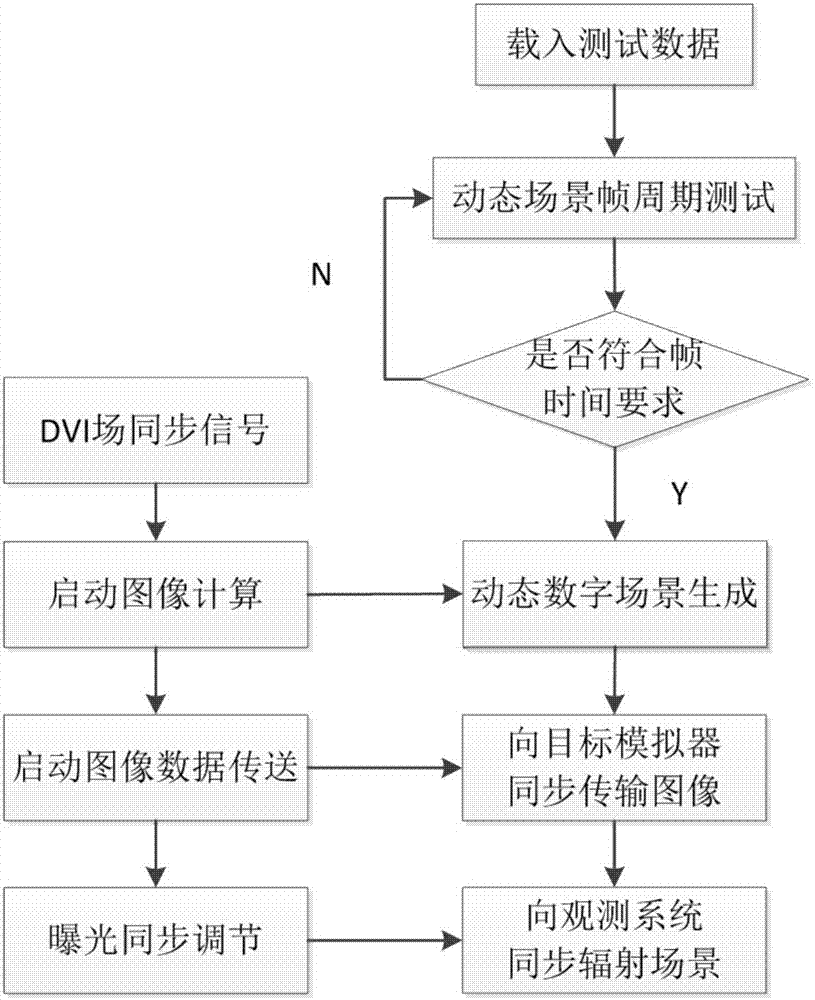

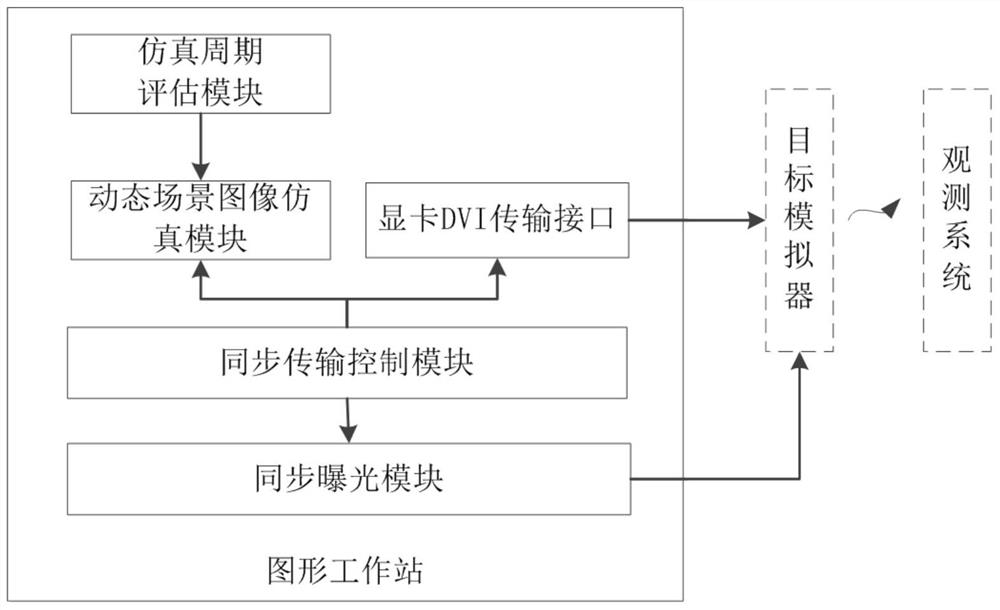

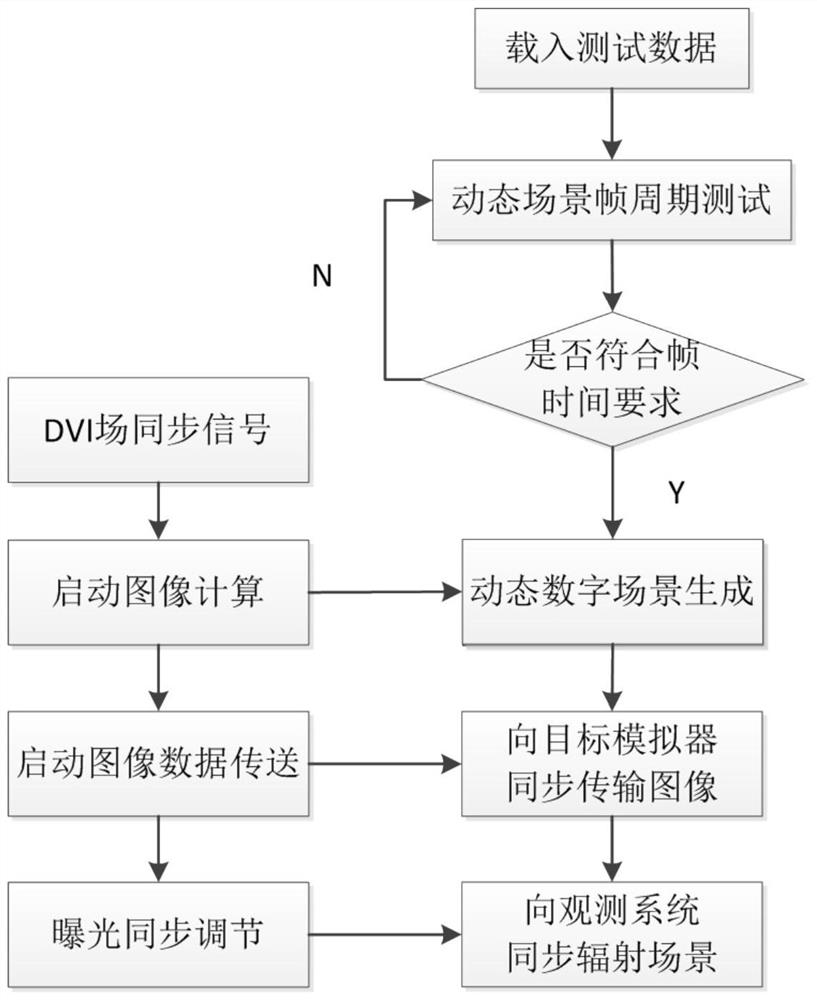

Target simulator real-time drive system and method based on DVI interface of graphics card

ActiveCN107305697AOutput delay is smallImprove Simulation Confidence3D-image renderingGraphic cardGraphics workstation

The present invention discloses a target simulator real-time drive system based on a DVI interface of a graphics card. The system comprises: a DVI transmission interface, used for establishing a data communication with a graphic workstation and a target simulator; a synchronous transmission control module, used for sending a simulation start signal to a dynamic scene image simulation module based on a field frequency signal output by the DVI transmission interface, and establishing synchronous data transmission with the target simulator; and the dynamic scene image simulation module, used for performing simulation analysis on to-be-tested dynamic scene data acquired from an external device based on the simulation start signal, and storing simulation image data into a frame cache. The present invention further discloses a target simulator real-time drive method based on a DVI interface of a graphics card. The technical scheme provided by the present invention shortens radiation scene output delay, ensures delay stability and thus greatly improves confidence of semi-physical dynamic scene simulation.

Owner:BEIJING SIMULATION CENT

Virtual cascade time delay compensation restoring apparatus

InactiveCN1301609COutput delay is smallHigh working reliabilityData switching detailsTime-division multiplexTime delaysEngineering

The device consists of cascade multiframe detection circuit for carry on sequence number locking detection, cascade sequence automatic regulation circuit for regulating reservoir sequence based on sequence number of each different reservior in cascade set to make it be in accordance with its sequence at transmission end, buffer zone for making zone as per sequence number of reservior and cascade multiframe, write control circuit for writing content in sequenced reservior to relevant buffer zone, read control repositioning and adaptive circuit for regulating frequency and plase of reservoir and read control circuit for reading out data from buffer zone to finalize restoration of cascade as per command of abovesaid circuit.

Owner:GLOBAL INNOVATION AGGREGATORS LLC

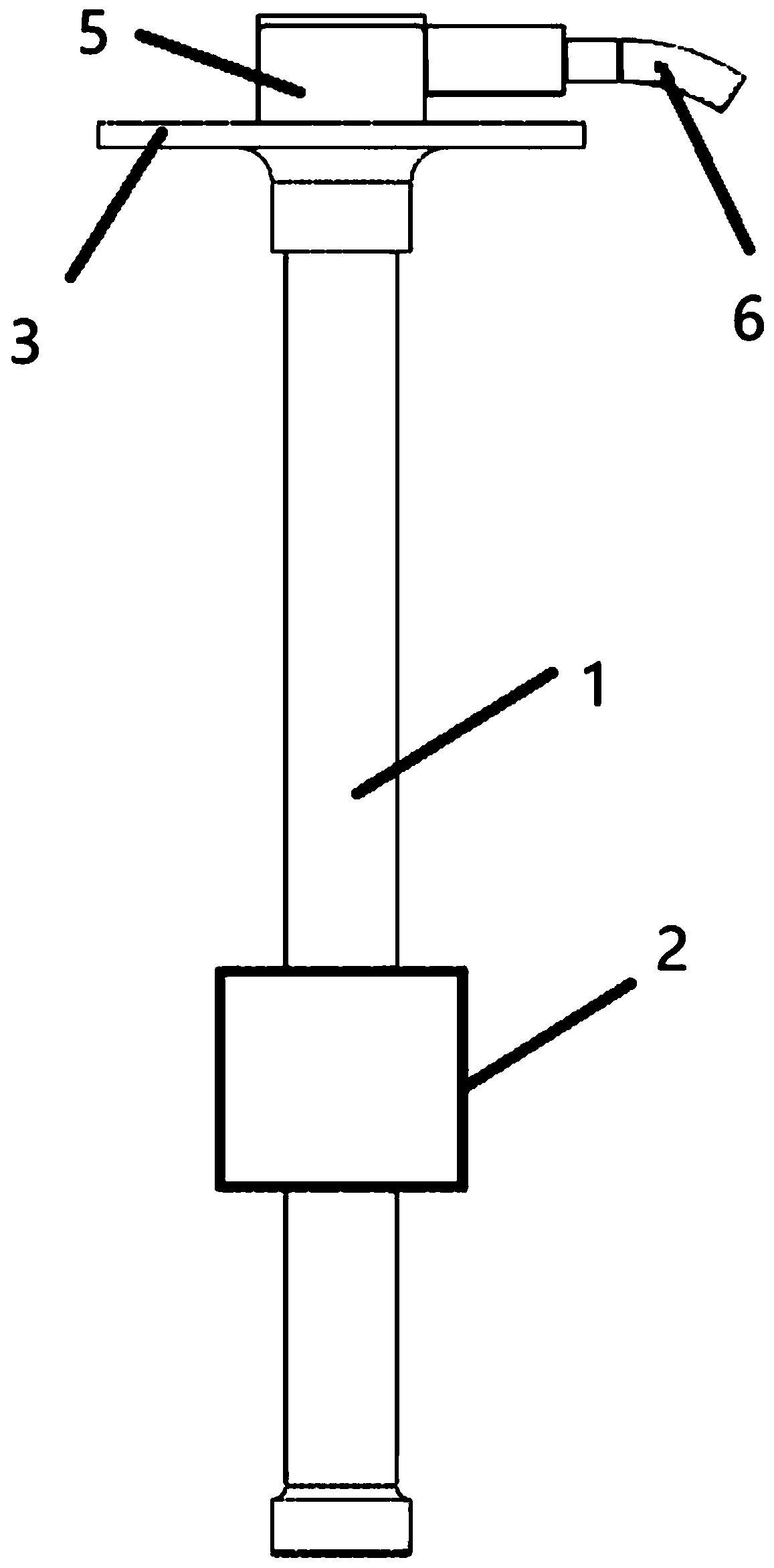

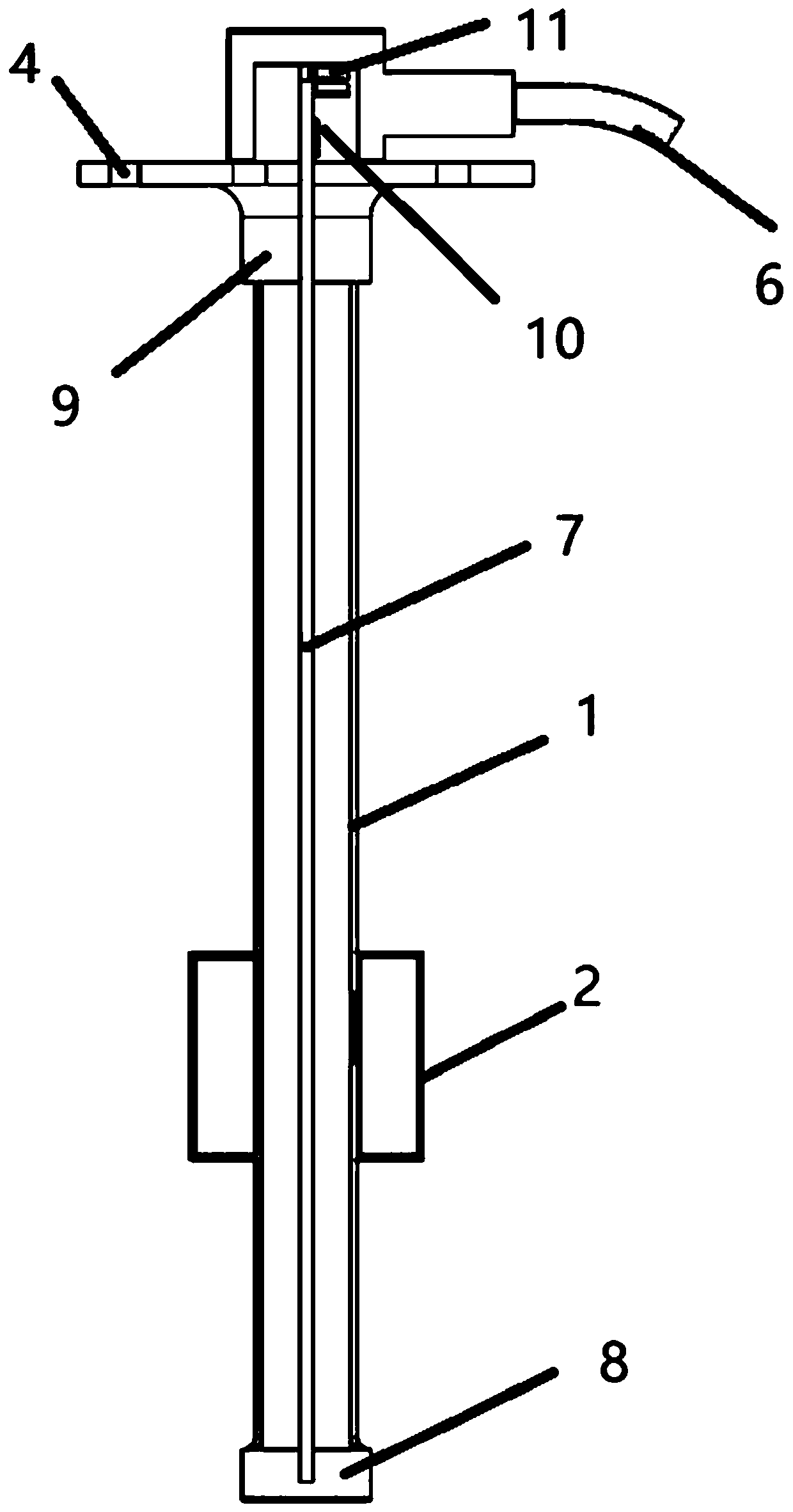

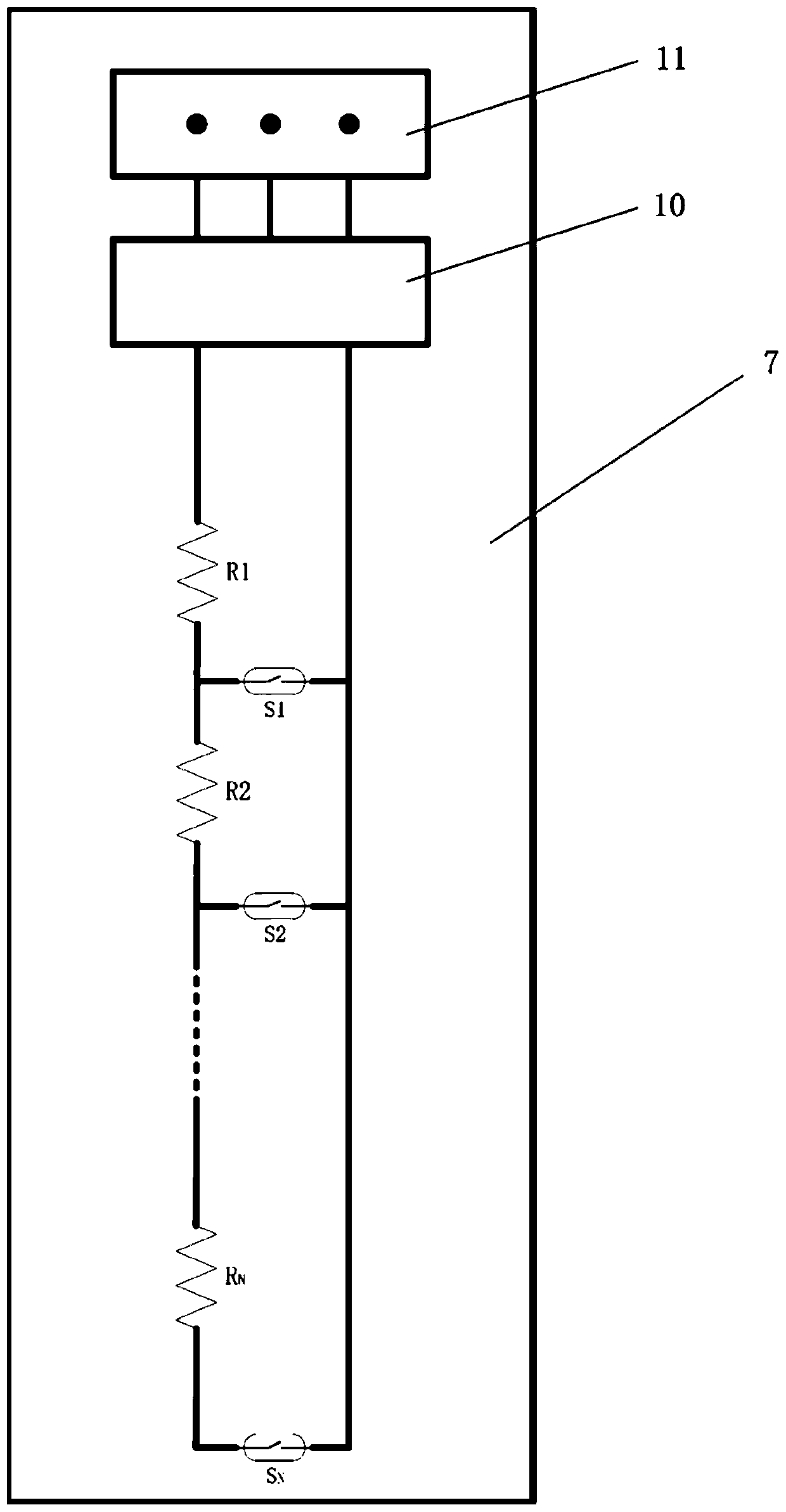

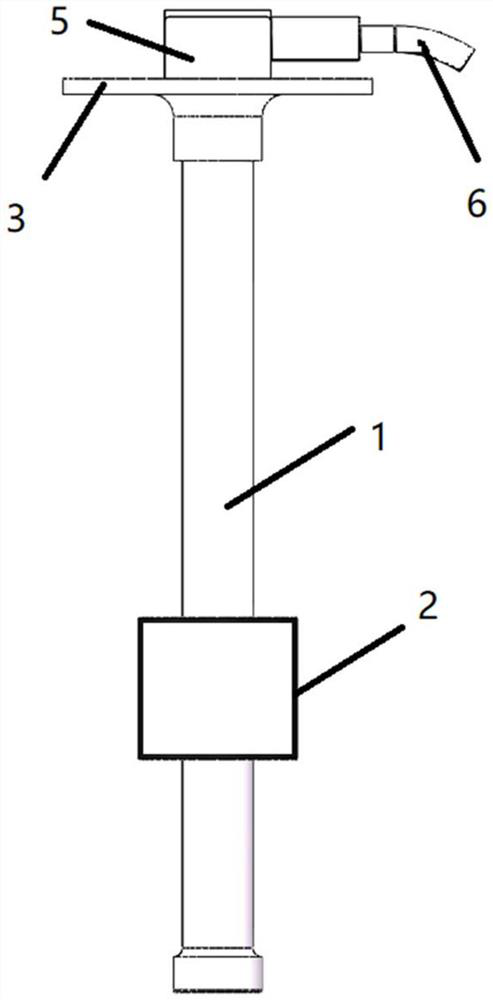

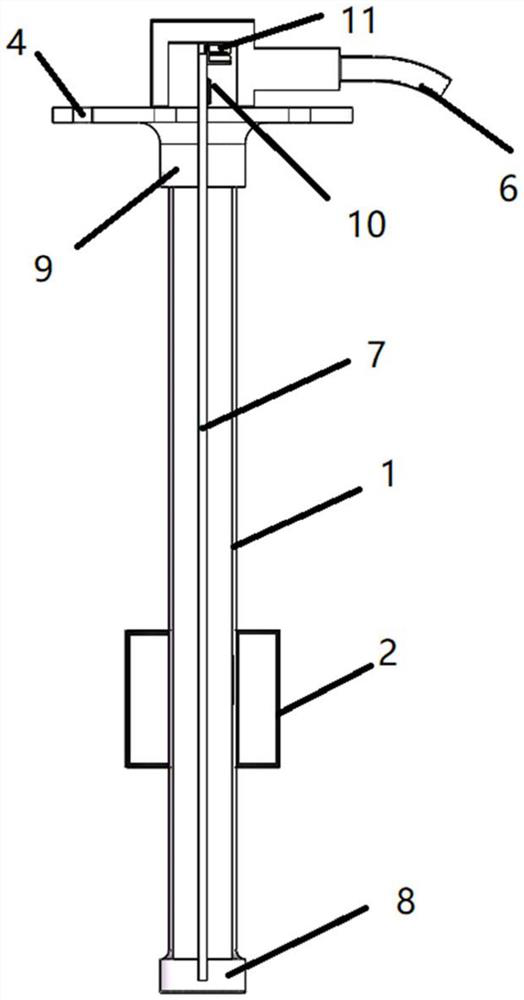

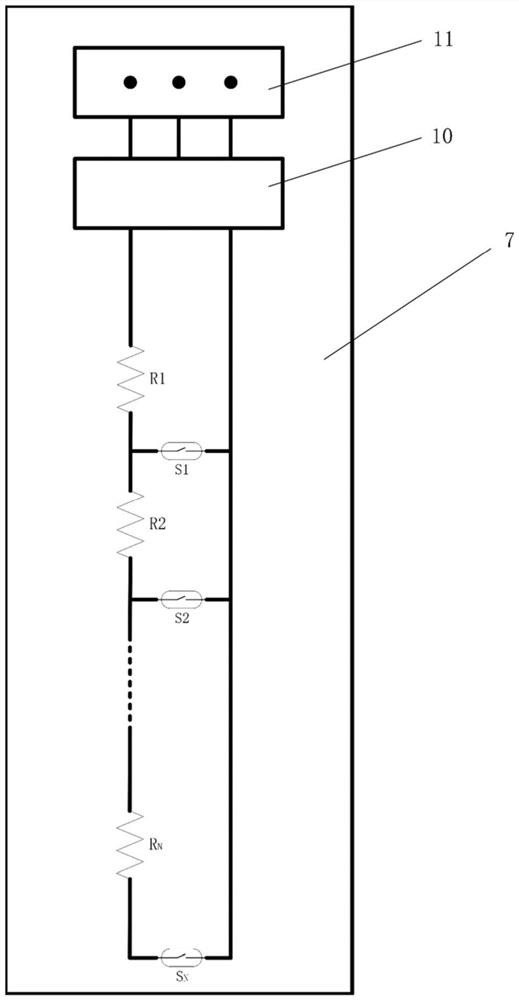

Oil tank oil level sensing mechanism and sensor using oil tank oil level sensing mechanism

ActiveCN111103039AHigh position signal accuracyHigh resolutionLevel indicators by floatsThermodynamicsElectrical and Electronics engineering

The invention discloses an oil tank oil level sensing mechanism and a sensor using the oil tank oil level sensing mechanism. The oil tank oil level sensing mechanism comprises a signal circuit moduleand a moving module which perform mutual induction. The signal circuit module comprises a circuit board assembly; a processing circuit assembly which is arranged on the circuit board assembly; an induction assembly which is arranged on the circuit board assembly, wherein the induction assembly is connected with the processing circuit assembly and the induction assembly and the moving module are inmutual induction; and an induction film which is arranged on the circuit board assembly and covers the induction assembly. The position signal precision is high and the resolution ratio is high; thecost is low and the structure is simple; the stability of the position signal of the sensor in a severe working environment is ensured; the induction film made of the soft magnetic material has the characteristics of low coercive force, low magnetic saturation density and high magnetic conductivity, the material can realize the maximum magnetization intensity or magnetic saturation by using the minimum external magnetic field and the fastest speed, and when the external magnetic field disappears, the material can be demagnetized at the fastest speed.

Owner:赛卓电子科技(上海)股份有限公司

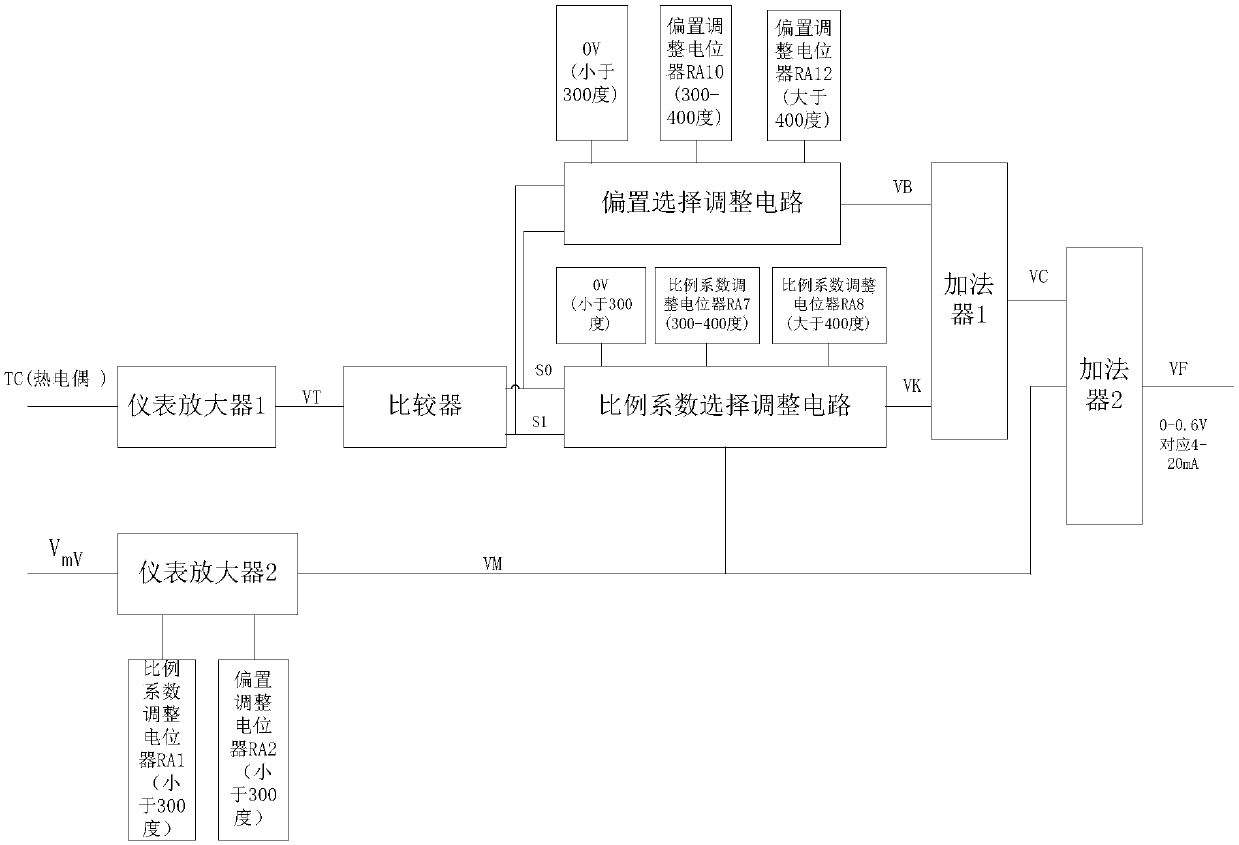

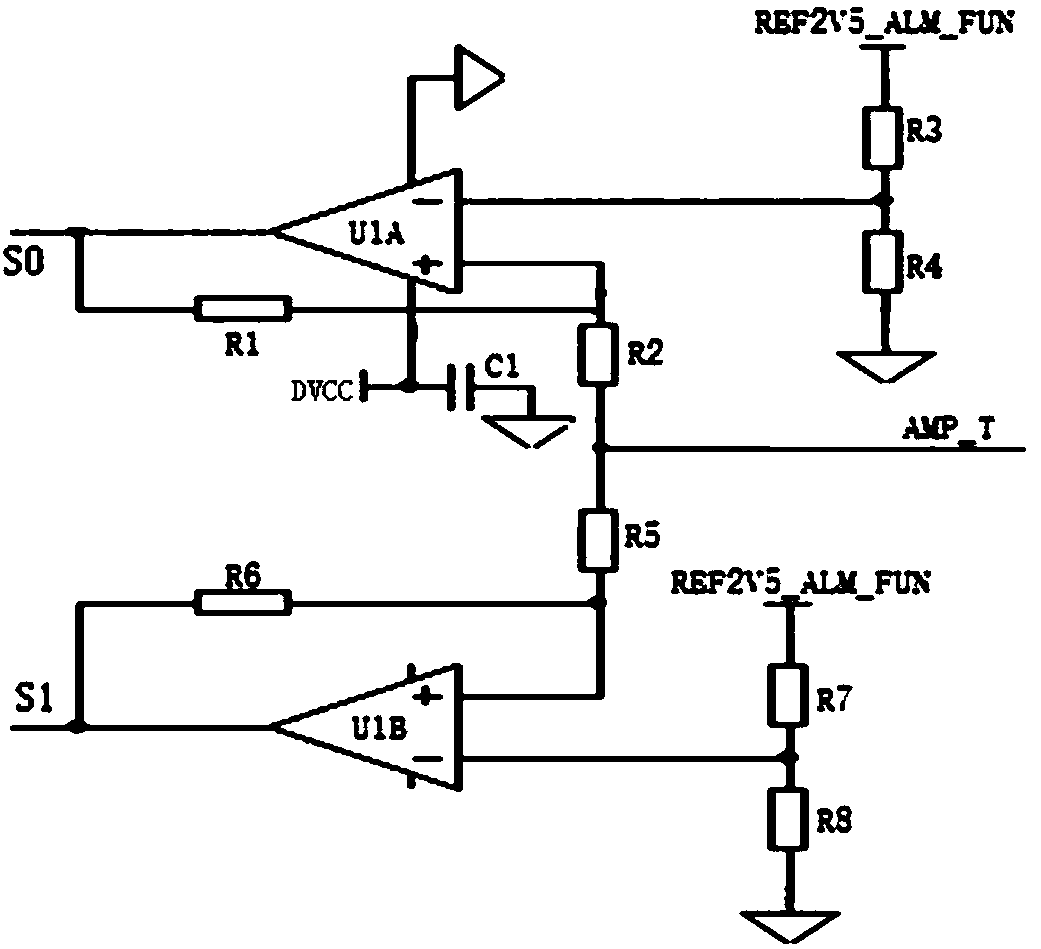

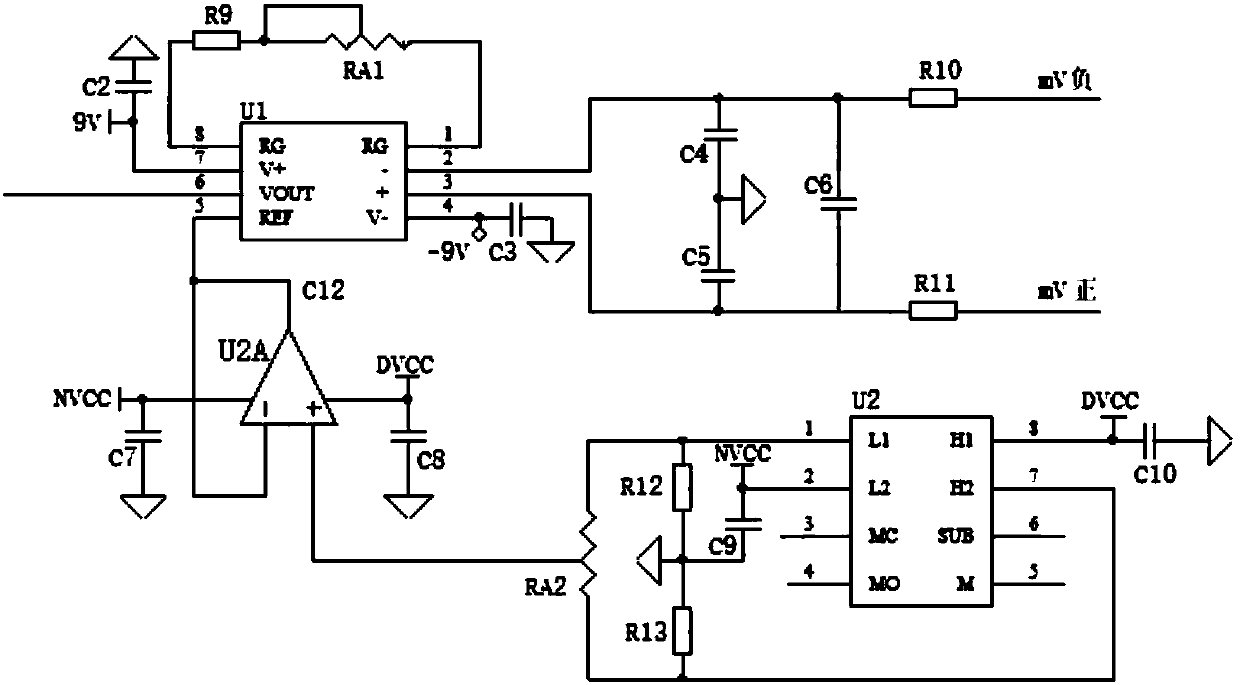

mV signal measurement temperature compensation device

PendingCN110530445ASimplify design difficultyShorten the development cycleVolume variation compensation/correction apparatusVolume/mass flow by electromagnetic flowmetersAudio power amplifierInstrumentation amplifier

The invention provides an mV signal measurement temperature compensation device. The compensation device comprises an instrumentation amplifier I for amplifying an output voltage of a thermocouple, aninstrumentation amplifier II for amplifying the output voltage of a primary sensor, a comparator circuit, a bias selection adjustment circuit, a proportionality coefficient selection adjustment circuit, an adder I and an adder II; the comparator circuit outputs a signal S0 and a signal S1 after performing comparison processing on output signals of the instrumentation amplifier I, and the signal S0 and the signal S1 are respectively used as input signals of the proportionality coefficient selection adjustment circuit and the bias selection adjustment circuit; and the output of the bias selection adjustment circuit and the output of the proportionality coefficient selection adjustment circuit are used as the input of the adder I, and the output of the adder I and the output of the instrumentation amplifier I are used as the input of the instrumentation amplifier II.

Owner:CHONGQING CHUANYI AUTOMATION

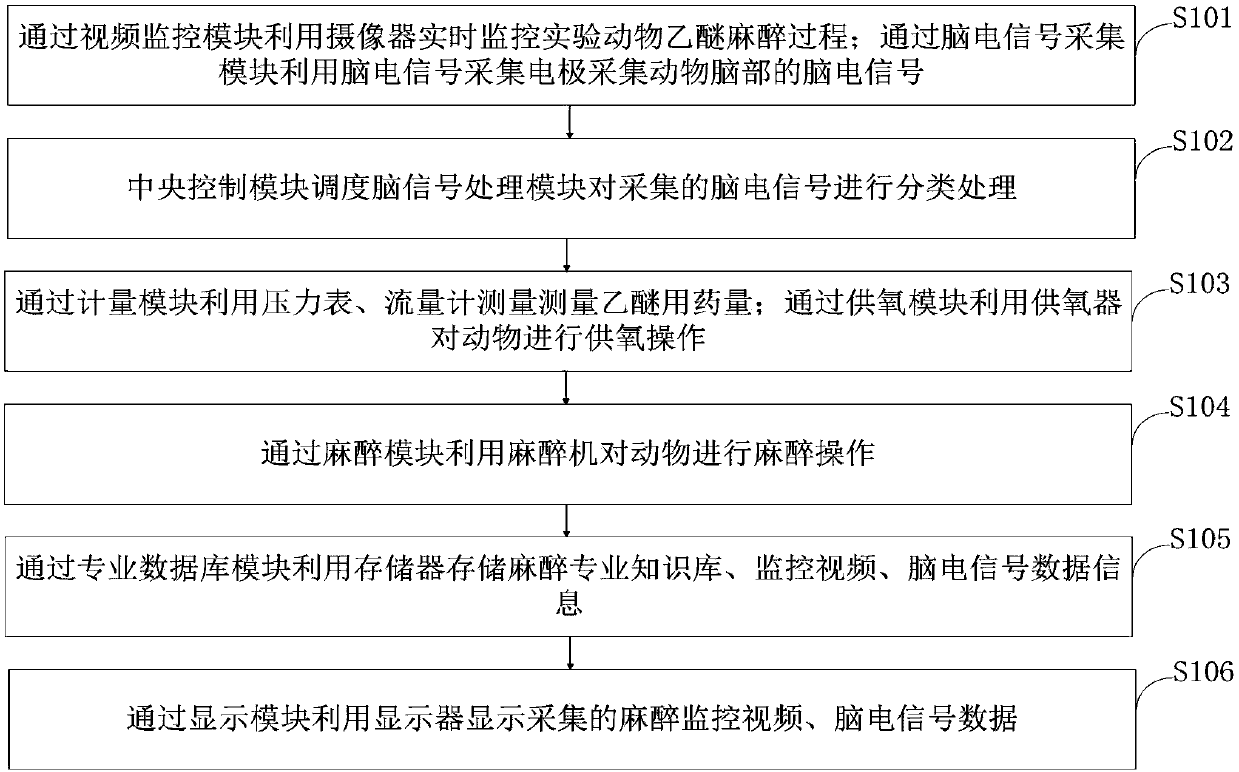

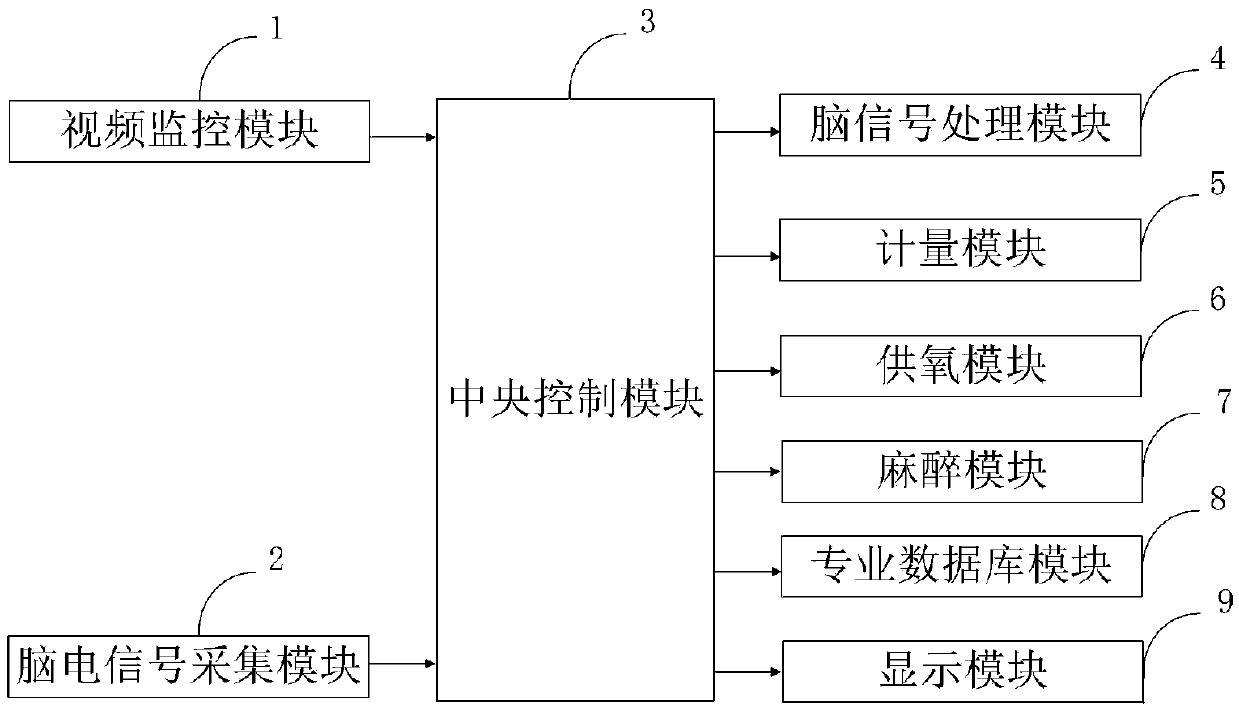

Ether anesthesia system for laboratory animal and operating method of system

InactiveCN109646146AOutput delay is smallReduce mistakesDiagnostic recording/measuringSensorsVideo monitoringMetering mode

The invention belongs to the technical field of anesthesia, and discloses an ether anesthesia system for a laboratory animal and an operating method of the system. The ether anesthesia system for thelaboratory animal comprises a video monitoring module, an electroencephalogram collecting module, a central control module, an electroencephalogram processing module, a metering module, an oxygen supply module, an anesthesia module, a special database module and a display module. Through the electroencephalogram processing module, a self-adaptation fuzzy logic reasoning algorithm is adopted, dataof low-frequency waves, high-frequency waves and BFI in different anesthesia states is trained, and the method has a great resolution capability; the method can automatically display different anesthesia depths, and other nonlinear interference is avoided; meanwhile, through the metering module, the dosage of gaseous anaesthetic in the whole anesthesia process can be precisely calculated, errors caused by manual calculation are avoided, and the accuracy and precision of the dosage calculation result of the liquid anaesthetic are effectively improved.

Owner:QINGDAO UNIV

A fpga implementation system based on low-latency lz lossless compression algorithm

ActiveCN106385260BQuick compressionImprove the defect that the output delay is uncertainCode conversionShift registerHash function

The invention discloses an FPGA realization system of LZ lossless compression algorithm based on a low delay. The system comprises an input cache module, an output cache module, a shift register, a read-back control module, a matching search module, a character length calculation module, a matched length calculation module, and an output control module. The input cache module is used for caching input source data and addressing. The output cache module is used for caching output compressed data. The shift register is used for converting the input source data into 4-bit data needed by hash function calculation through shift. The read-back control module is used for carrying out read-back to obtain source data matched with a search need. The matching search module is used for carrying out matching searching of source data word-by-word hash calculation. The character length calculation module is used for calculating the length of a character which can be not matched in a compressed sequence. The matched length calculation module is used for calculating the length of the matched character in the compressed sequence.

Owner:中电莱斯信息系统有限公司

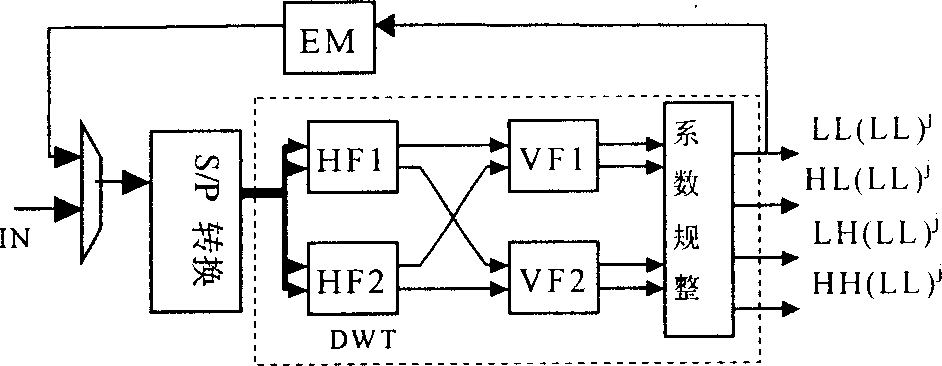

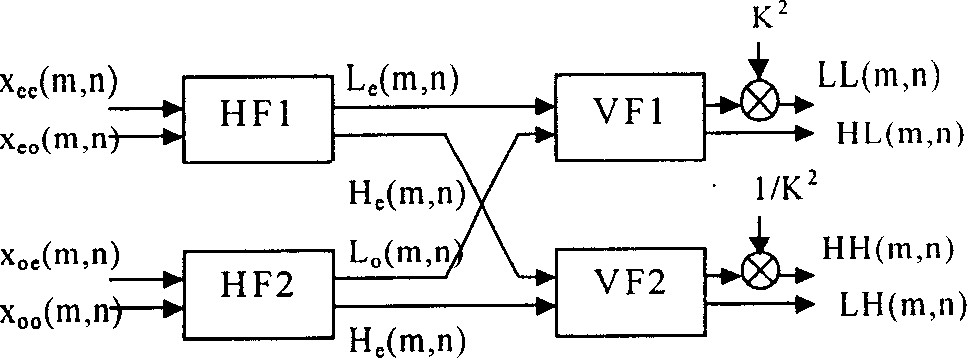

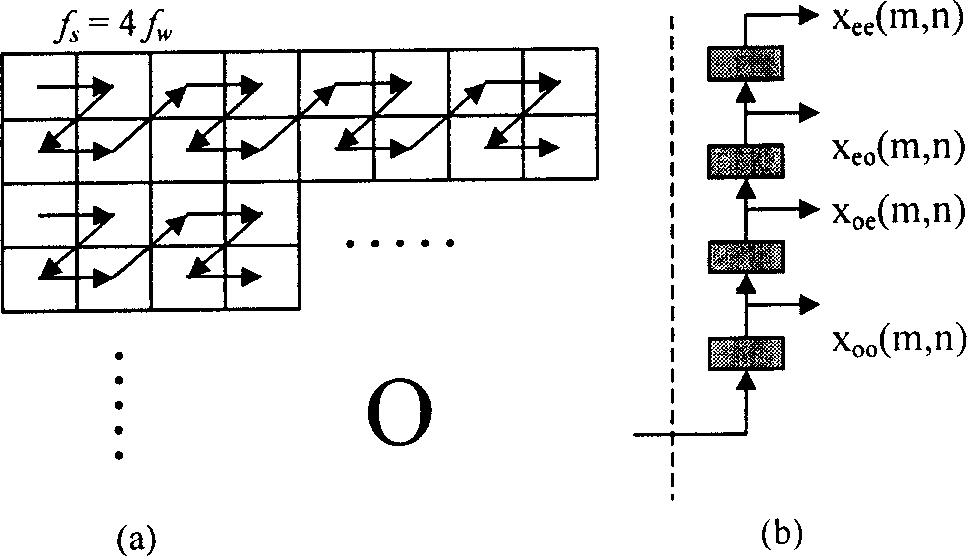

Circuit for realizing direct two dimension discrete small wave change

InactiveCN1295653CReduce power consumptionReduce control complexityImage codingData seriesExternal storage

The invention is a circuit for realizing direction two-dimension discrete wavelet transition, which belongs to image data processing technology field, especially relates to hardware realization of direct two-dimension discrete wavelet transition. The aim is to decrease hardware cost and system delay, and it can be applied to very large scale integration circuit structure design of high speed and low power direct two-dimension discrete wavelet transition of all limit length filters, the invention includes selector, data series and parallel converting interface circuit, primary converting circuit which are connected in order electrically; the primary converting circuit is 4 input and 4 output structure, includes the first parallel filter and the second parallel filter, the first vertical filter and the second vertical filter connected to them and output coefficient regulating unit, the parallel and vertical filters are 2 input and 2 output structure, the first vertical filter and the second vertical filter output is connected to the output coefficient regulating unit; one output electric signal of the output coefficient regulating unit is connected to an external memory, the latter is outputted to one input end of the selector.

Owner:HUAZHONG UNIV OF SCI & TECH

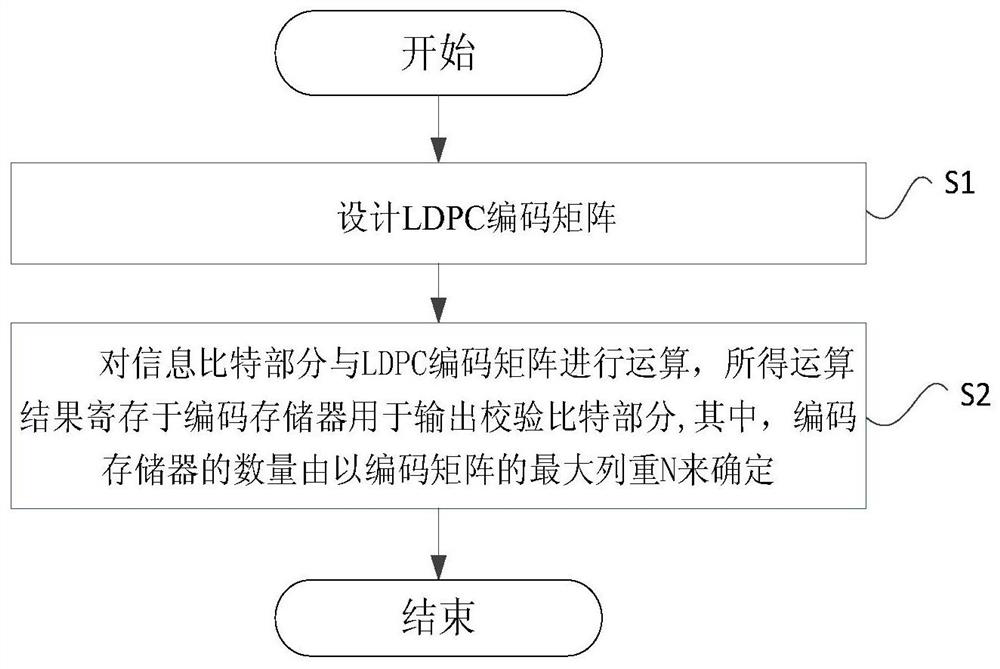

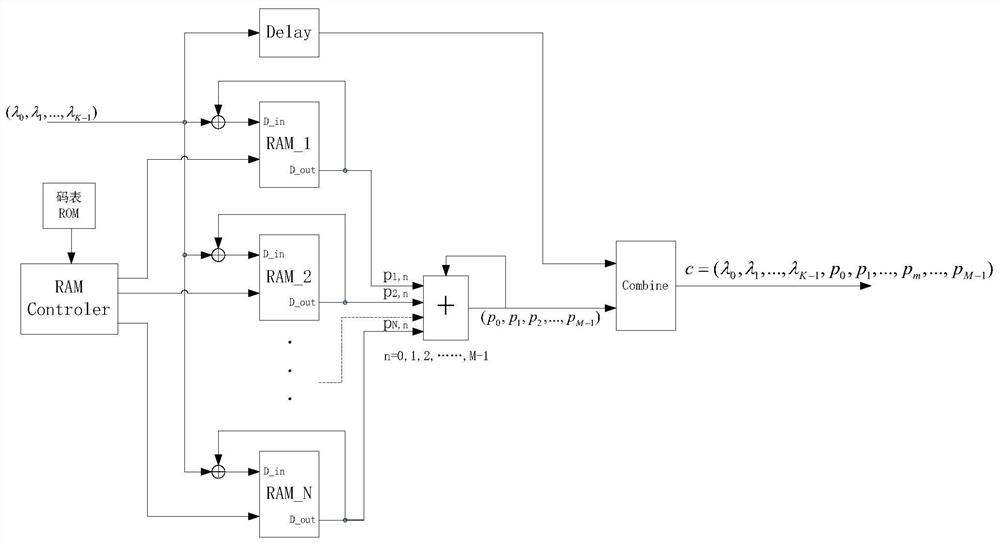

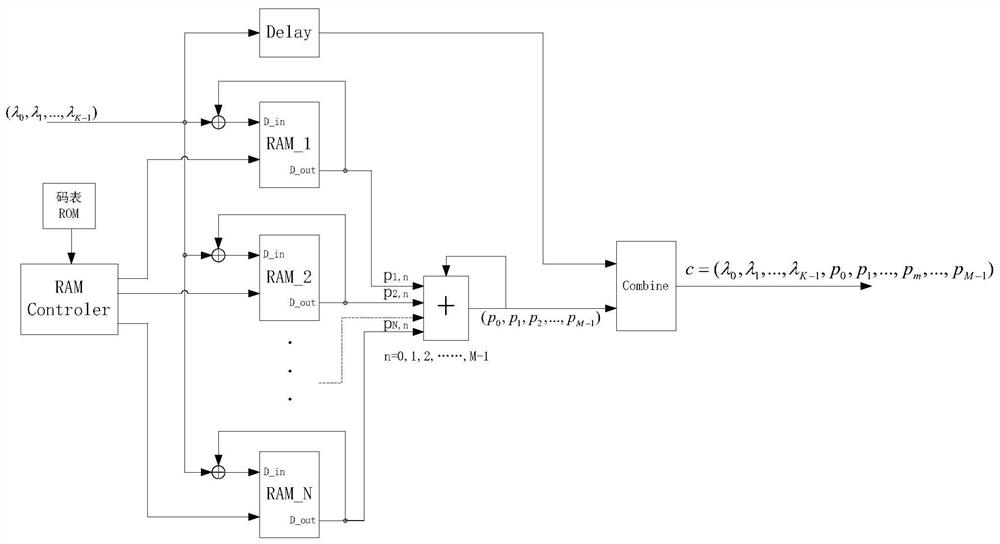

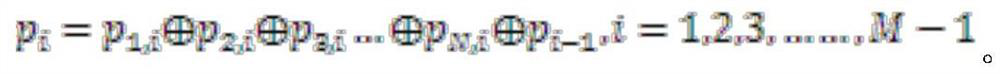

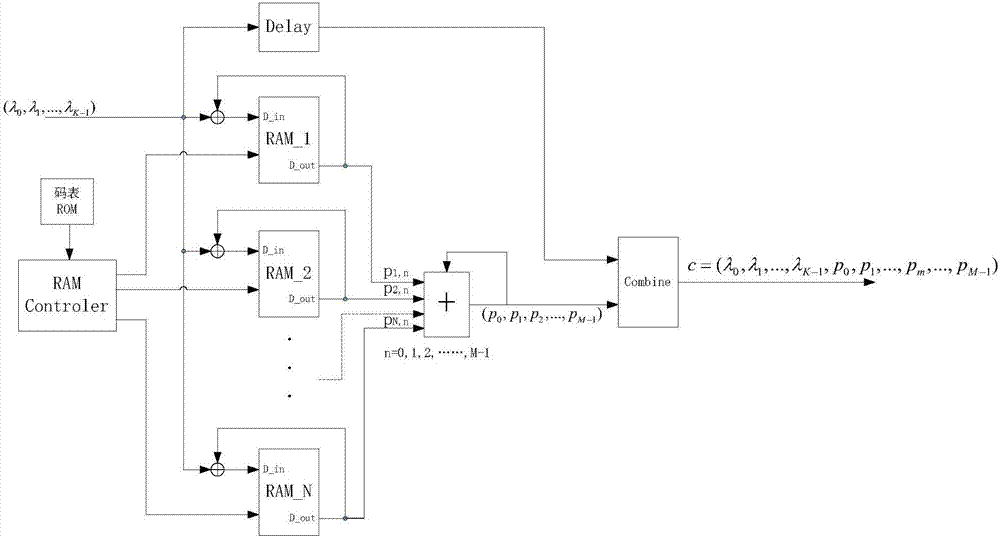

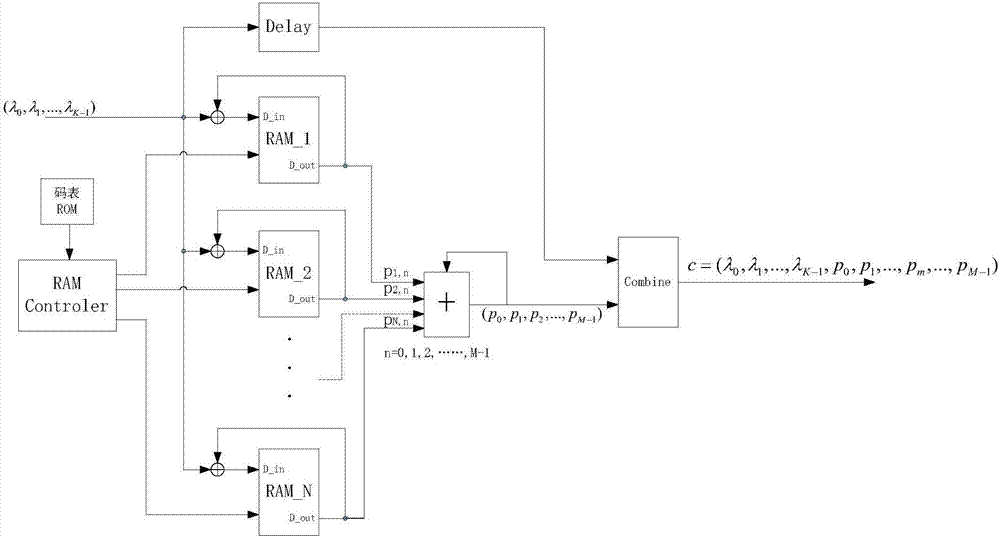

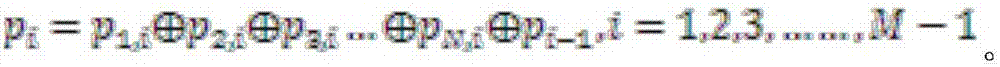

an ldpc encoder

ActiveCN107959501BOutput delay is smallSave storage spaceError correction/detection using multiple parity bitsCode conversionControl storeEngineering

The present invention provides an LDPC encoder, comprising: an encoding memory for storing a set LDPC encoding matrix and an LDPC code table; N random access memory RAMs; and a storage controller for controlling the reading and writing of the N RAMs in parallel; The operator is used to perform operations on the information bit part in the encoded codeword and the LDPC encoding matrix; the delay module represents a necessary delay for the input information bit part, so that the generated parity bit part can be continuous with the information bit part Output; the splicing module is used to splice the information bit part and the parity bit part to output, wherein the operation result obtained by the operator is stored in the coding memory, and the number of the coding memory is determined by the maximum column weight N of the coding matrix , the present invention can make the storage space of the LDPC coder as small as possible without making the design too difficult, and can also take into account the versatility of different codewords.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

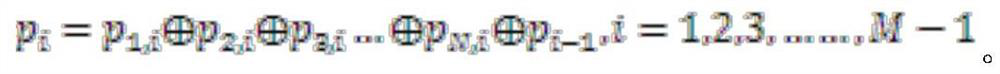

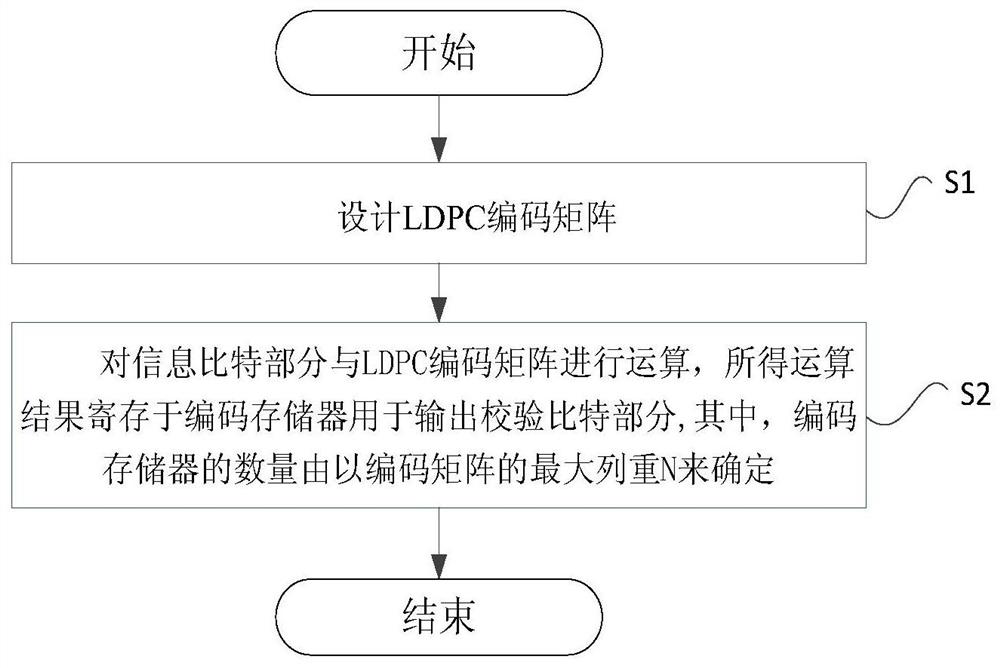

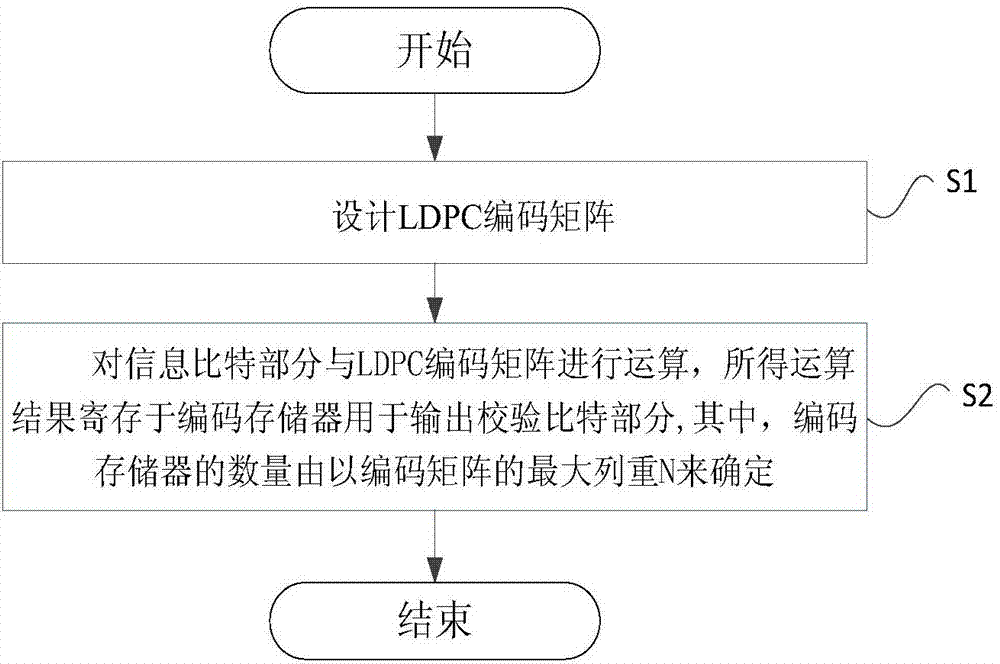

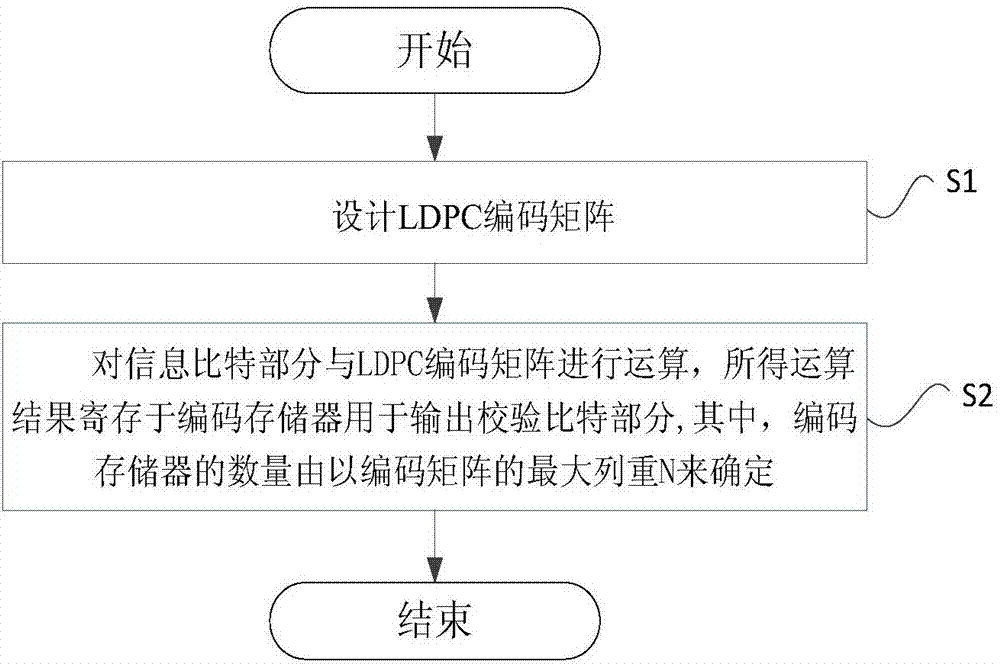

A kind of ldpc encoding method

ActiveCN107959502BOutput delay is smallAddressing control complexity is reducedError correction/detection using multiple parity bitsCode conversionAlgorithmEngineering

The invention provides a kind of LDPC encoding method, comprising the following steps: designing an LDPC encoding matrix for LDPC encoding; initializing the encoding memory RAM, and sequentially inputting the information bit part of the serial input and the column matrix information of each column of the encoding matrix respectively Carry out the operation, and the obtained operation result is stored in the encoding memory for outputting the parity bit part; wherein, the quantity of the encoding memory is determined by the maximum column weight N of the encoding matrix, and the LDPC encoding matrix is designed, including: the encoding matrix takes L columns as the unit , divided into several sub-column matrices; the first column matrix information in the sub-column matrix is given by the LDPC code table, and the subsequent adjacent column matrix information is obtained from the first column matrix information through a preset calculation method. This method can make LDPC code The storage space of the device should be as small as possible without making the design too difficult, and the versatility of different codewords can also be taken into account.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

HS-SCCH channel coding device for high speed downlink packet access

ActiveCN101026412BIncrease profitOutput delay is smallError preventionRadio transmission for post communicationTime delaysComputer science

The encoding device for HS-SCCH channel makes the output data compact, reduces time delay, and raises circuit usage. The device includes first process circuit and second process circuit. The first process circuit includes the first convolutional coding unit (CCU), and first rate adaption unit (RAU). The first CCU encodes the input data; and RAU carries out rate matching or XOR process for the data, which are than outputted. Characters are that providing enable signal for the first process circuit to read next set of input data, the second process circuit includes following units: connected insequence CRC16 circuit unit, second CCU, second RAU, counter monitoring unit, and time delay compensation unit located at one or several positions: in front of CRC16 circuit unit, between CRC16 circuit unit and second CCU, and between second CCU and second RAU.

Owner:SANECHIPS TECH CO LTD

A low-latency audio output method for Android applications on the Linux platform

ActiveCN114333933BReduce processImprove audio output efficiencyDigital storageSound input/outputAndroid appLatency (audio)

The invention discloses a low-latency audio output method for Android applications on a Linux platform. The audio output mode is determined by obtaining the type of audio player used by an Android application in an Android compatible environment in a Linux system, and different output modes can effectively reduce The process involved in the audio playback process of the Android application is reduced, the data interaction between the processes is reduced, the audio output efficiency of the Android application is effectively improved, the output delay is reduced, and the user experience is improved.

Owner:北京麟卓信息科技有限公司

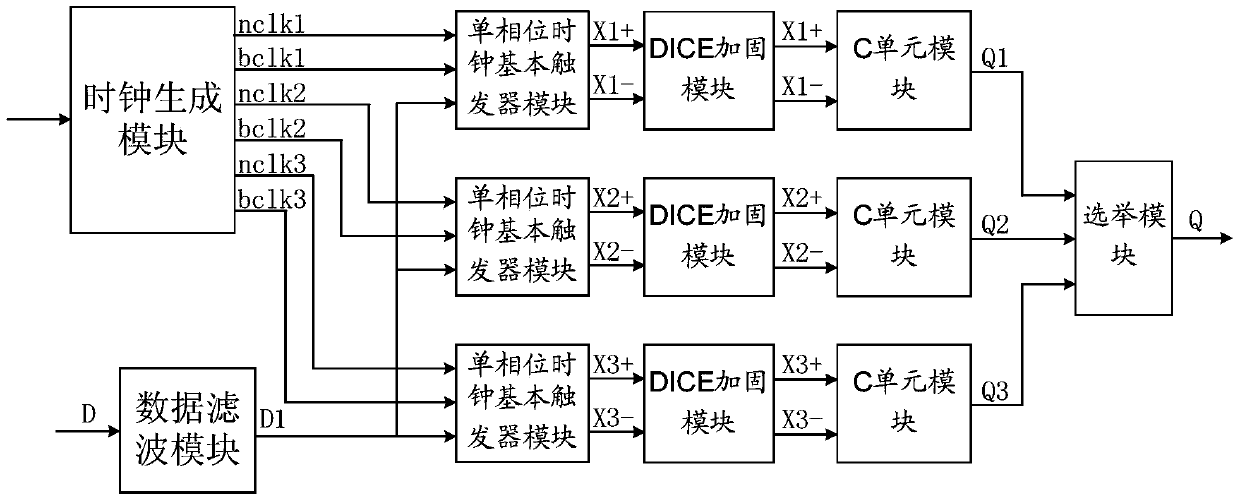

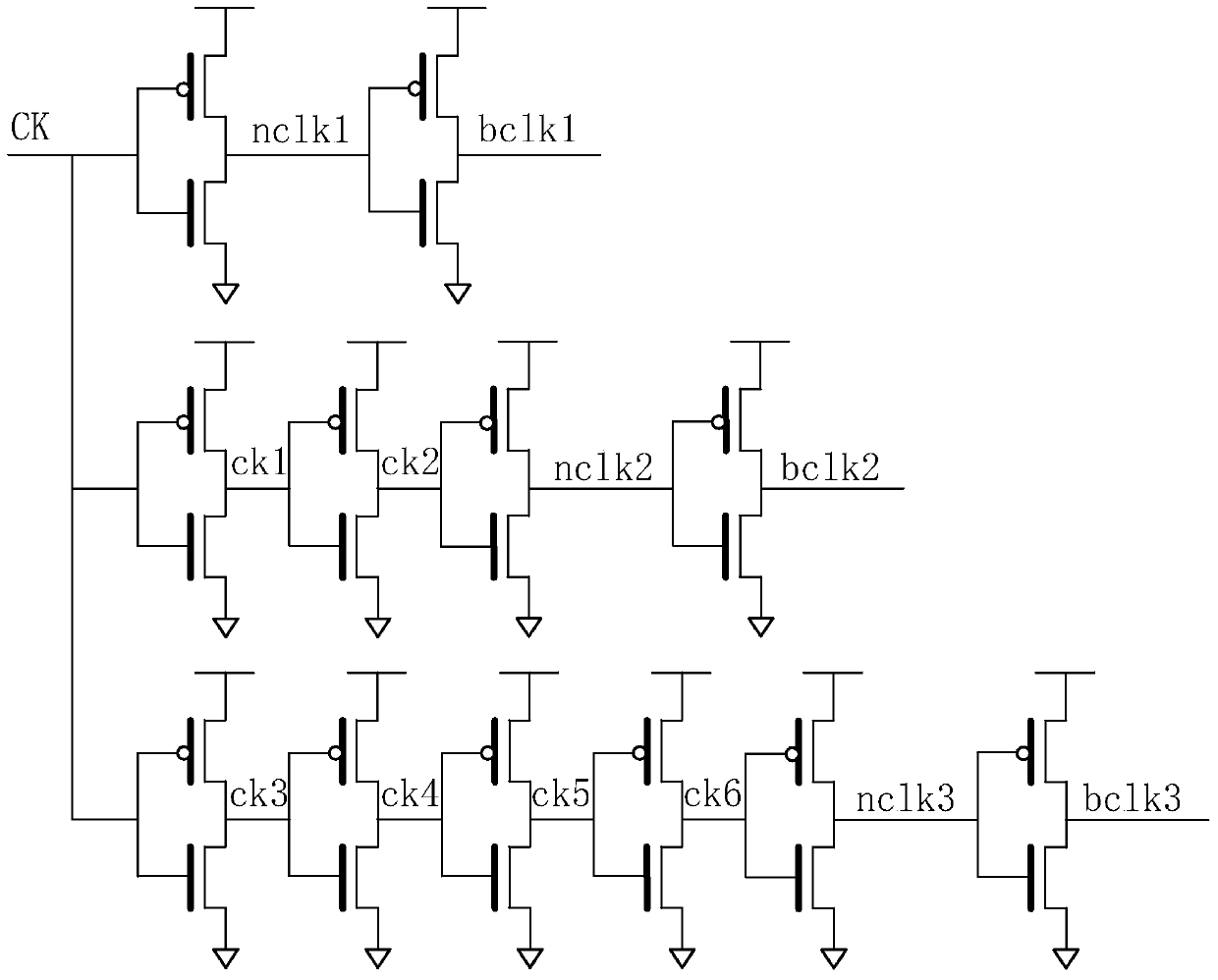

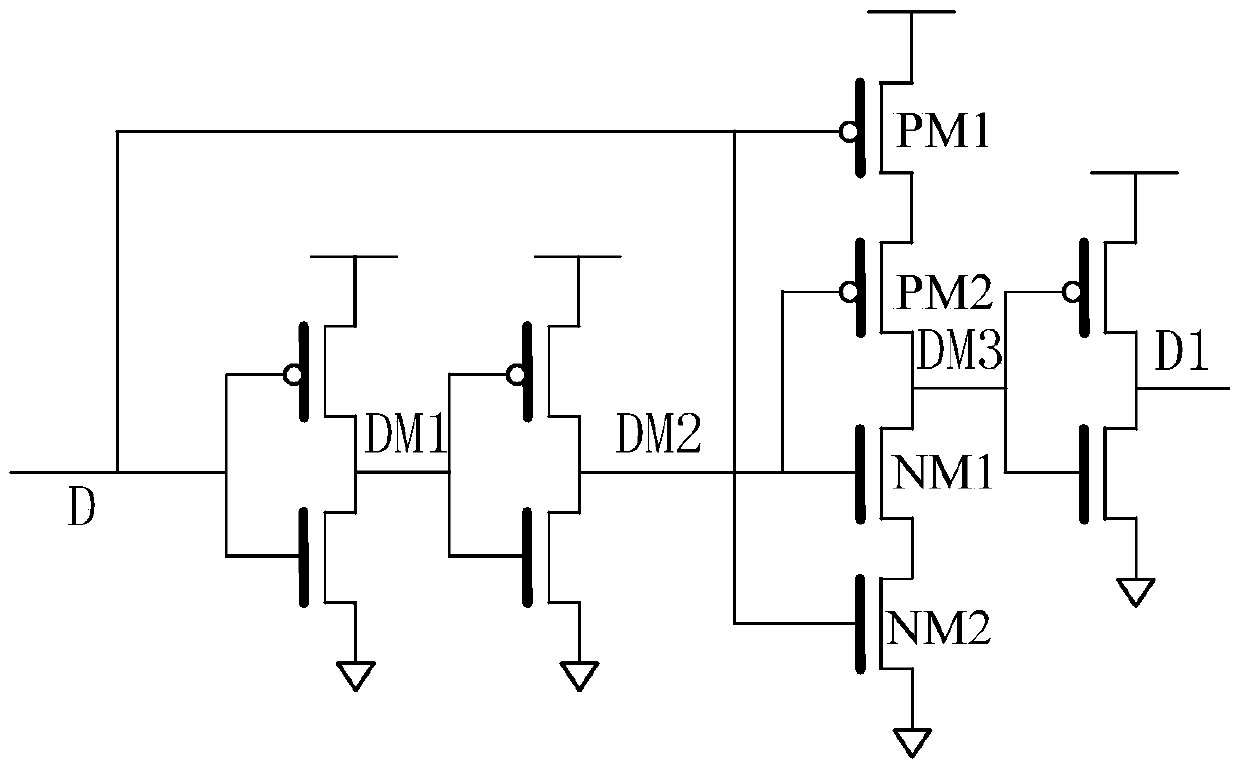

A Radiation Resistant Flip-Flop Circuit Structure Based on Single Phase Clock

ActiveCN105141291BSmall area overheadReduce power consumptionElectric pulse generator circuitsComputer moduleComputer science

A radiation-resistant flip-flop circuit structure based on a single-phase clock, including a clock generation module, a data filtering module, a first single-phase clock basic flip-flop module, a second single-phase clock basic flip-flop module, a third single-phase clock Bit clock basic trigger module, first DICE hardening module, second DICE hardening module, third DICE hardening module, first C-unit module, second C-unit module, third C-unit module and election module. The flip-flop circuit structure of the present invention adopts single-phase clock technology. Compared with the existing flip-flop technology, it not only saves the area cost and reduces power consumption, but also avoids the timing redundancy in the flip-flop of the master-slave structure, and improves the efficiency of the flip-flop. Timing performance, in addition, the trigger circuit structure of the present invention adopts a hybrid DICE+TMR structure, which improves the trigger pulse of the trigger and enhances the ability to resist single event reversal and single event pulse.

Owner:BEIJING INST OF CONTROL ENG

Low-latency and low-complexity digital kvm switcher video lossless compression method and system

ActiveCN106028029BLower latencyReduce computational complexityDigital video signal modificationComputation complexityStream data

The invention discloses a lossless video compression method and system for a digital KVM switcher having low delay and low complexity. The lossless video compression method comprises the following steps of: (1), writing frame-level coding information of a screen video image in a code stream; (2), sequentially inputting RGB data of pixels to be compressed in the screen video image; (3), calculating the prediction mode of the current pixels according to the spatio-temporal correlation; (4), calculating the coding mode of the current pixels according to the prediction mode of the current pixels; (5), writing a compression bit in the code stream according to the coding mode of the current pixels; (6), repeating the steps (2)-(5), such that coding of all the pixels in the screen video image of the current frame is completed; and (7), performing byte alignment filling of the code stream of the current frame, such that coding of the screen video image of the current frame is completed. The method disclosed by the invention is applied to compression of the screen video image of the digital KVM switcher; the compression processing delay and the code stream data volume of the screen video image can be effectively reduced under the limited calculation complexity; and simultaneously, lossless video quality can be kept.

Owner:杭州比特瑞旺电脑有限公司

A physical interface device for digital real-time simulation of power systems based on optical fiber communication

ActiveCN103472733BMeet real-time IO needsIncrease I/O scaleSimulator controlReal-time simulationElectric power system

The invention provides a digital real-time simulation physical port device of a power system based on optical fiber communication. The port device comprises a machine case, a bottom plate, a power plate, a functional plate and a liquid crystal screen, wherein the bottom plate, the power plate, the functional plate and the liquid crystal screen are located in the machine case. The bottom plate is vertical to an upper panel and a lower panel of the machine case, the power plate and the functional plate are respectively fixed through insertion grooves formed in the upper panel of the machine case, the lower panel of the machine case and the bottom plate, and the liquid crystal screen is installed on a front panel of the machine case and is connected with the bottom plate through a PCI bus. The digital real-time simulation physical port device of the power system based on optical fiber communication has the advantages of being large in port scale, high in sampling accuracy, high in data processing speed, high in synchronization precision and the like, and can meet new test requirements.

Owner:STATE GRID CORP OF CHINA +1

fuel tank level sensor

ActiveCN111103039BHigh position signal accuracyHigh resolutionLevel indicators by floatsFuel tankPhysics

The fuel tank oil level sensing mechanism and the sensor using the fuel tank oil level sensing mechanism of the present invention include a signal circuit module and a mobile module for mutual induction; the signal circuit module includes: a circuit board assembly; a processing circuit assembly, the processing circuit assembly is arranged in the circuit on the board component; the sensing component, the sensing component is arranged on the circuit board component, the sensing component is connected with the processing circuit component, and the sensing component and the mobile module sense each other; the sensing film, the sensing film is set on the circuit board component, and the sensing film covers the sensing component. The invention has high position signal accuracy and high resolution; low cost and simple structure; it ensures the stability of the position signal of the sensor in harsh working environments; the sensing film made of soft magnetic materials has low coercive force, low magnetic saturation density and high The characteristics of magnetic permeability, this kind of material can use the smallest external magnetic field and the fastest speed to achieve the maximum magnetization or magnetic saturation, and when the external magnetic field dissipates, this kind of material can demagnetize at the fastest speed.

Owner:赛卓电子科技(上海)股份有限公司

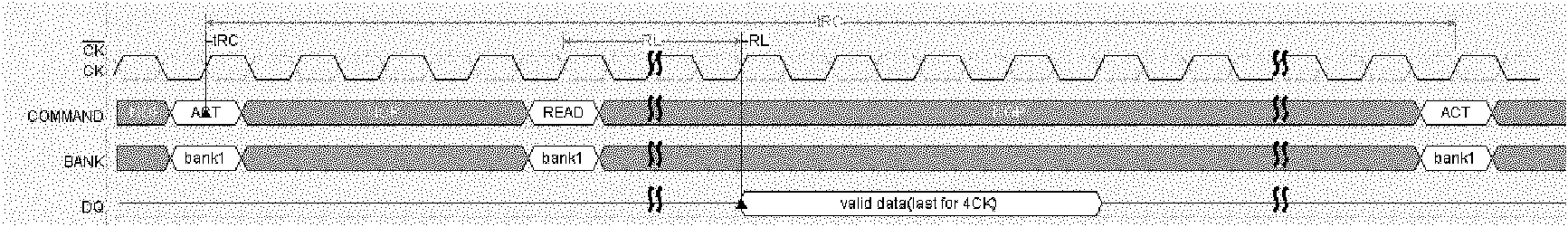

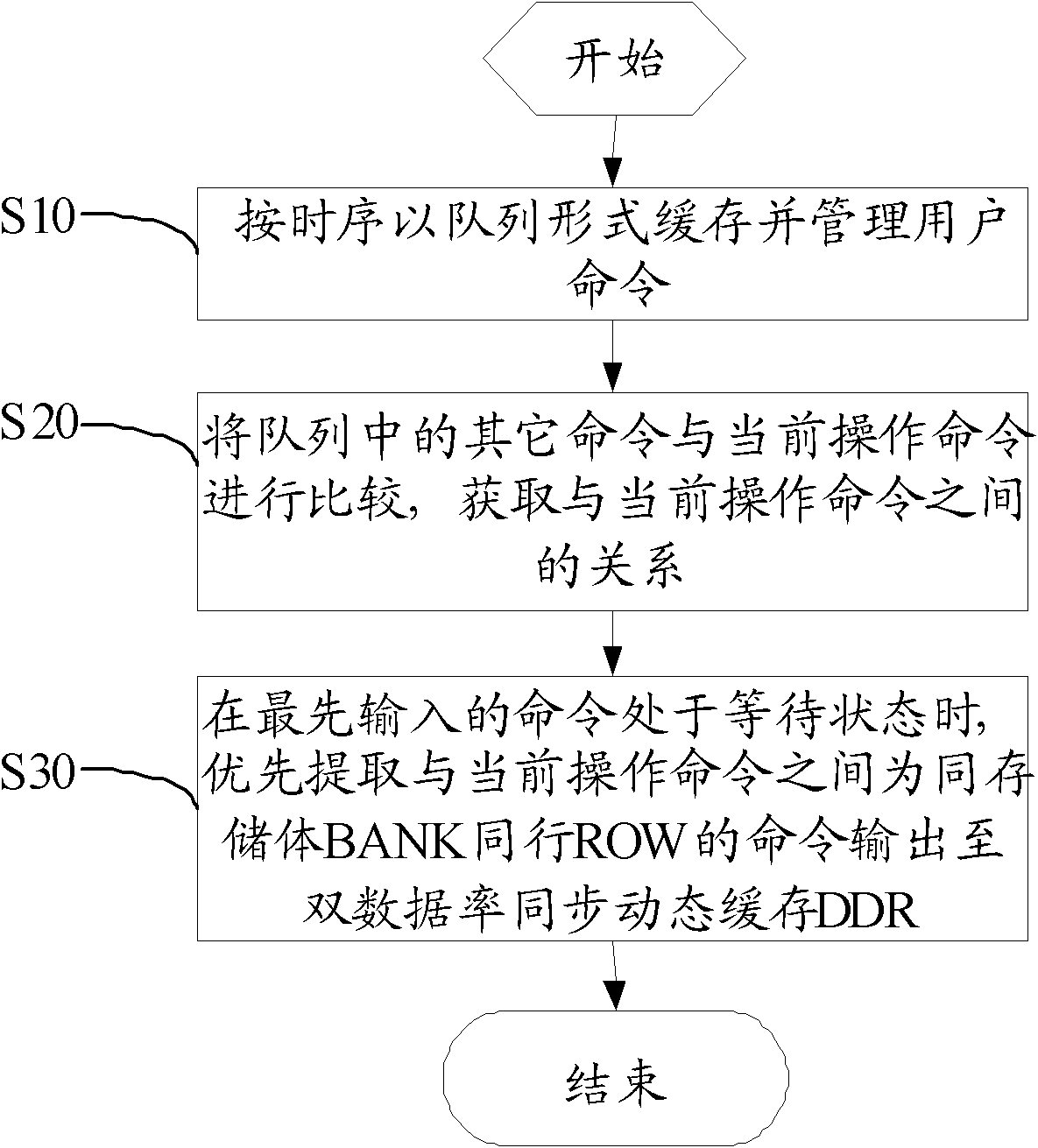

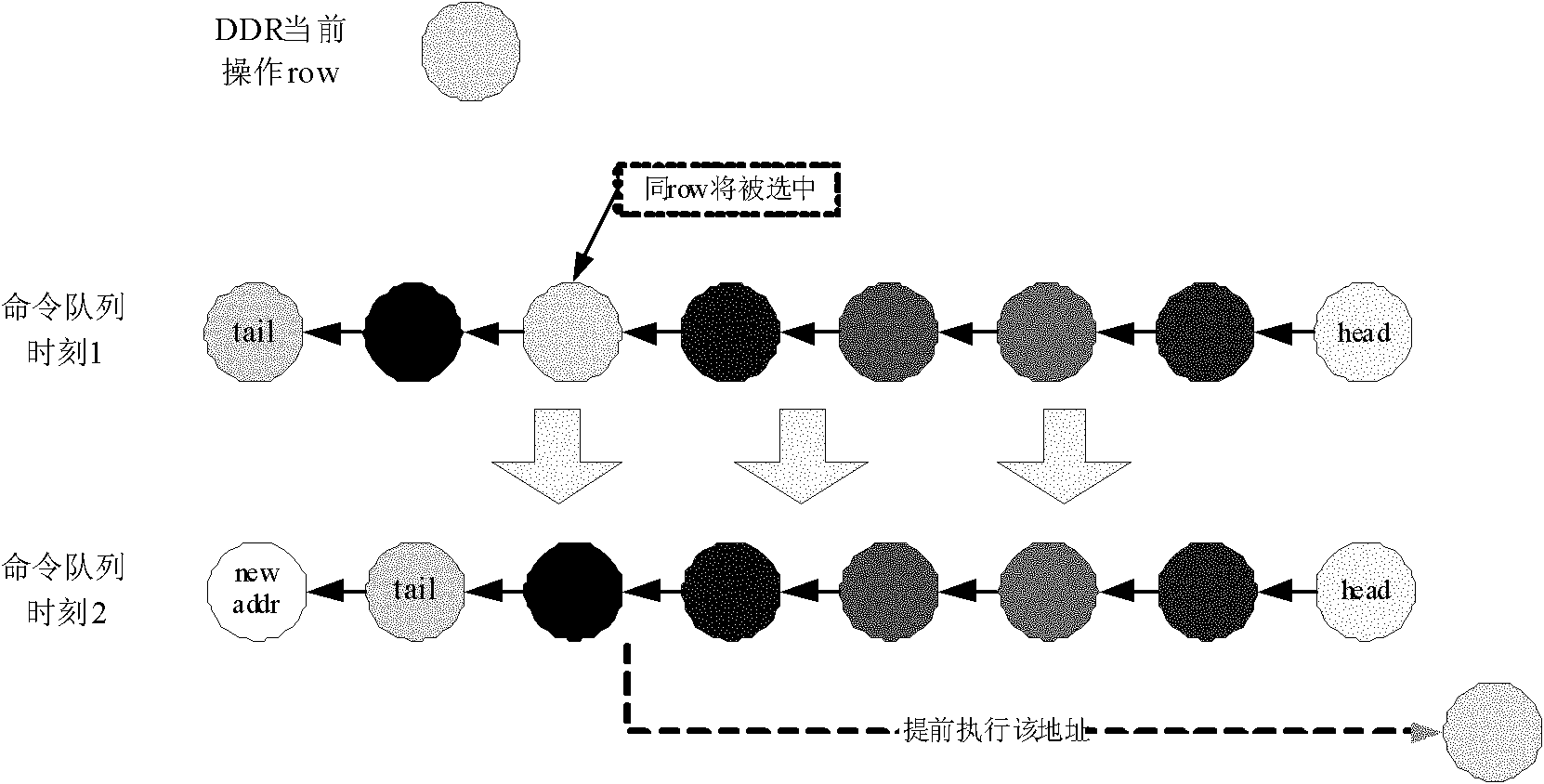

Method and device for increasing efficiency of DDR (Double Data Rate) controller

ActiveCN102456391BImprove controller efficiencyImprove efficiencyDigital storageDouble data rateWait state

The invention relates to the field of data communication and provides a method for increasing efficiency of a DDR (Double Data Rate) controller. The method comprises the following steps of caching and managing user commands in the form of queue according to a time sequence; comparing other commands in the queue with the current operation command to obtain relationships between the other commands and the current operation command; preferentially extracting a command which shares bank and row with the current operation command and outputting the command to a double data rate synchronous dynamic cache DDR when the first input command is in a waiting state. The invention also provides a device for increasing efficiency of the DDR controller. By using the device or method for increasing efficiency of the DDR controller, provided by the invention, the data output delay can be reduced while the bandwidth efficiency of the DDR is increased, and the space consumption of internal static cache is saved.

Owner:SANECHIPS TECH CO LTD

Construction method of LDPC encoder

ActiveCN107959500AOutput delay is smallSave storage spaceError correction/detection using multiple parity bitsCode conversionAlgorithmEncoder

The invention provides a construction method of an LDPC encoder, the method comprises the following steps: designing an LDPC encoding matrix for performing LDPC encoding; performing operation for an information bit part in an encoding code word and the LDPC encoding matrix, registering the obtained operation result in an encoding memorizer for outputting a check bit part, wherein the number of theencoding memorizers is determined according to the maximal column N of the encoding matrix. Through the construction method of the LDPC encoder, a storage space of the LDPC encoder is enabled to be small as much as possible, but design is not too difficult, and universality of different code words is also considered.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

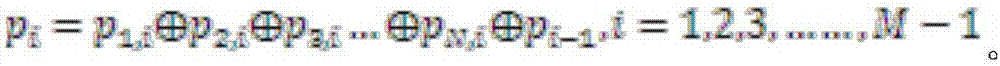

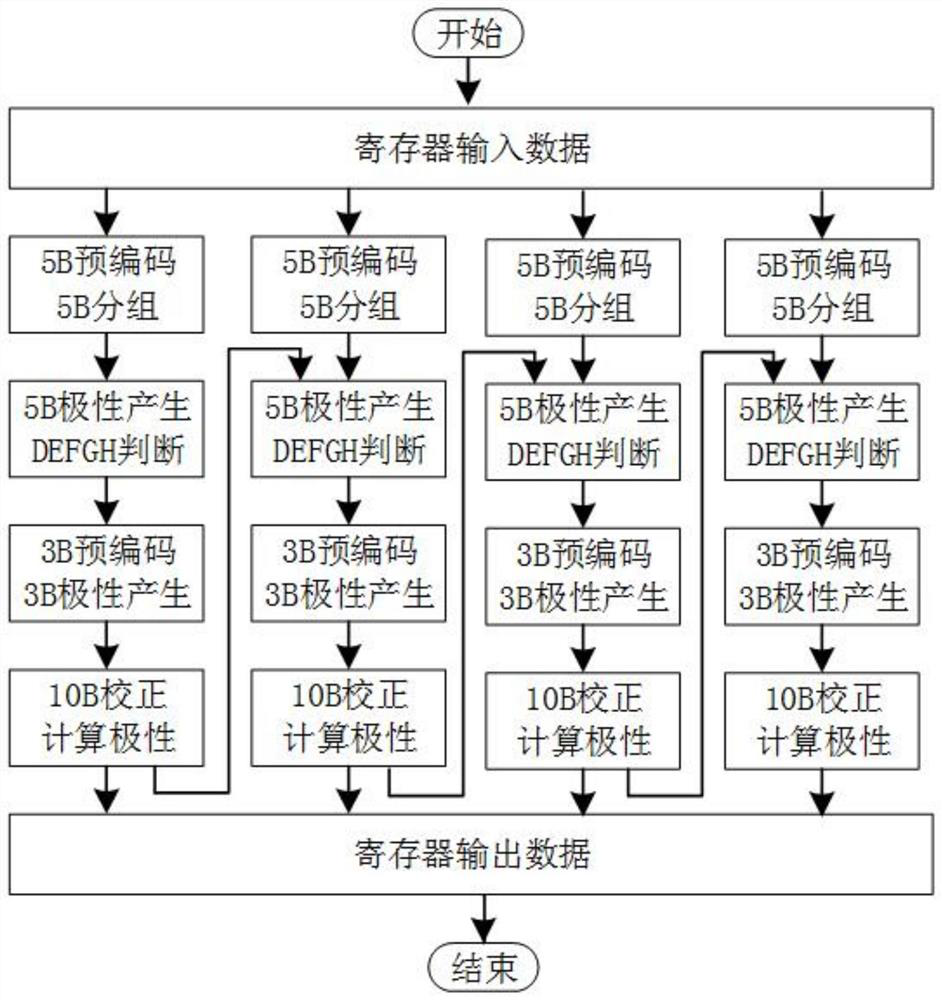

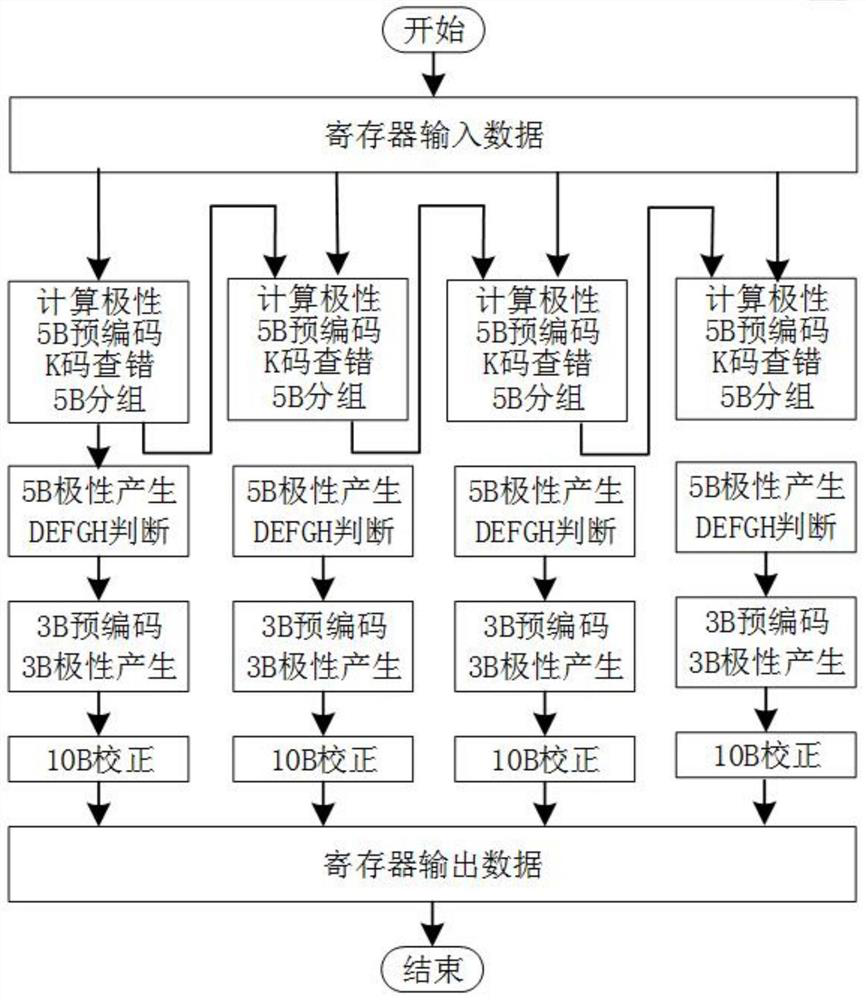

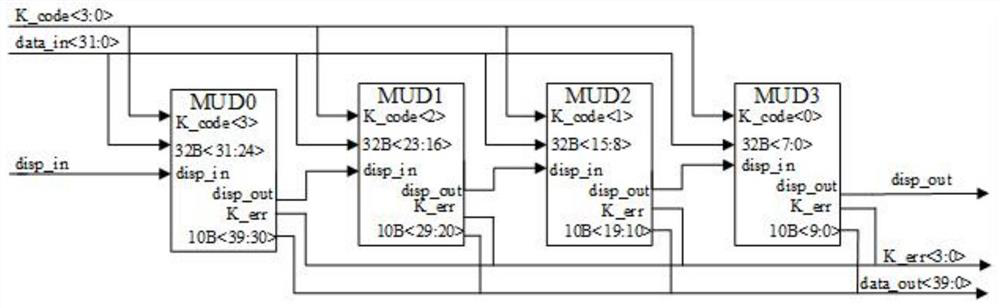

A method and device for low-latency 8b/10b encoding

ActiveCN111030953BReduce couplingOutput delay is smallSynchronous/start-stop systemsParallel encodingEngineering

The invention discloses a low-delay 8B / 10B encoding method and device, which improves the traditional four-channel 8B / 10B encoder, and derives the polarity generation method according to the causal relationship of the 8B / 10B encoding table. The polarity generation part is added to the traditional multi-channel encoder, which saves a lot of waiting time between the internal channels of the traditional multi-channel encoder, improves the efficiency of parallel encoding, and reduces the encoding output delay while increasing the data transmission rate. The present invention can be simply extended to low-latency 8B / 10B encoders of any channel.

Owner:58TH RES INST OF CETC

LDPC encoder

ActiveCN107959501AOutput delay is smallSave storage spaceError correction/detection using multiple parity bitsCode conversionStatic random-access memoryControl store

The invention provides an LDPC encoder. The LDPC encoder comprises encoding memories (N random access memories), a memory controller, an operator, a delay module and a combine module; the encoding memories store a set LDPC encoding matrix and an LDPC code table; the memory controller is used for conducting read-write control over the N RAMs in parallel; the operator is used for conducting operation on the information bit part in encoding codewords and the LDPC encoding matrix; the delay module expresses to conduct necessary delay on the input information bit part and is used for allowing the generated check bit part to be capable of being continuously output with the information bit part; the combine module is used for combining the information bit part with the check bit part and then output the combined part; and operation results obtained by the operator are registered in the encoding memories, and the number of the encoding memories is determined by the maximum column N of the encoding matrix. Accordingly, the memory space of the LDPC can be as small as possible, the design difficulty cannot be too high, and the universality of different codewords also can be considered.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

A real-time driving system and method for a target simulator based on a graphics card DVI interface

ActiveCN107305697BOutput delay is smallImprove Simulation Confidence3D-image renderingGraphic cardGraphics workstation

The present invention discloses a target simulator real-time drive system based on a DVI interface of a graphics card. The system comprises: a DVI transmission interface, used for establishing a data communication with a graphic workstation and a target simulator; a synchronous transmission control module, used for sending a simulation start signal to a dynamic scene image simulation module based on a field frequency signal output by the DVI transmission interface, and establishing synchronous data transmission with the target simulator; and the dynamic scene image simulation module, used for performing simulation analysis on to-be-tested dynamic scene data acquired from an external device based on the simulation start signal, and storing simulation image data into a frame cache. The present invention further discloses a target simulator real-time drive method based on a DVI interface of a graphics card. The technical scheme provided by the present invention shortens radiation scene output delay, ensures delay stability and thus greatly improves confidence of semi-physical dynamic scene simulation.

Owner:BEIJING SIMULATION CENT

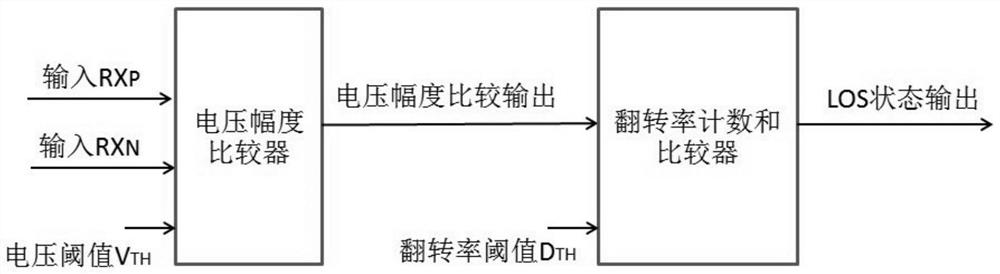

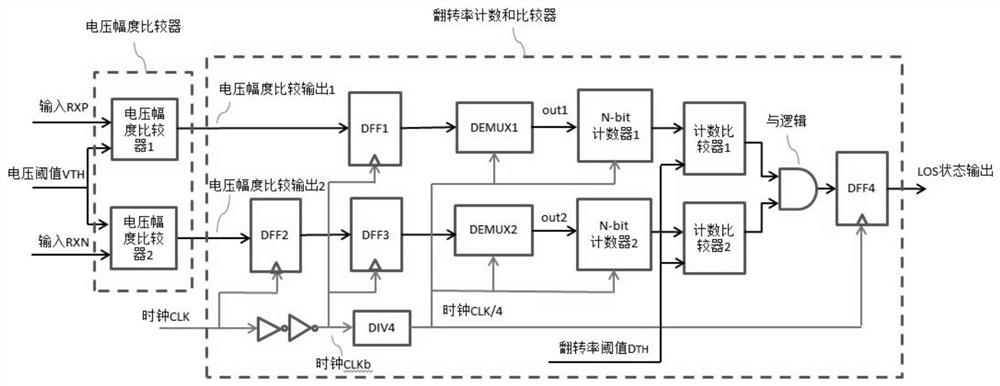

High-speed serial signal loss detection circuit

ActiveCN112345820AAvoid misjudgment of short-to-high missing state as normalOutput delay is smallCurrent/voltage measurementEnergy efficient computingVoltage amplitudeComparators circuits

The invention discloses a high-speed serial signal loss detection circuit which comprises a voltage amplitude comparator and a turnover rate counting and comparing circuit. Dual judgment of the voltage amplitude comparator and the turnover rate counting and comparing circuit is adopted, the condition that the loss state of the input signal from short circuit to high level is judged to be normal bysingly using the voltage amplitude comparator is avoided; meanwhile, the signal loss detection circuit can directly process low-amplitude normal signals, the circuit module contained in the signal loss detection circuit can work when high-frequency signals are inputted, the output delay of detection results is extremely small, and the low-delay alarm requirements of various communication protocols can be met.

Owner:CHENGDU SINO MICROELECTRONICS TECH CO LTD