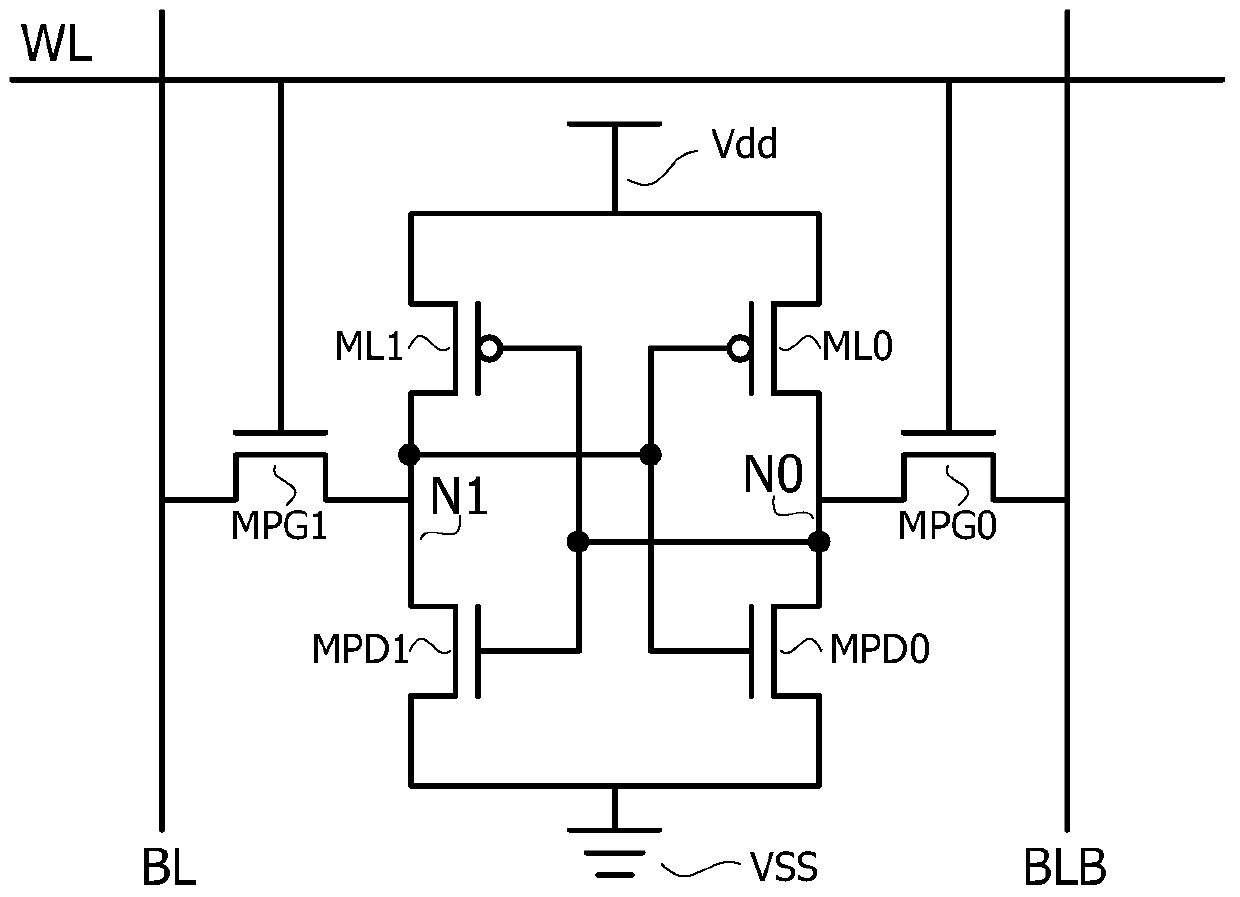

Circuit and method for suppressing negative voltage of bit line under high power supply voltage

A power supply voltage and negative voltage technology, applied in the electronic field, can solve problems such as voltage difference, leakage, gate oxide layer breakdown, etc., and achieve the effect of avoiding damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

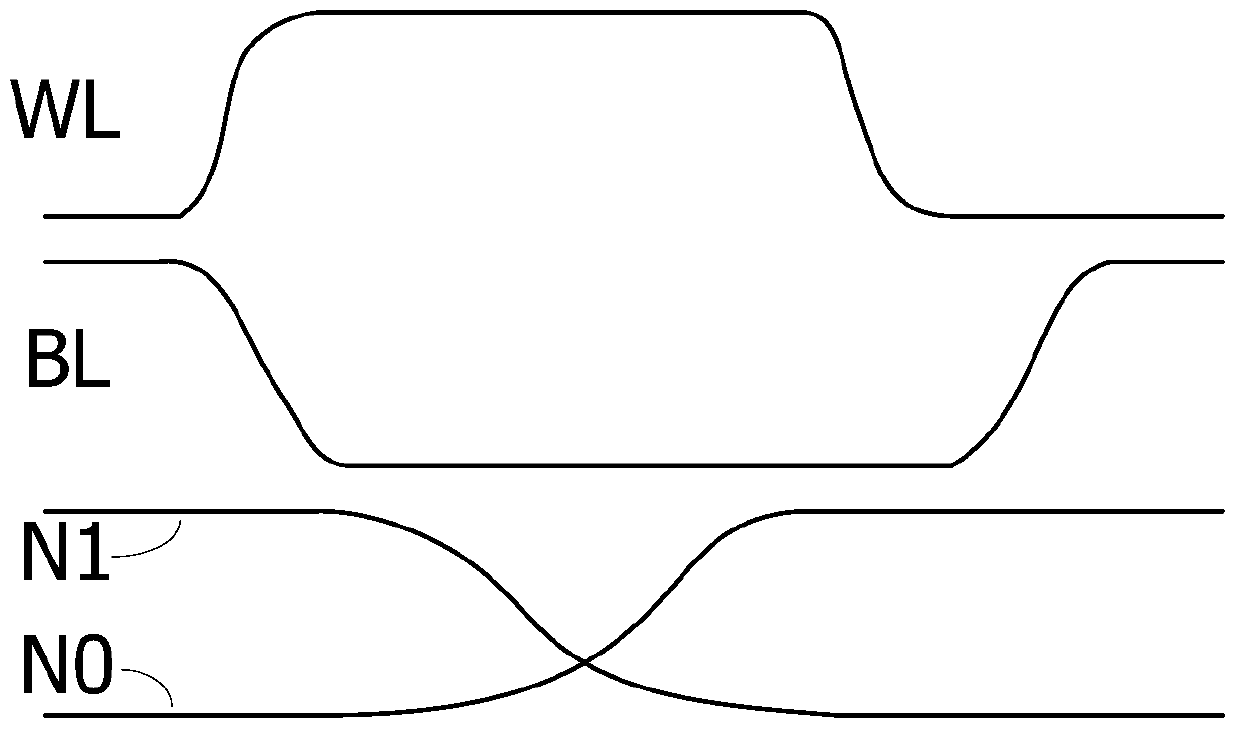

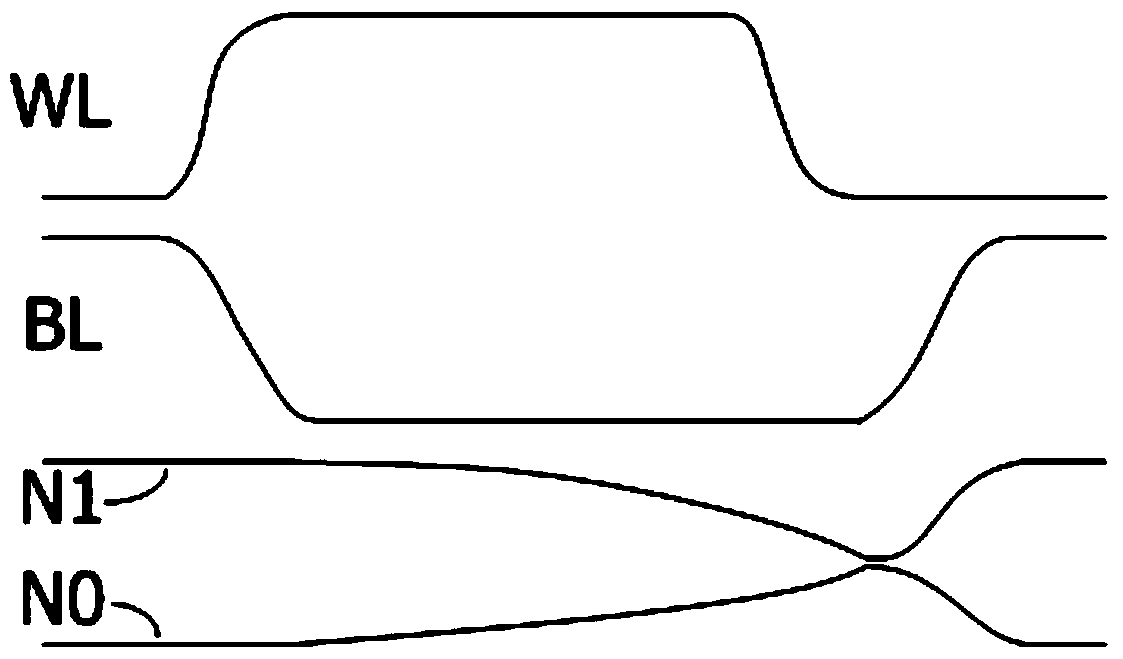

[0129] A specific embodiment, taking the step of writing data 0 as an example: refer to Figure 9 ,include:

[0130] Step s11, the first bit line BL is pulled down to the ground voltage VSS;

[0131] Step s12, the first external signal NBSTEB changes from high level to low level, and the first signal NBST0 changes from high level to low level after a delay of the first set time t1 and is transmitted on the first bit line BL Coupling generates a negative voltage; the first write enable signal WT0 delays the second set time t2 and disconnects the connection between the first bit line BL and the ground voltage. When the power supply voltage is a high power supply voltage, it is coupled on the first bit line BL After obtaining the negative voltage, disconnect the first bit line BL from VSS of the ground voltage to obtain the ground voltage VSS on the first bit line BL;

[0132] Step s13 , the word line of one of the N SRAM memory cells is selected, the first bit line BL is connect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com