Multi-processor system and clock synchronization method

A multi-processor system and clock synchronization technology, applied in the computer field, can solve problems such as small margin and hidden stability problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

[0042] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention more clear, the technical solutions in the embodiments of the present invention will be clearly described below in conjunction with the drawings in the embodiments of the present invention.

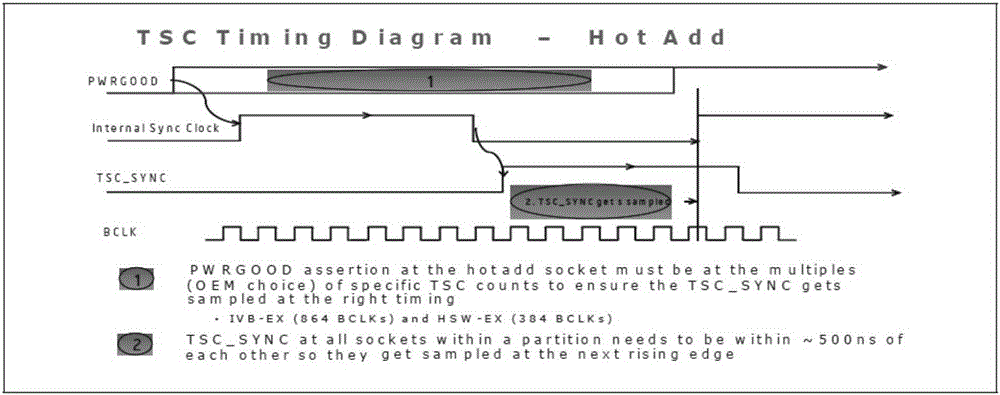

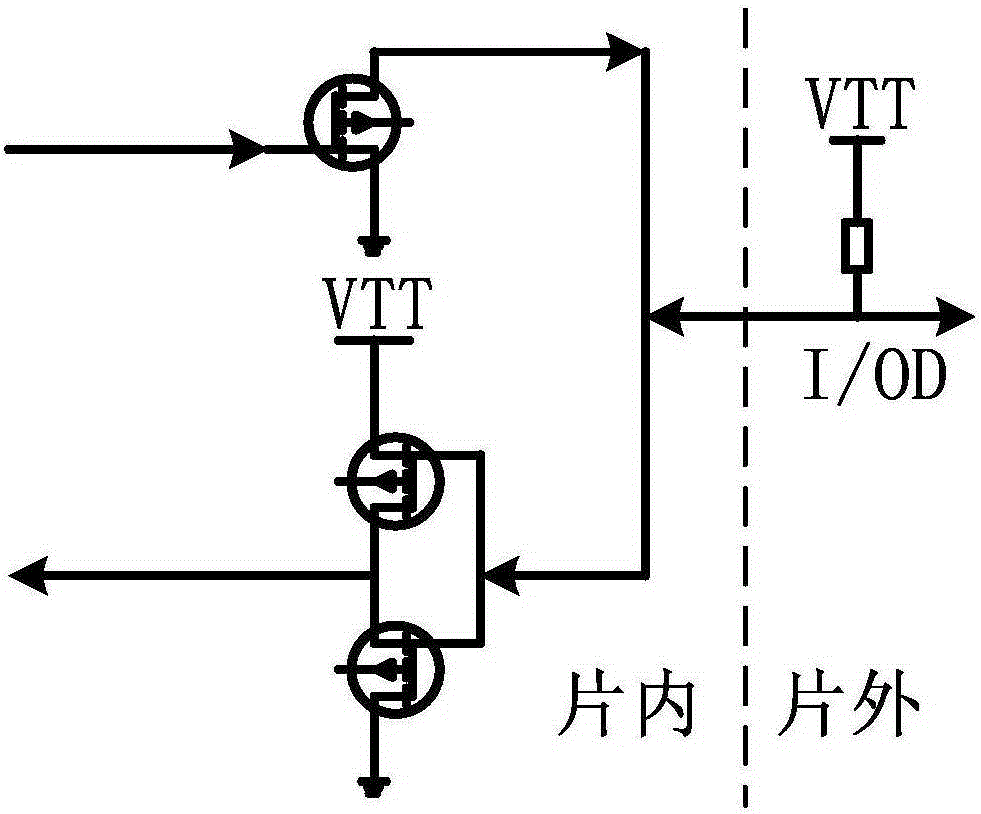

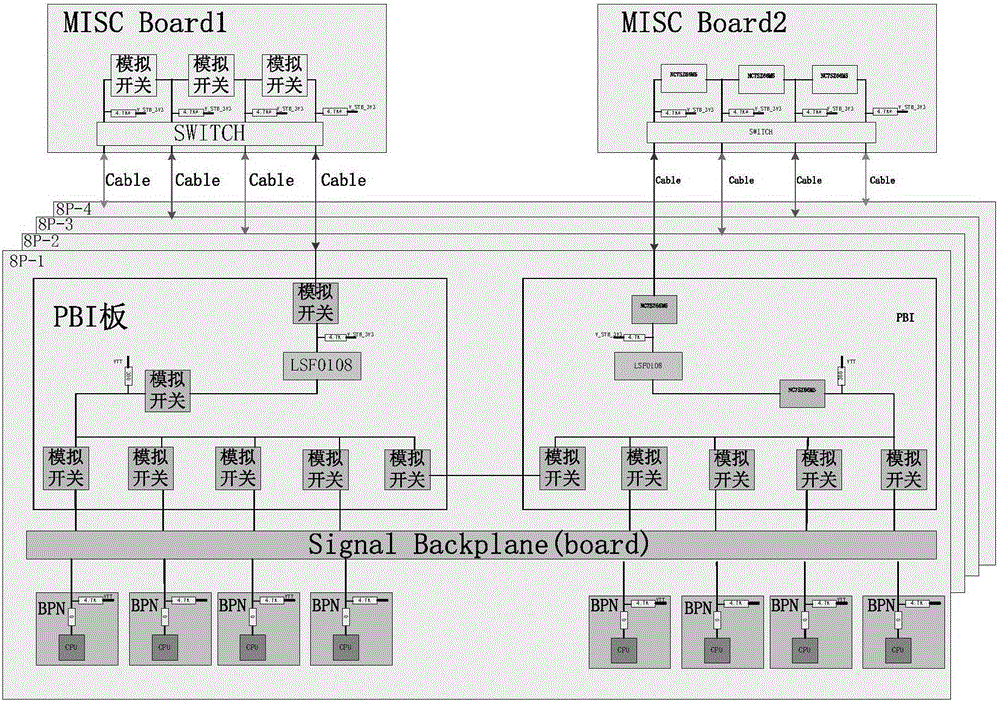

[0043] The present invention proposes a solution to the problems of low TSC clock synchronization success rate and poor stability caused by too long TSC_SYNC direct link in the existing multiprocessor system. , the TSC_SYNC bus is divided into multiple small domains, and the main processor sends a synchronization signal to control the programmable logic device to synchronize the signals on the TSC bus. The time difference between the rising edge of the TSC waveform and each CPU ensures that the system after hot plugg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More