Hybrid scheduling bus arbiter and arbitration method

A bus arbitration and hybrid scheduling technology, applied in instruments, electrical digital data processing, etc., can solve the problems of lack of priority scheduling, lack of comprehensive scheduling schemes, etc., to achieve the effect of increased application flexibility, less resource overhead, and simple circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

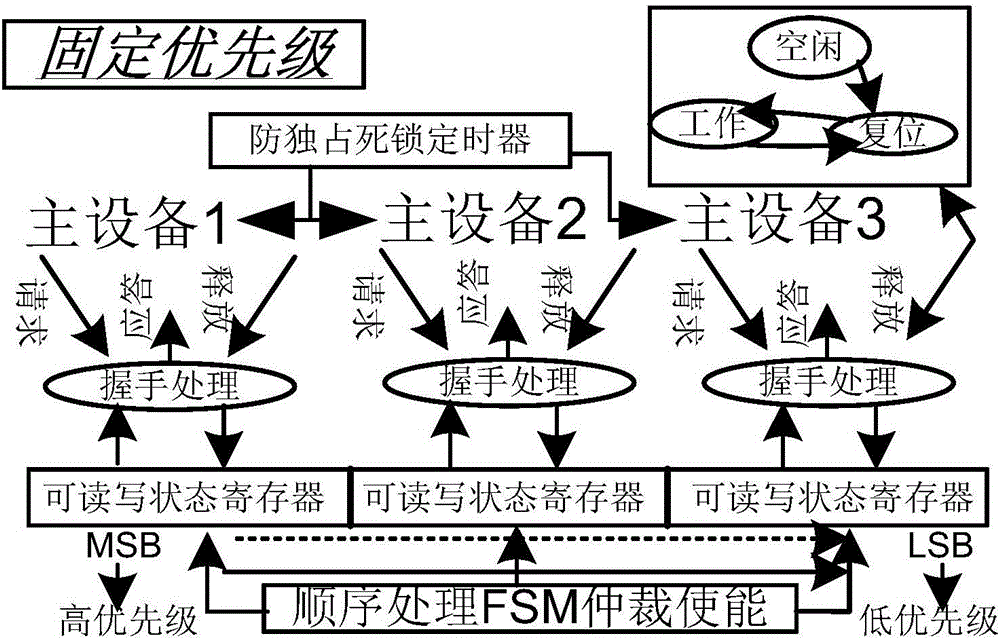

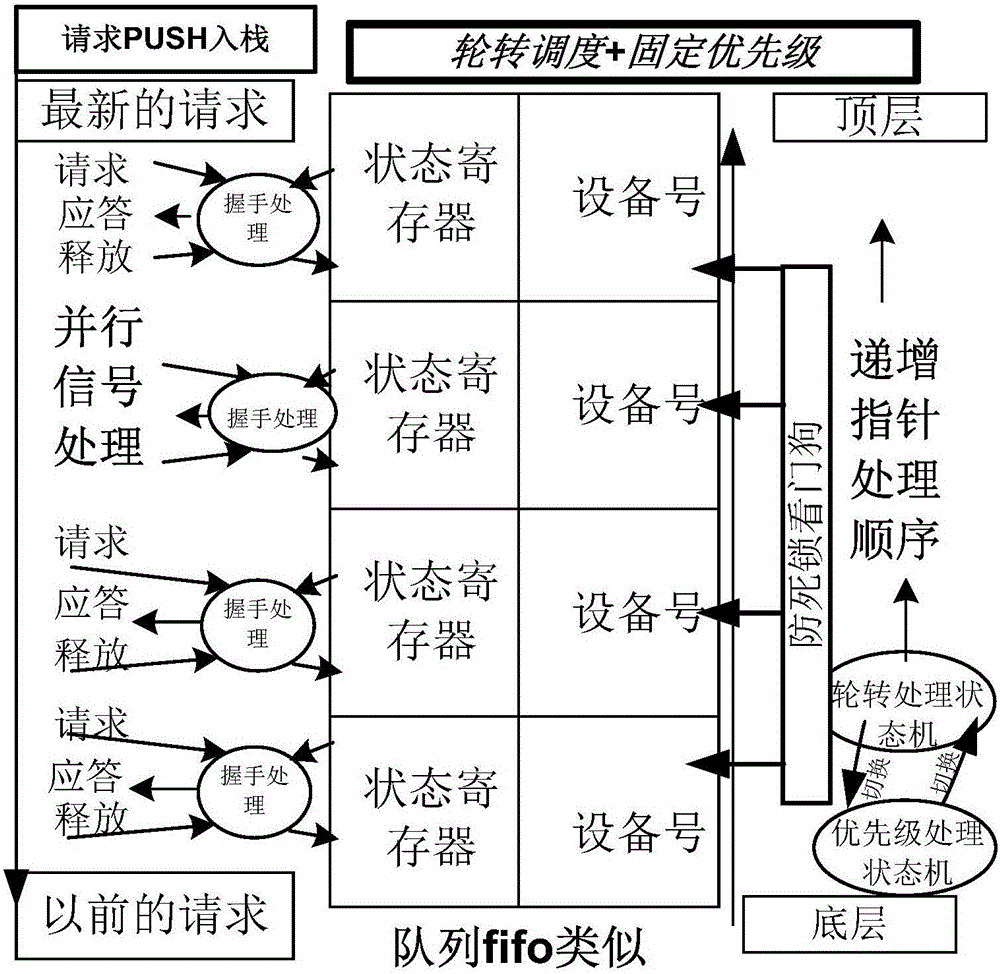

[0031] Embodiment 1: a kind of bus arbiter of hybrid scheduling, has round-robin scheduling module and fixed priority module; Round-robin scheduling module comprises a state register and round-robin scheduling state machine, and status register stores the request signal of each equipment, and round-robin scheduling state machine According to the round-robin scheduling order, the request signal of the current device is arbitrated and judged; the fixed priority module includes a register pile and a fixed priority state machine; the register pile processes the request signal of each device in the order from the most significant bit to the least significant bit Storage, the fixed priority state machine makes an arbitration decision on the request signal of the current device according to the fixed priority order.

[0032] The status register and the register stack are both readable and writable registers. Compared with the read-only register, the readable and writable register has ...

Embodiment 2

[0037] The present invention also proposes a bus arbitration method for hybrid scheduling, including:

[0038] When the round-robin scheduling module is enabled, the round-robin scheduling order is used to arbitrate and judge the request signal of the current device; when the fixed-priority module is enabled, the fixed-priority order is used to arbitrate and judge the request signal of the current device.

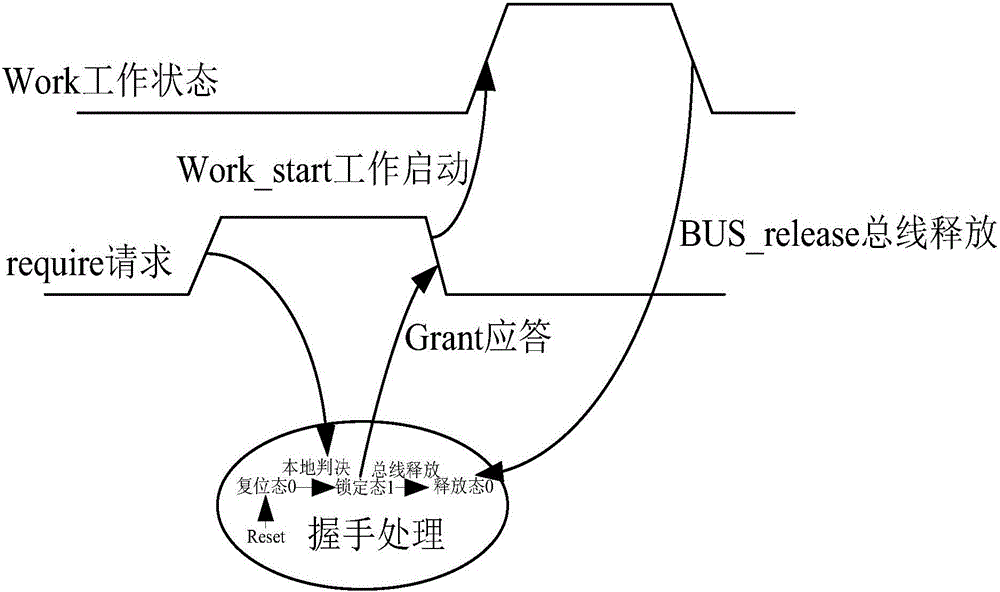

[0039] Such as figure 1 As shown, it is a timing diagram of a single handshake protocol; the arbitrator uses the "handshake protocol processing" module to realize the operations of 'bus request', 'bus response', 'work start', and 'bus release' to complete a single device and arbitration The handshake protocol of the device.

[0040]The arbiter judges the access order according to the fixed priority. The require 'request' signal comes from the first master device, and this signal is judged locally, and the handle control state machine is flipped from the reset state to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More