Assertion-Based Memory Controller Interface Timing Parameterized Verification System

A memory controller and verification system technology, applied in static memory, instruments, etc., can solve problems such as time-consuming, error-prone, and inability to guarantee the correctness of timing verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0101] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

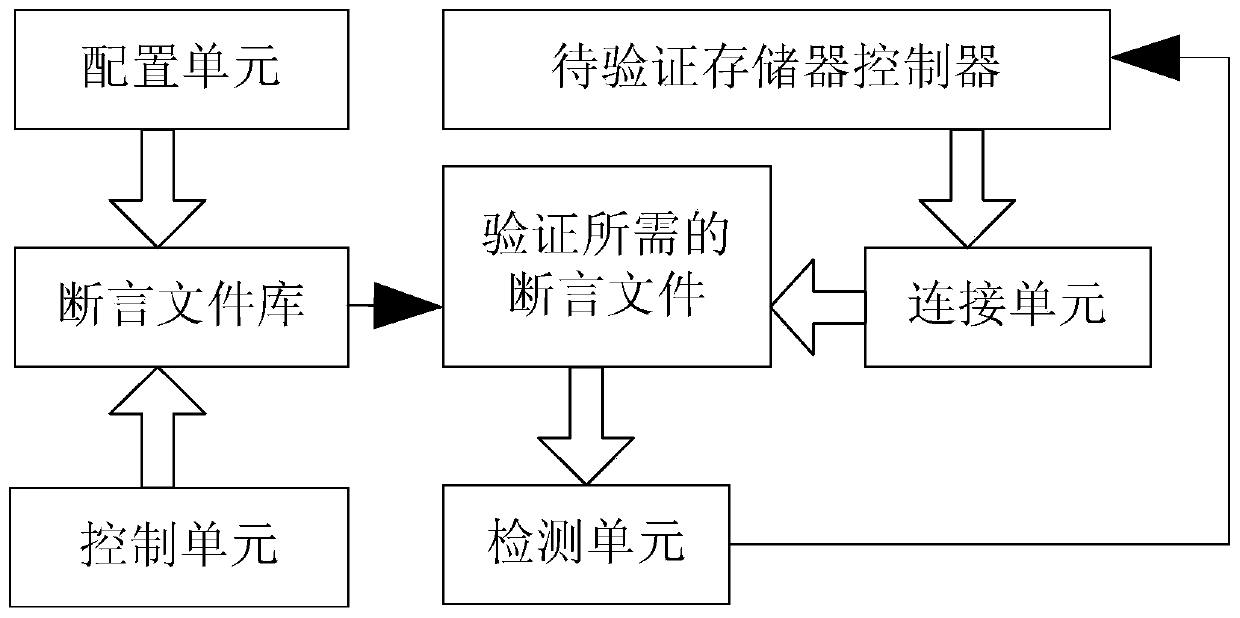

[0102] Such as figure 1 Shown is a schematic diagram of the verification system. It can be seen from the figure that the assertion-based memory controller interface timing parameterized verification system includes a configuration unit, a control unit, an assertion file library, assertion files required for verification, a memory controller to be verified, and a connection unit , Detection unit:

[0103] Configuration unit: manually enter configuration parameters, and transfer the configuration parameters to the assertion file library; where the configuration parameters include:

[0104] type_prom is whether to generate a prom type assertion;

[0105] type_sram is whether to generate sram type assertion;

[0106] type_sdram is whether to generate sdram type assertion;

[0107] bw_prom is the bit width of prom memory;

[0108] bw_sram is the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More