Small signal impedance modeling method for second-order generalized integrator-phase locked loop (SOGI-PLL)

A technology of second-order integration and modeling method, applied in the direction of AC network circuits, electrical components, single-network parallel feeding arrangements, etc., can solve a large number of Fourier transforms, convolutions, and can not truly respond to single-phase phase locking Loop impedance characteristics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

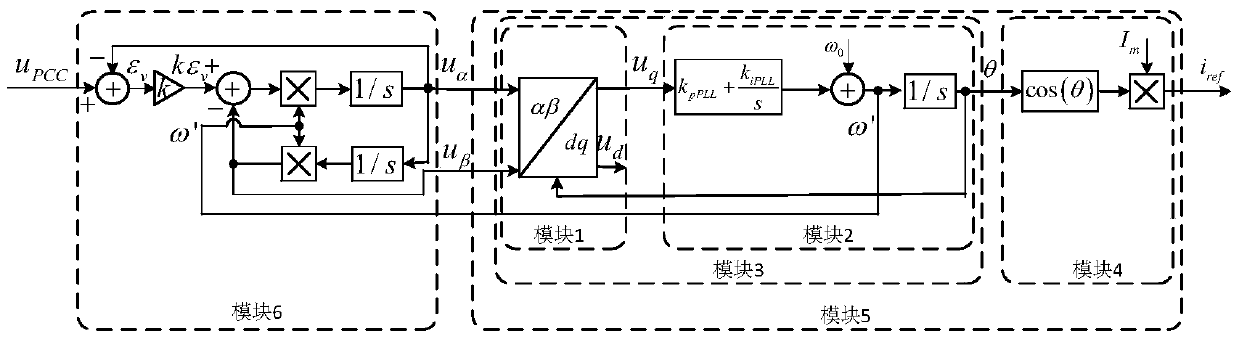

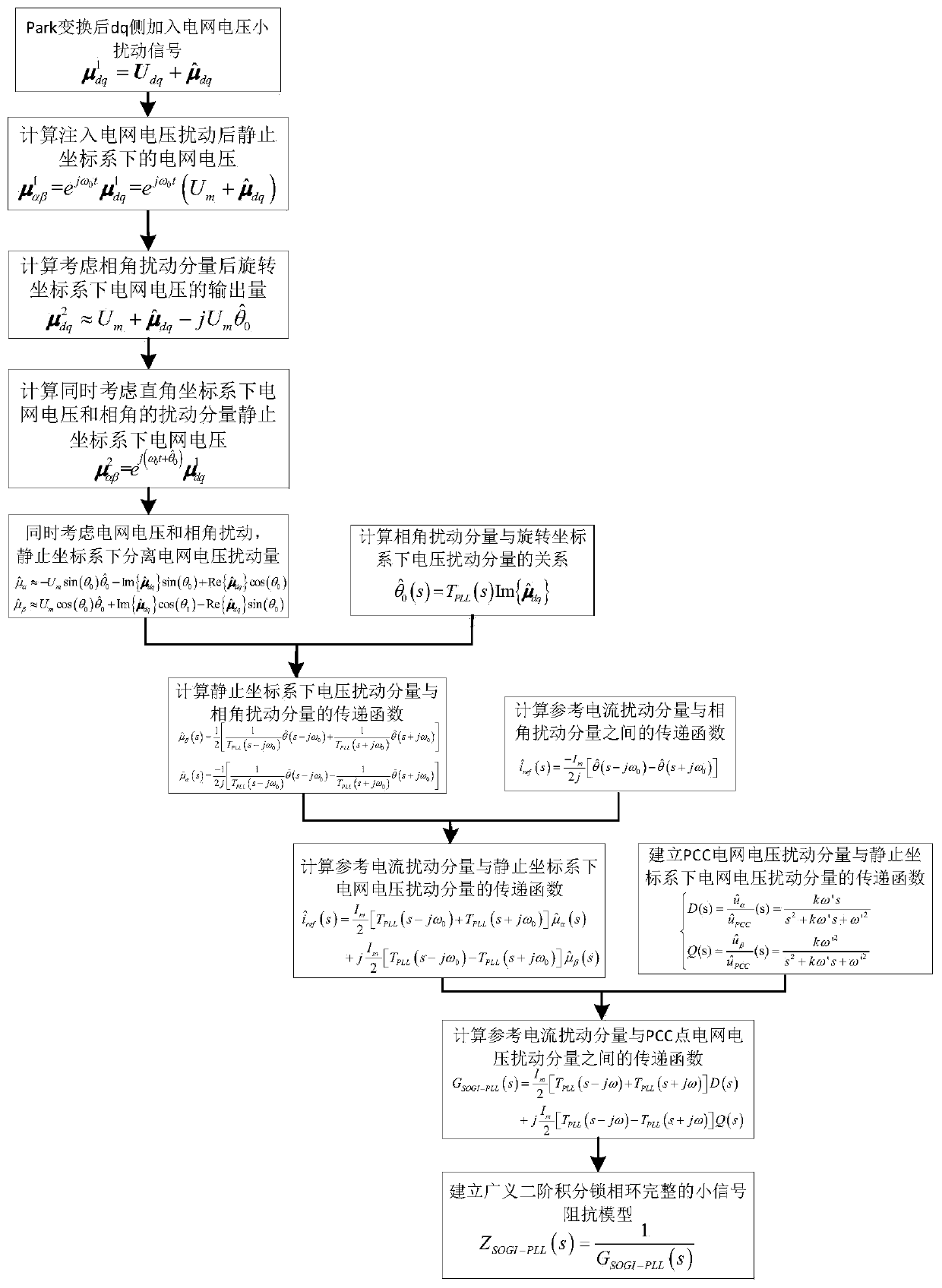

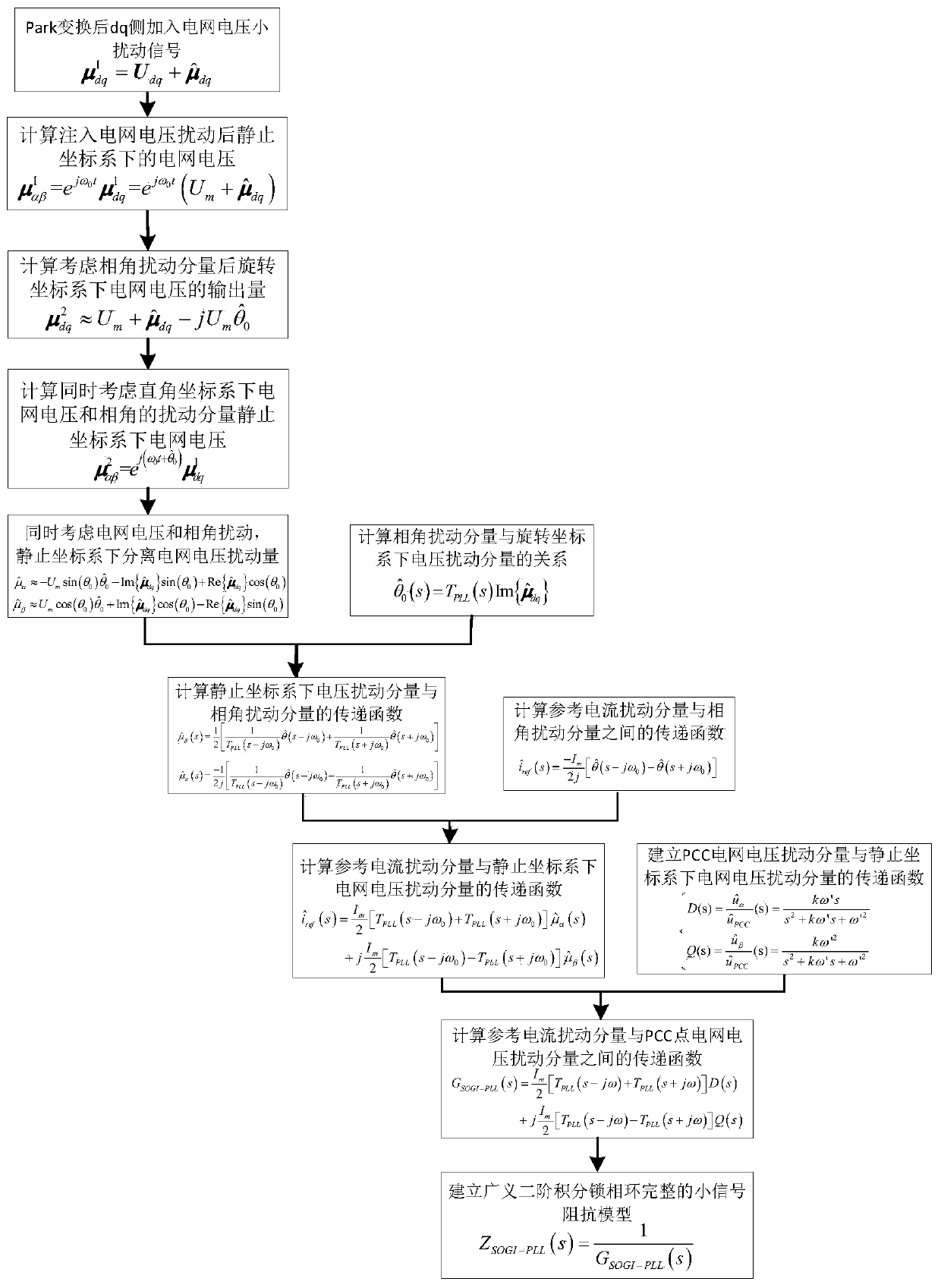

[0082] In order to more specifically illustrate the modeling process of the generalized second-order integral phase-locked loop small-signal model provided by the present invention, it will be described below in conjunction with the accompanying drawings.

[0083] Such as figure 2 As shown, the small-signal impedance modeling flowchart of the generalized second-order integral phase-locked loop of the present invention, the modeling method of the present invention comprises the following steps:

[0084] Step I: Determine the relationship between the input grid voltage in the stationary coordinate system and the small output signal in the rotating coordinate system;

[0085] Step II: Establish the transfer function of the virtual axis output disturbance component and the phase angle disturbance component under the rotating coordinate system;

[0086] Step III: establish the transfer function of the grid voltage disturbance component and the phase angle disturbance component un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More