Time test circuit and time test method

A technology for testing circuits and time, applied in the direction of electrical unknown time interval measurement, devices and instruments for measuring time interval, etc., can solve the problems of inclusions, circuit errors, long rising edge time of pulse signals, etc., so as to reduce the turnover time and avoid the impact , the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

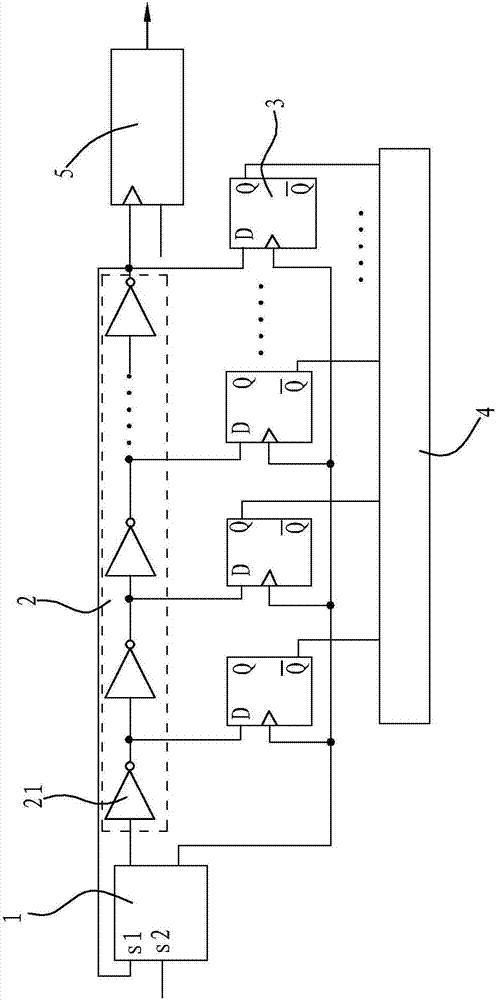

[0022] Such as figure 1 As shown, the time test circuit in this embodiment is characterized in that it includes a voltage comparator 1 , an oscillator 2 , a plurality of D latches 3 , a temperature encoder 4 and a counter 5 .

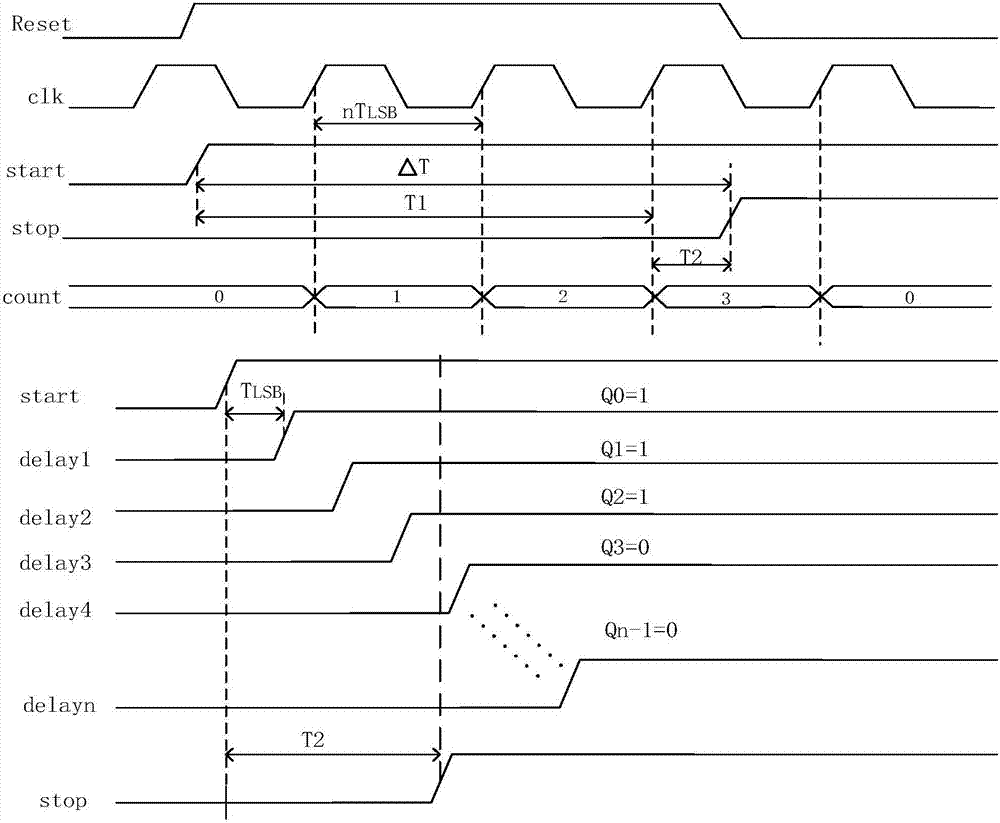

[0023] The voltage comparator 1 can be composed of a bias circuit, a differential amplifier, a common source amplifier, and a push-pull stage output circuit. Since the rising edge time of the signal output by the voltage comparator 1 is too long, the capacitance will be increased during delay propagation in the oscillator 2 The charging and discharging time will increase the delay time of the single gate delay unit 21 accordingly. Therefore, the step signal output by the voltage comparator 1 is divided to obtain a step signal with a shorter rising edge as the start of the time and the end of the time. Stop internal tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More