Semiconductor device failure analysis sample and preparation method thereof, and failure analysis method

A failure analysis sample and failure analysis technology, which is applied in the field of semiconductor device failure analysis samples and their preparation, can solve the problems of uneven overall height of the surface of the sample 10, large differences in expansion coefficients, and large gradients of grinding layers, etc., to achieve improved preparation The effect of success rate, reduction of operating time, and reduction of grinding difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] In order to make the purpose and features of the present invention more obvious and understandable, the specific implementation of the present invention will be further described below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

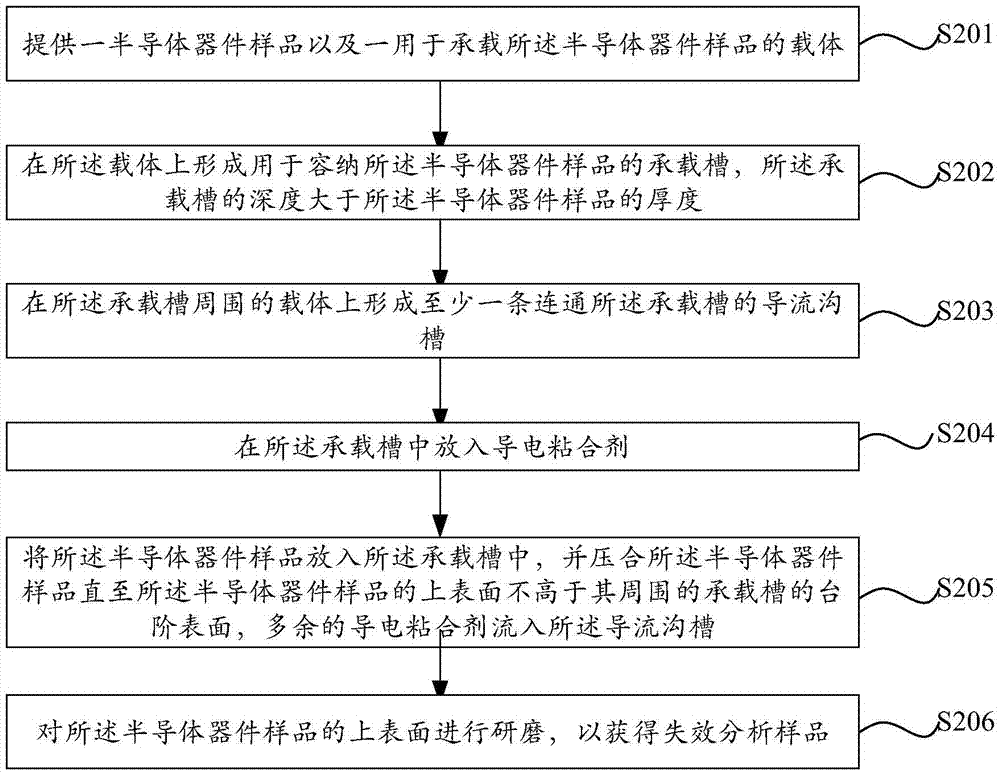

[0063] Please refer to figure 2 , this embodiment proposes a method for preparing a semiconductor device failure analysis sample, including:

[0064] S201, providing a semiconductor device sample and a carrier for carrying the semiconductor device sample;

[0065] S202, forming a bearing groove for accommodating the semiconductor device sample on the carrier, the depth of the bearing groove being greater than the thickness of the semiconductor device sample;

[0066] S203, forming at least one diversion groove communicating with the bearing groove on the carrier around the bearing groove;

[0067] S204, placing a c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More