Clock circuit and clock signal transmission method thereof

A clock circuit and clock signal technology, which is applied in the direction of reducing power, logic circuits, and generating/distributing signals through control/clock signals, can solve the problems of long clock signal propagation path, clock delay and large power consumption, and achieve shortening Effect of clock path, reduction of clock error, and reduction of transmission delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

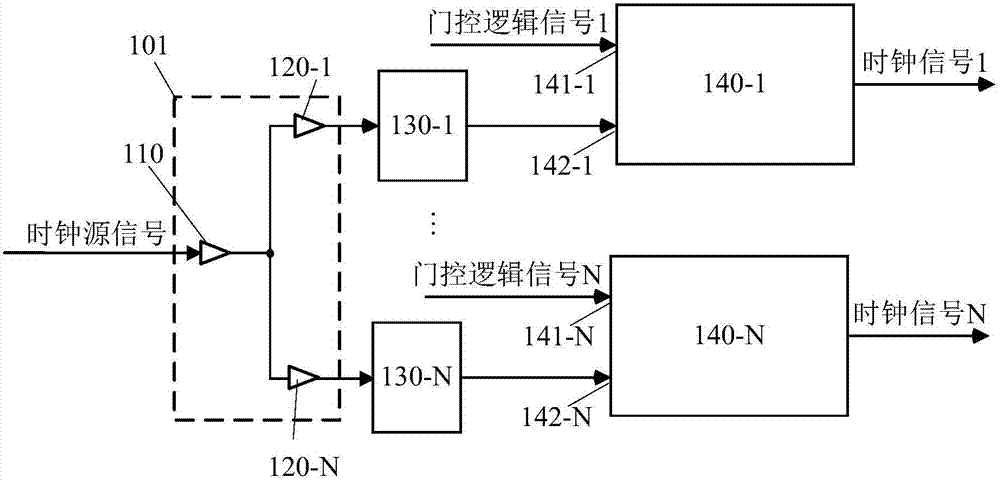

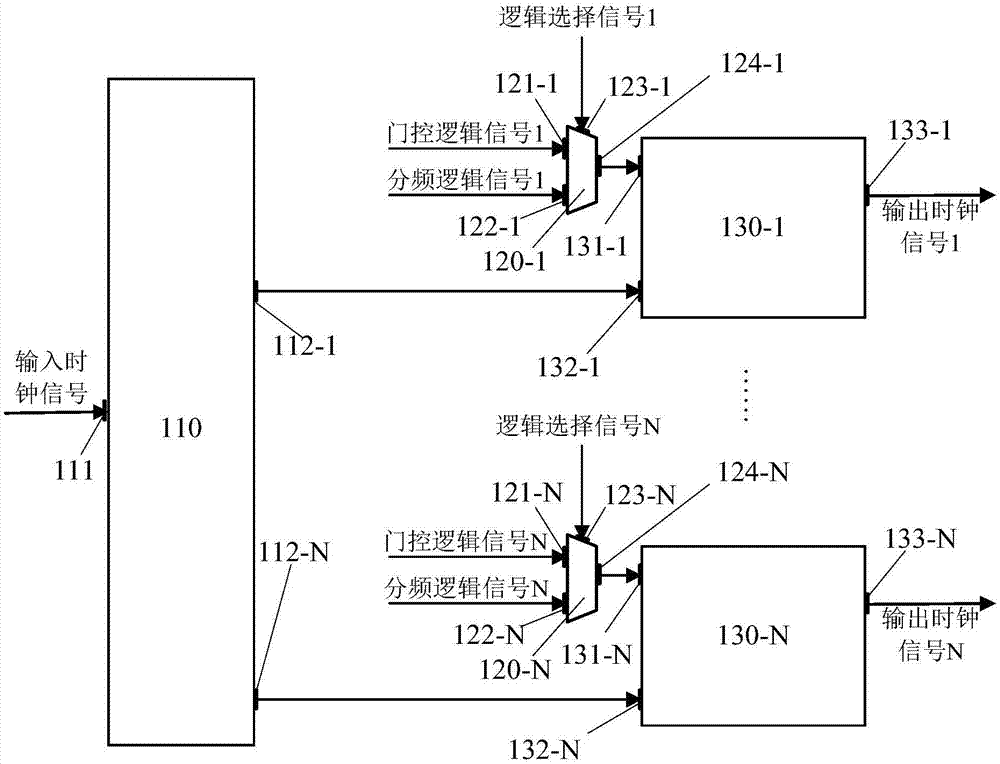

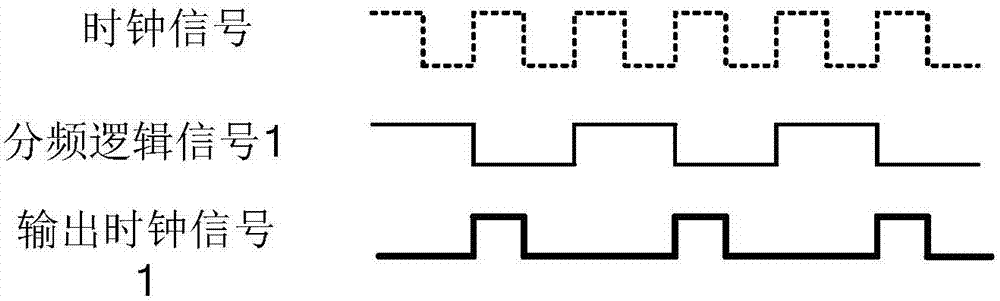

[0038] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0039] The application scenarios of the clock circuit in the embodiment of the present invention will be described below with an example. A digital integrated circuit integrating the clock circuit of the embodiment of the present invention can constitute a processor. The processing of the processor needs to be driven by periodic clock pulses, that is, after the clock signal is input to the clock circuit, it is transmitted through the clock circuit, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More