Field effect transistor

A field-effect transistor, nitride semiconductor technology, applied in transistors, semiconductor devices, electric solid-state devices, etc., can solve the problems of unstable operation and long distance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

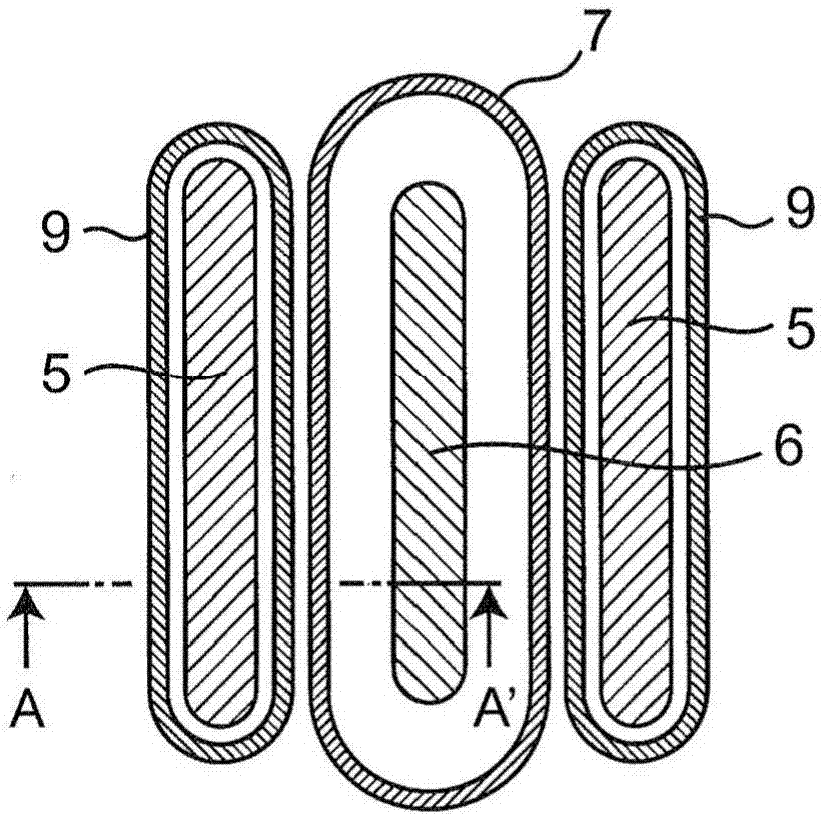

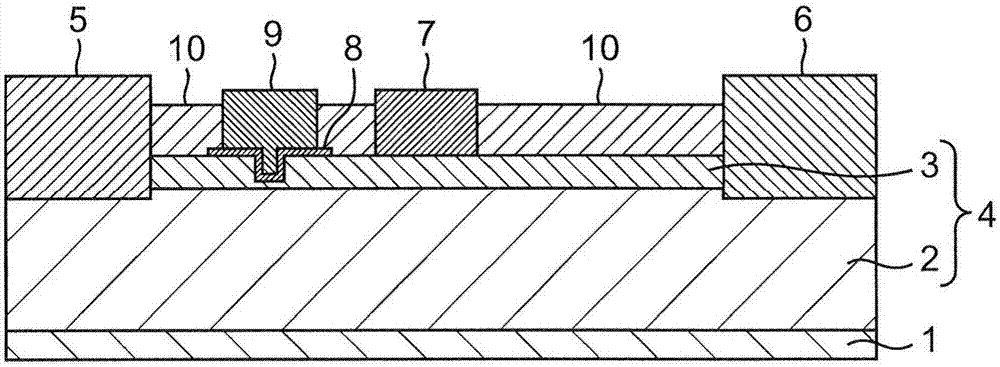

[0043] figure 1 is a plan view of a nitride semiconductor HFET as a field effect transistor of the first embodiment, figure 2 for figure 1 The cross-sectional view of the A-A' arrow.

[0044] The nitride semiconductor HFET as figure 2 As shown, on a substrate 1 made of Si, a channel layer 2 made of GaN and a channel layer made of Al are sequentially formed. x Ga 1-x A barrier layer 3 composed of N (0x Ga 1-x The Al mixed crystal ratio x of N is set to x=0.17 as an example. Then, 2DEG (two dimensional electrons: two-dimensional electron gas) is generated at the interface between the channel layer 2 and the barrier layer 3 . In the present embodiment, the nitride semiconductor 4 is constituted by the channel layer 2 and the barrier layer 3 . In addition, in this embodiment, as an example, the thickness of the barrier layer 3 is set to 30 nm.

[0045] On the barrier layer 3 , a source electrode 5 and a drain electrode 6 are formed with a preset interval. In the present...

no. 2 approach

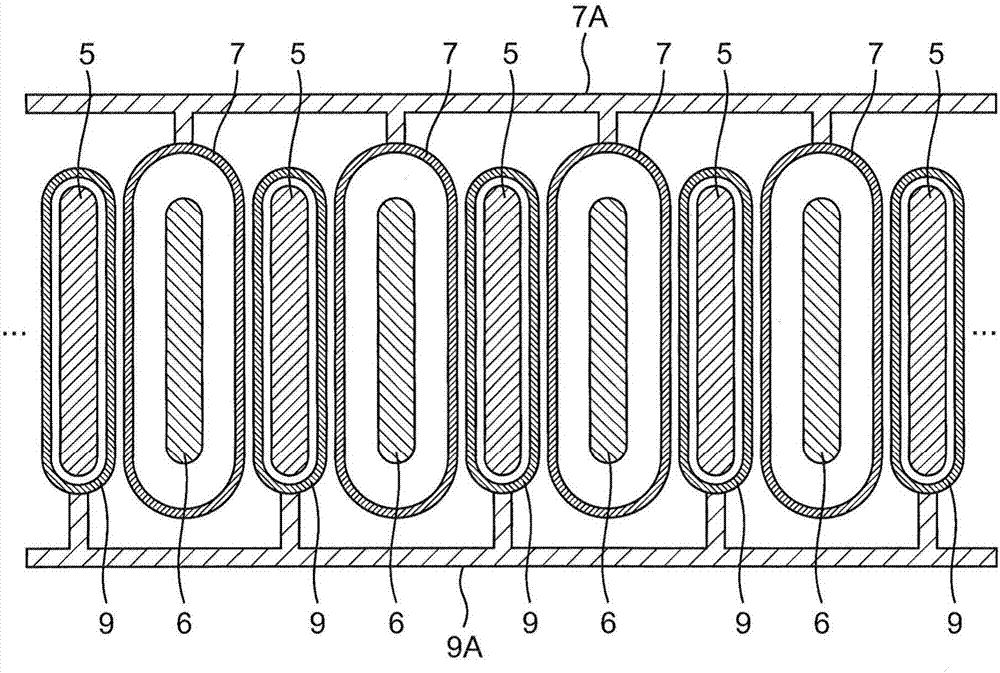

[0064] image 3 It is a plan view of a nitride semiconductor HFET as a field effect transistor of the second embodiment.

[0065] The nitride semiconductor HFET, towards the image 3 The cross section in the direction perpendicular to the extending direction of the drain electrode 6 has the same figure 2Exactly the same structure. Here, the same reference numerals are assigned to the same components as in the first embodiment, and detailed description thereof will be omitted. Hereinafter, points different from the case of the first embodiment will be described.

[0066] In this embodiment, if image 3 As shown, in plan view, in the direction perpendicular to the extending direction of the drain electrode 6, a plurality of figure 1 The structure of the nitride semiconductor HFET of the first embodiment is shown. Then, at one of the two ends of the first gate electrode 7 of each nitride semiconductor HFET, a first gate electrode wiring 7A commonly connected to each first ...

no. 3 approach

[0070] Figure 4 It is a plan view of a nitride semiconductor HFET as a field effect transistor of the third embodiment.

[0071] The nitride semiconductor HFET, towards the Figure 4 The cross-section in the direction perpendicular to the extending direction of the drain electrode 6 has the same figure 2 Exactly the same structure. Here, the same reference numerals are assigned to the same components as in the first embodiment, and detailed description thereof will be omitted. Hereinafter, points different from those of the first and second embodiments will be described.

[0072] In this embodiment, if Figure 4 As shown, when viewed from above, the distance L1 between the first gate electrode 7 and the drain electrode 6 in normal conduction operation at the end is set to be the same as the distance L2 to the straight line portion or to be larger than the distance L2 at the straight line. The distance to L2 is longer.

[0073] Also in the said end part, the electric fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More