Method for checking consistency of schematic diagram and PCB production data

A technology of production data and schematic diagrams, applied in the field of electronic information, can solve problems such as production scrap, functional failure, project delay, etc., to achieve the effect of saving time, cost and simple operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be further described below in conjunction with drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only some parts related to the present invention are shown in the accompanying drawings but not the whole content. Unless otherwise defined, all technical and scientific terms used herein are related to the technical field of the present invention. The skilled person generally understands the same meaning. The terms used herein are for describing specific embodiments only, and are not intended to limit the present invention.

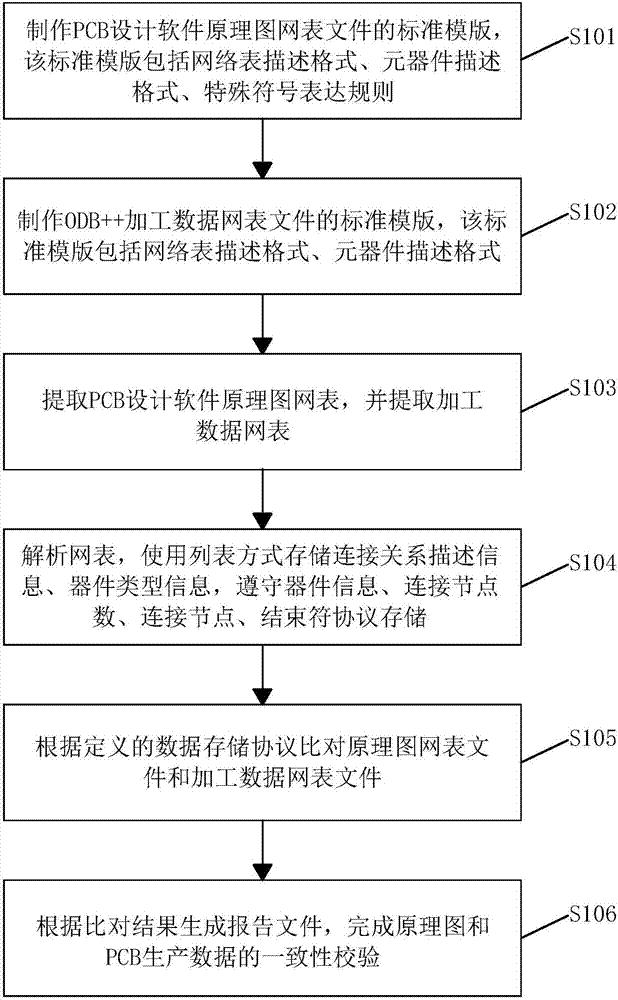

[0018] Please refer to figure 1 as shown, figure 1 The flow chart of the method for verifying the consistency of the schematic diagram and PCB production data provided by the present invention.

[0019] In this embodim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More