A Multi-input High Speed CMOS Buffer Circuit

A multi-input, buffer technology, applied in the direction of logic circuit, logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the problem of high circuit power consumption, slow buffer processing speed, increase Buffer complexity and other issues, to achieve the effect of small delay, strong application advantages, and improved ease of use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

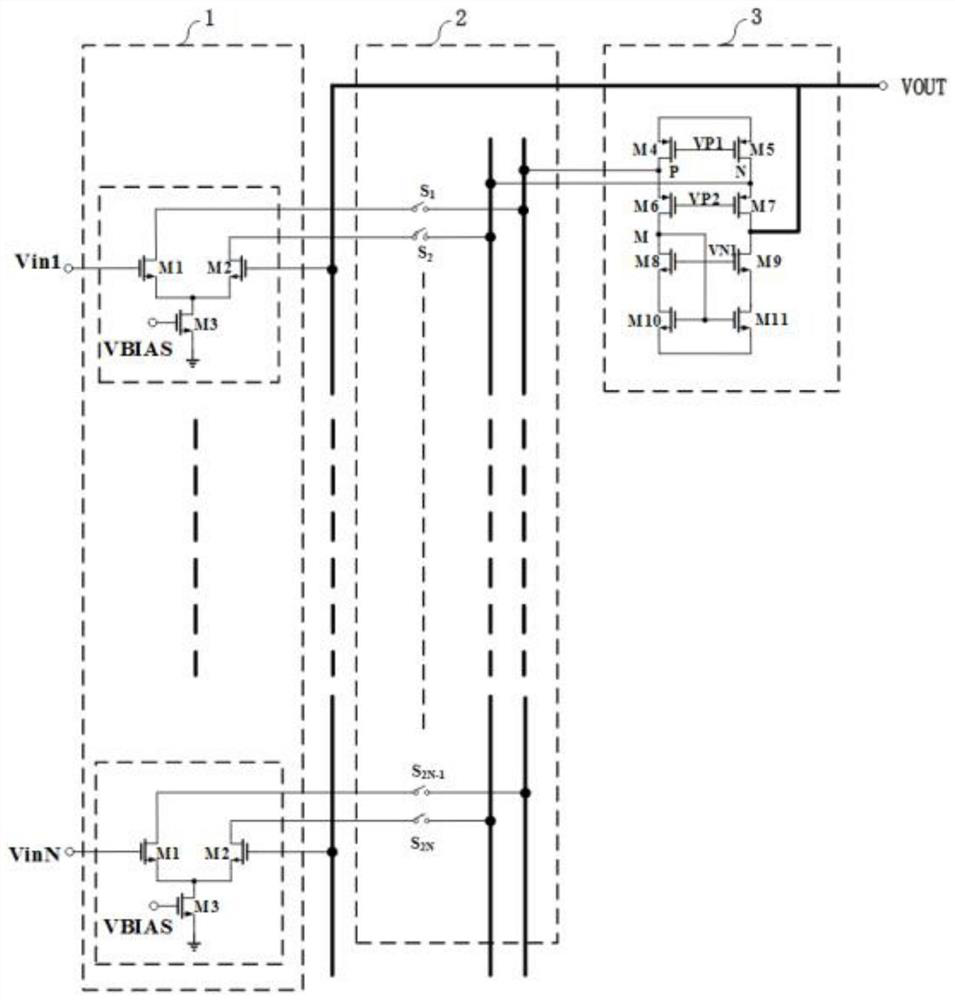

[0017] In order to make the purpose, technical solution and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

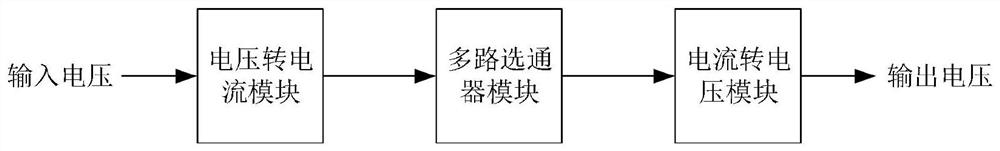

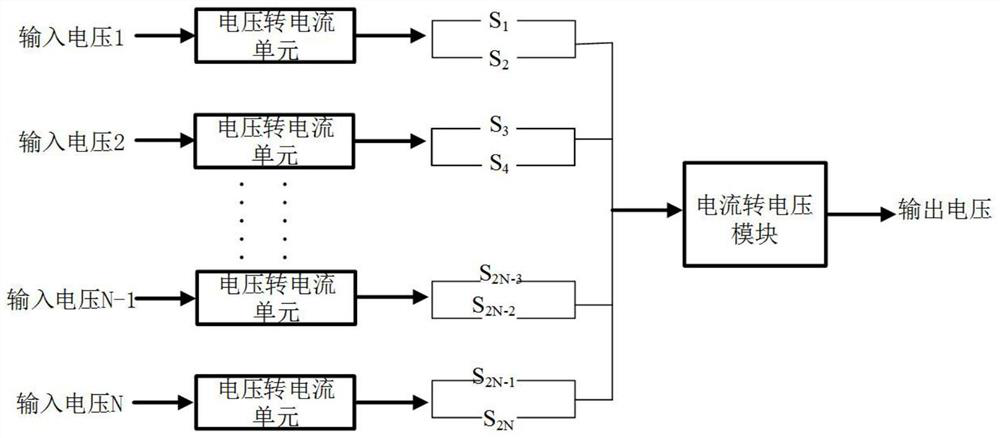

[0018] Such as figure 1 As shown, a multi-input high-speed CMOS buffer circuit, which includes a voltage-to-current module, a multiplexer module, and a current-to-voltage module, and the two sides of the multiplexer module are respectively connected to the voltage-to-current module and the current The other side of the voltage-to-voltage module is used for input voltage, and the other side of the current-to-voltage module is used to output voltage; the voltage-to-current module is used to convert multiple input voltages into current signals; multi-way selection The passer module is used to conduct the voltage-to-current module and the current-to-voltage module; the current-to-voltage module converts the input current signal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More