Bridge circuit for EMIF interface and AHB/APB time series and control method of bridge circuit

A technology of bridging circuits and timing, applied in electrical digital data processing, instruments, etc., can solve problems such as irrelevant research and achieve the effect of reducing space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The specific embodiment of the present invention will be described in detail below in conjunction with the accompanying drawings, but the present invention is not limited to this embodiment. In order to provide the public with a thorough understanding of the present invention, specific details are specified in the following preferred embodiments of the present invention.

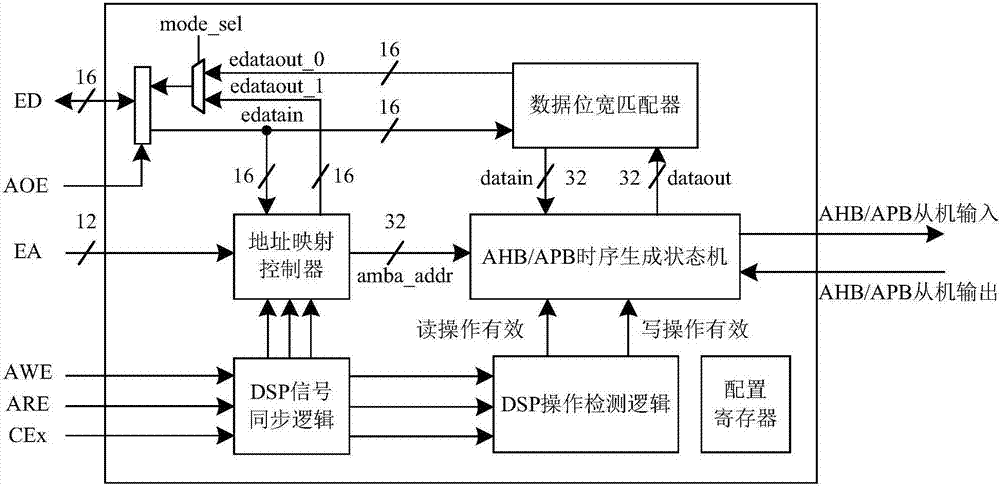

[0051] The invention discloses an EMIF interface and AHB / APB timing bridge circuit, which solves the problem of direct access of resources on SoC chip by DSP and simultaneously solves the problem of data bit width matching between 16-bit EMIF interface and 32-bit AMBA bus. The bridging circuit is integrated in the SoC chip, and is connected to an external DSP through an EMIF interface to complete analysis, splicing and conversion of DSP access timing, and finally realize efficient operation of on-chip resources. The bridging circuit supports DSP access control to 16 AHB / APB slaves at most.

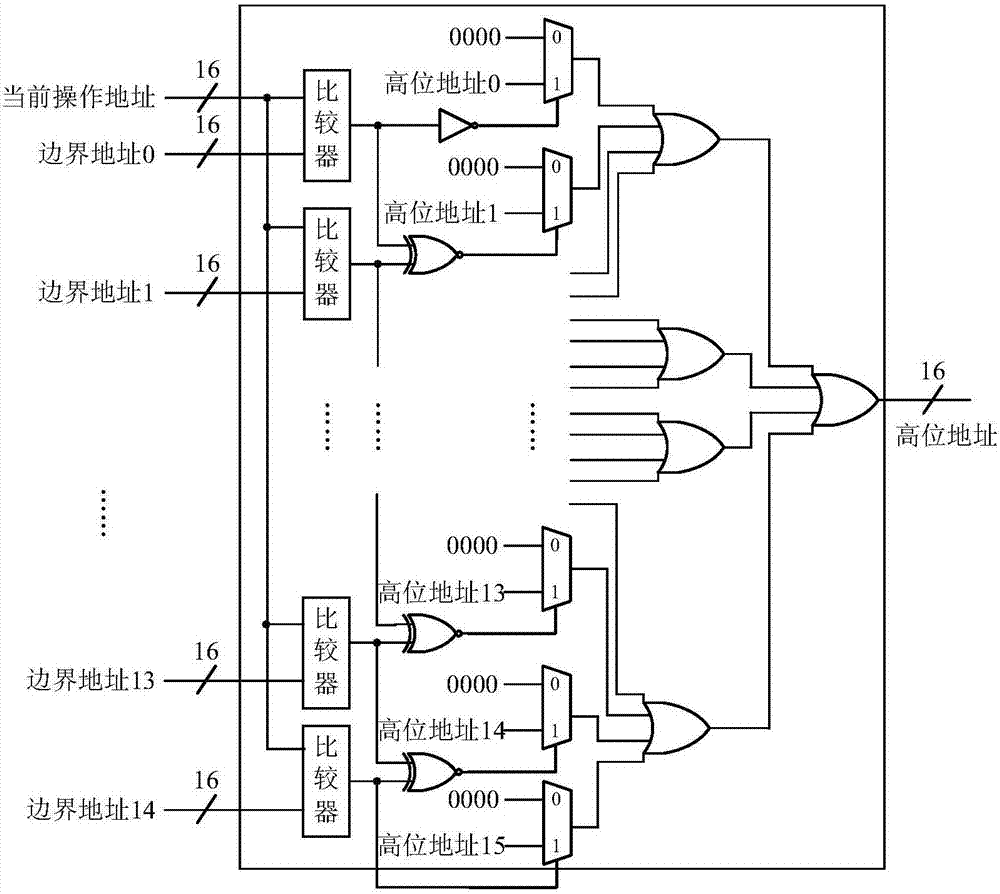

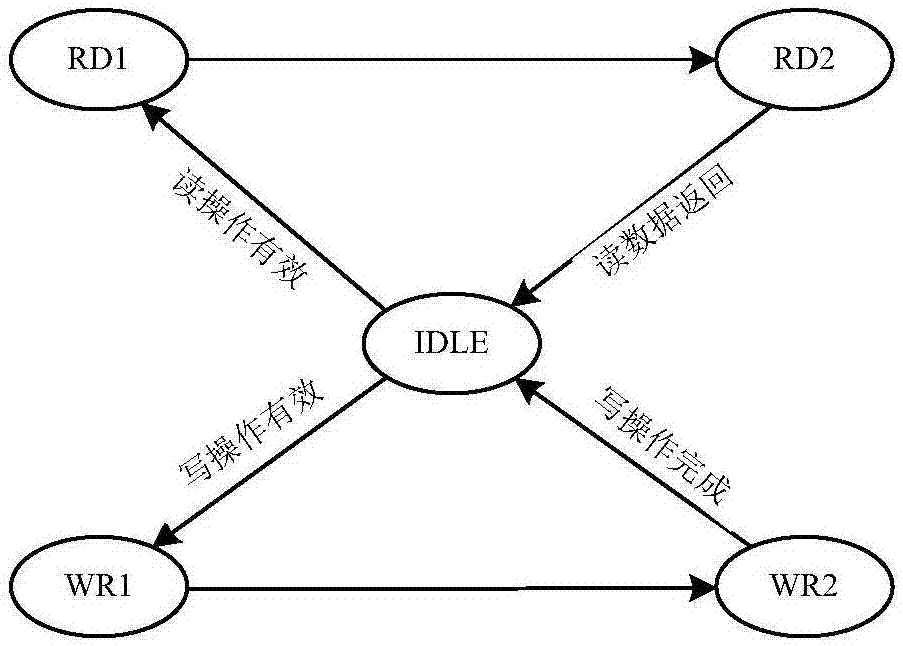

[0052] T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More