Method for writing in an EEPROM memory and corresponding device

A technology for writing operations and memory cells, which is applied in the field of memory, and can solve problems such as unacceptable number of write times, write problem obstacles, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

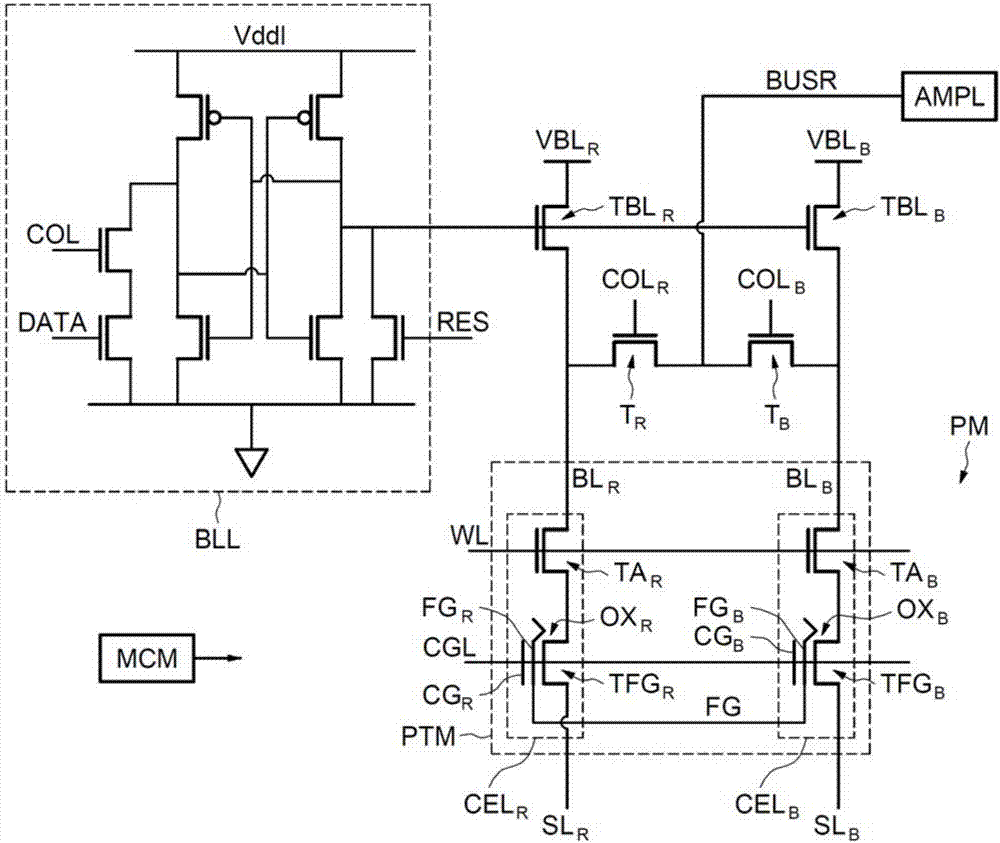

[0049] figure 1 An embodiment of a memory device of the EEPROM type is shown, comprising: a memory location PTM on a memory plane PM; BUSR is in particular a switching element connecting the memory plane PM with the sense amplifier AMPL.

[0050] In particular, the sense amplifier AMPL is configured for reading the content of the bits stored in the memory location PTM.

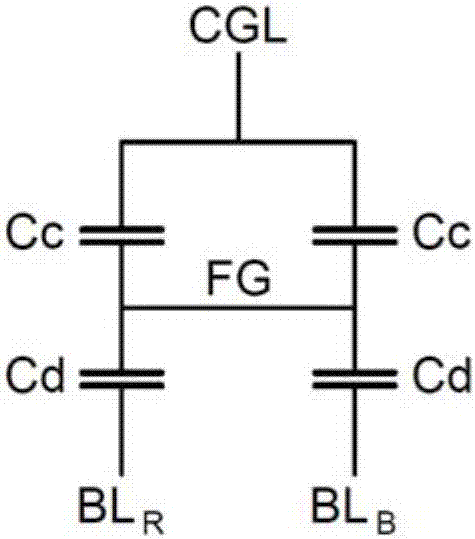

[0051] Memory location PTM includes two identical memory cells CEL R 、CEL B . first memory cell CEL R is referred to as a "regular cell", while the second memory cell CEL B Known as a "boost unit".

[0052] Conventional memory cell CEL R includes a first-state transistor TFG called “regular” R and the first access transistor TA controlled by a signal passed through the word line WL R , the first access transistor TA R The drain is connected to the first bit line BL R . The first access transistor TA R The source is connected to the first state transistor TFG R the drain.

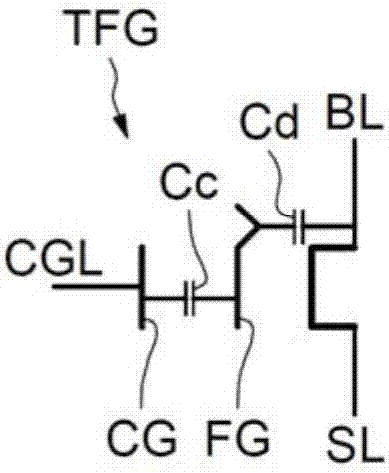

[0053] First state tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More