Manufacturing method of tft array substrate

A manufacturing method and array substrate technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of conductive film 9' rupture, affect panel display effect, and unreliable resistance bridging, etc., to improve product quality. Yield rate, improved display effect, bridging reliable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to further illustrate the technical means adopted by the present invention and its effects, the following describes in detail in conjunction with preferred embodiments of the present invention and accompanying drawings.

[0041] The invention provides a method for manufacturing a TFT array substrate, comprising the following steps:

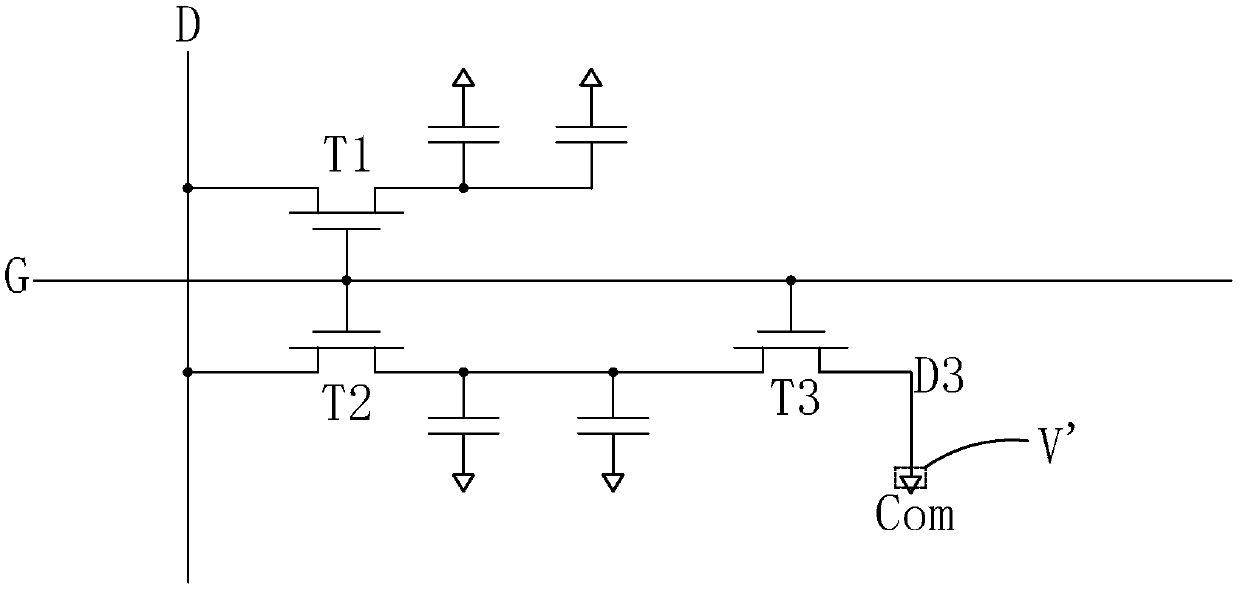

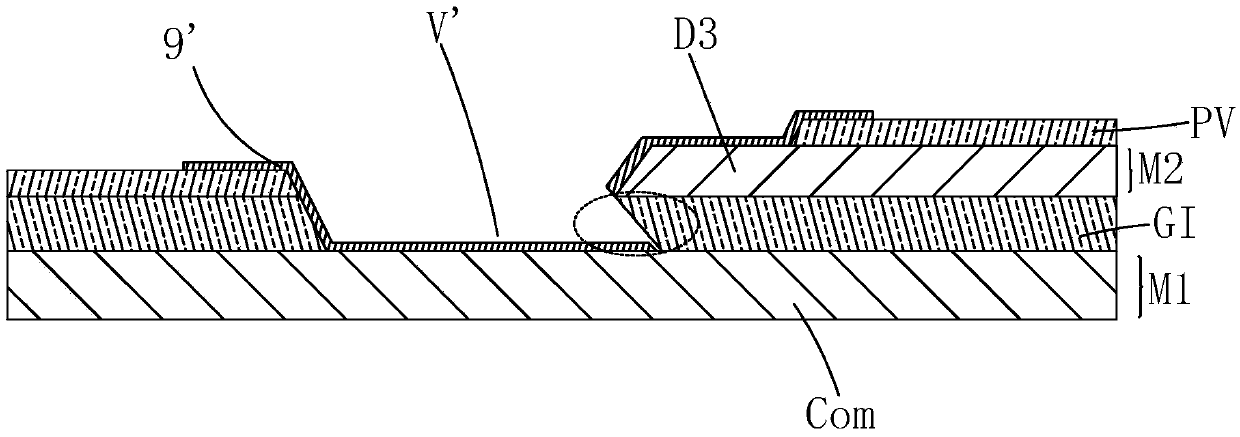

[0042] Step S1, please refer to Image 6 , combined with Figure 12 On the substrate 1, a first metal layer M1, a gate insulating layer GI, a semiconductor active layer 2, a second metal layer M2, and a protection layer PV are sequentially formed from bottom to top, and a photoresist is coated on the protection layer PV. PR.

[0043] The gate insulating layer GI covers the first metal layer M1, and the first metal layer M1 includes a gate line G and a common voltage line Com;

[0044] The protection layer PV covers the second metal layer M2, and the second metal layer M2 includes a data line D, a first source S1, a first drain D1,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More