Patents

Literature

278results about How to "Avoid undercut" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

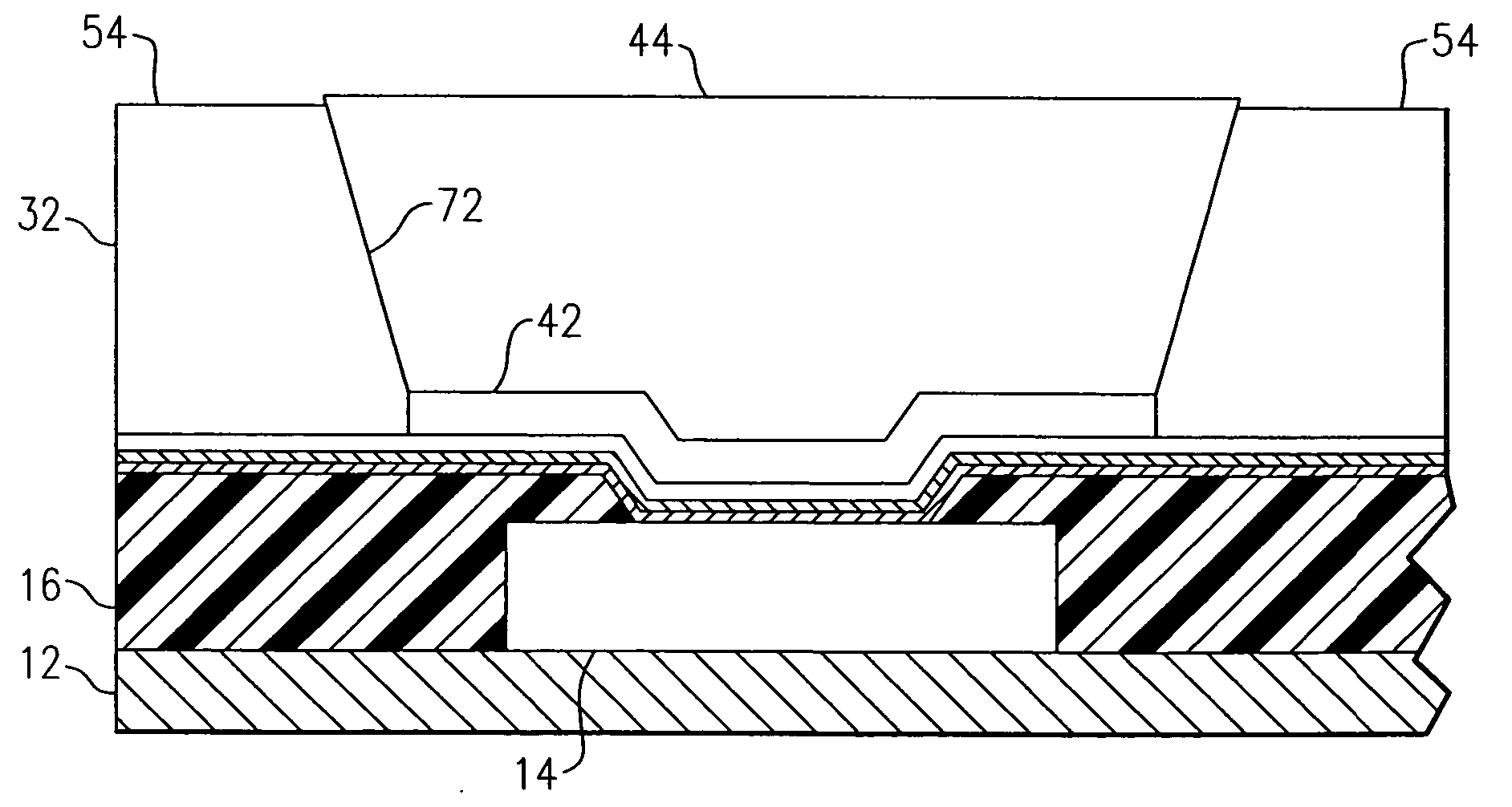

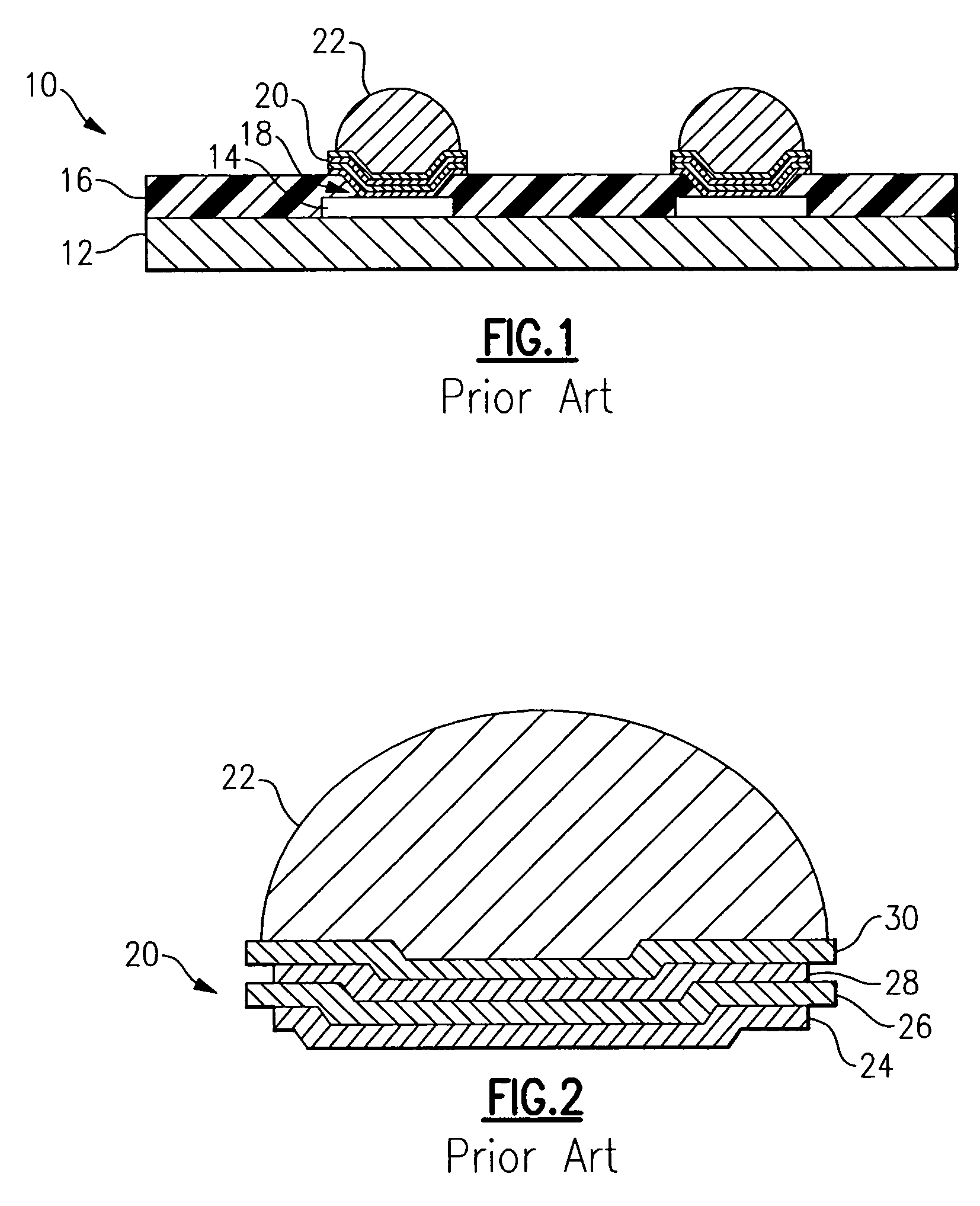

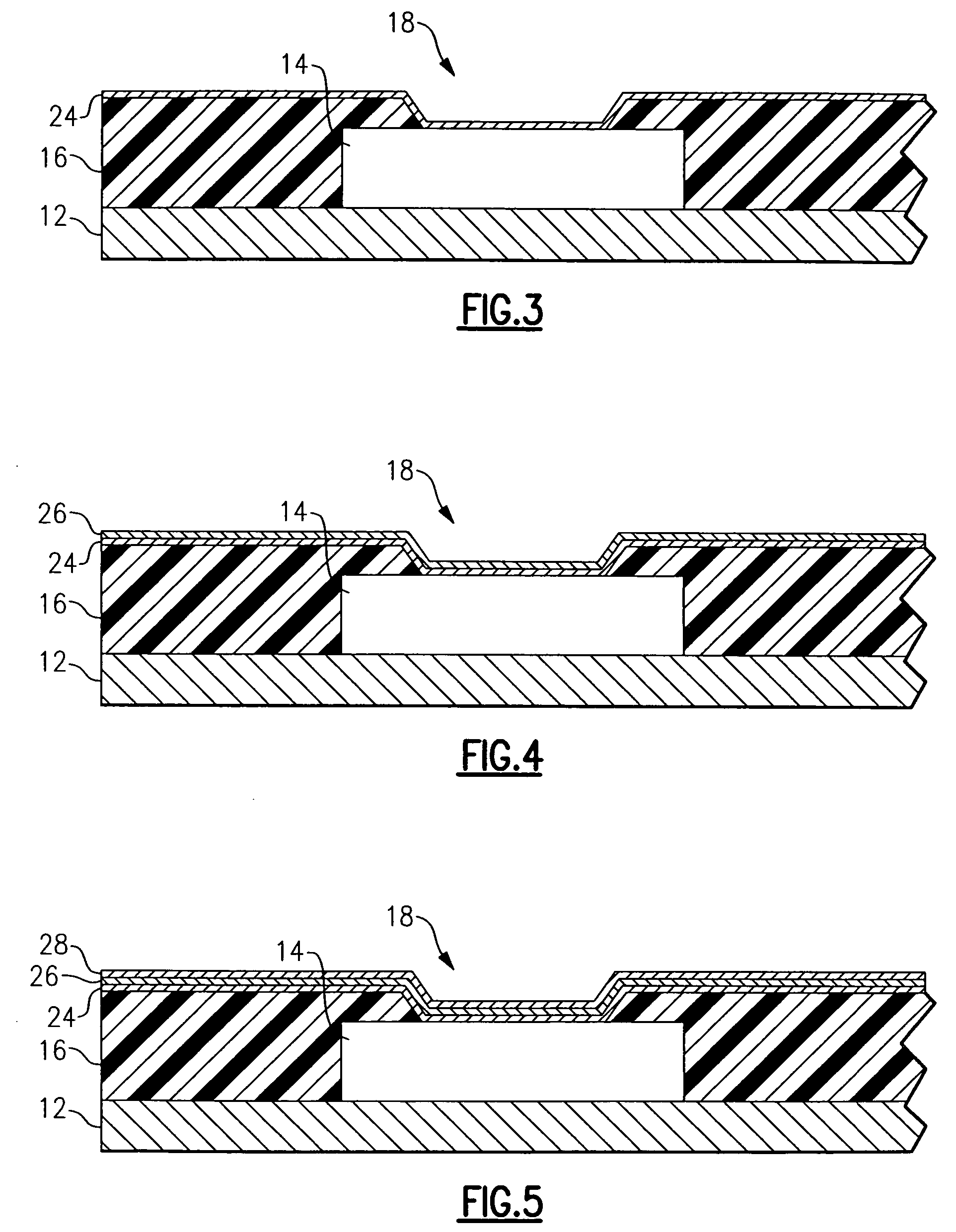

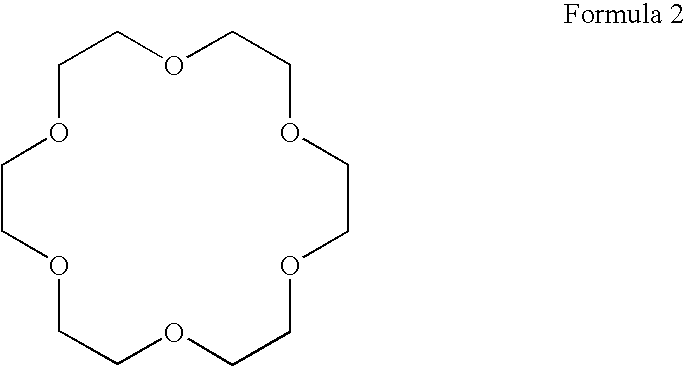

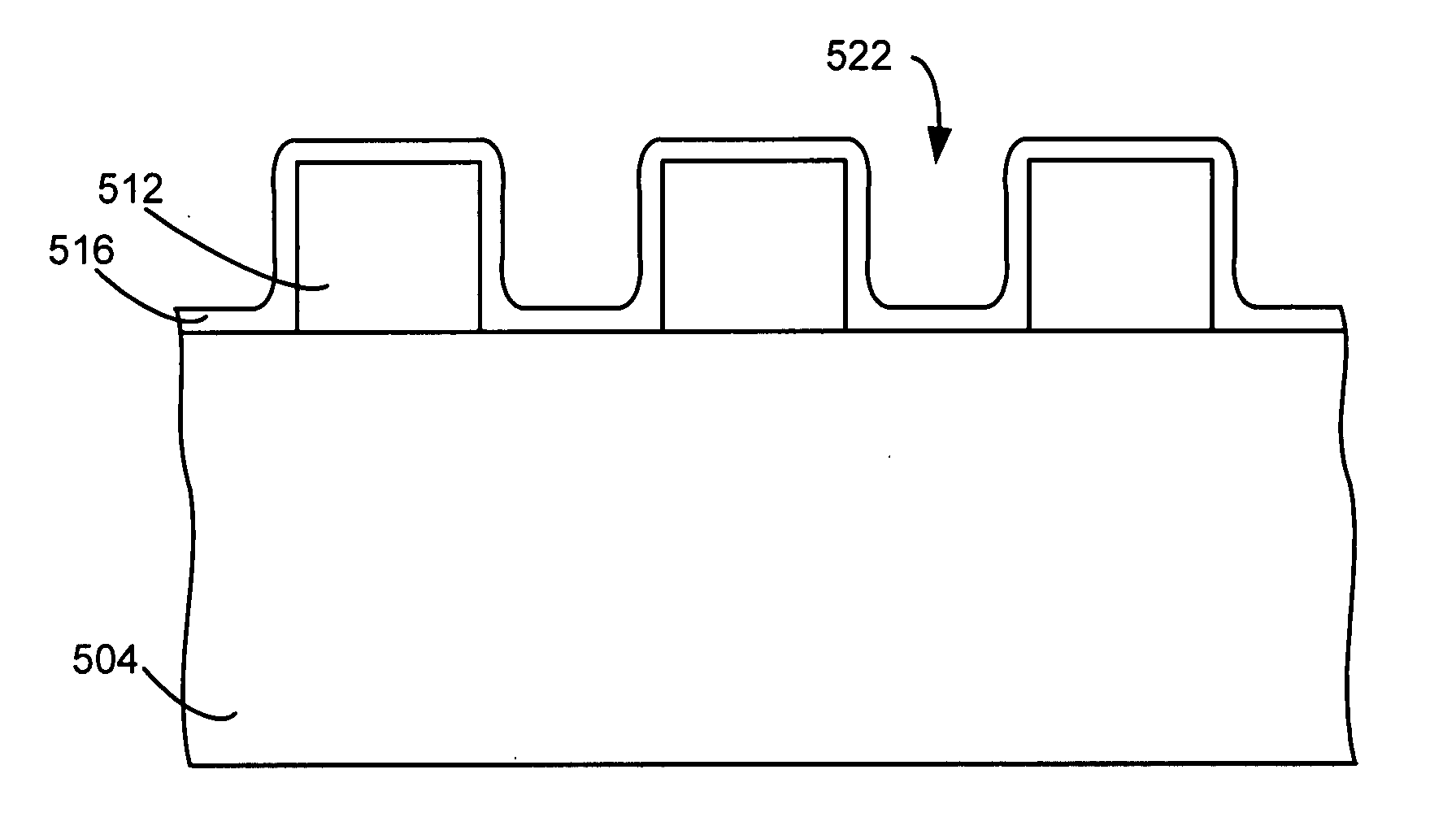

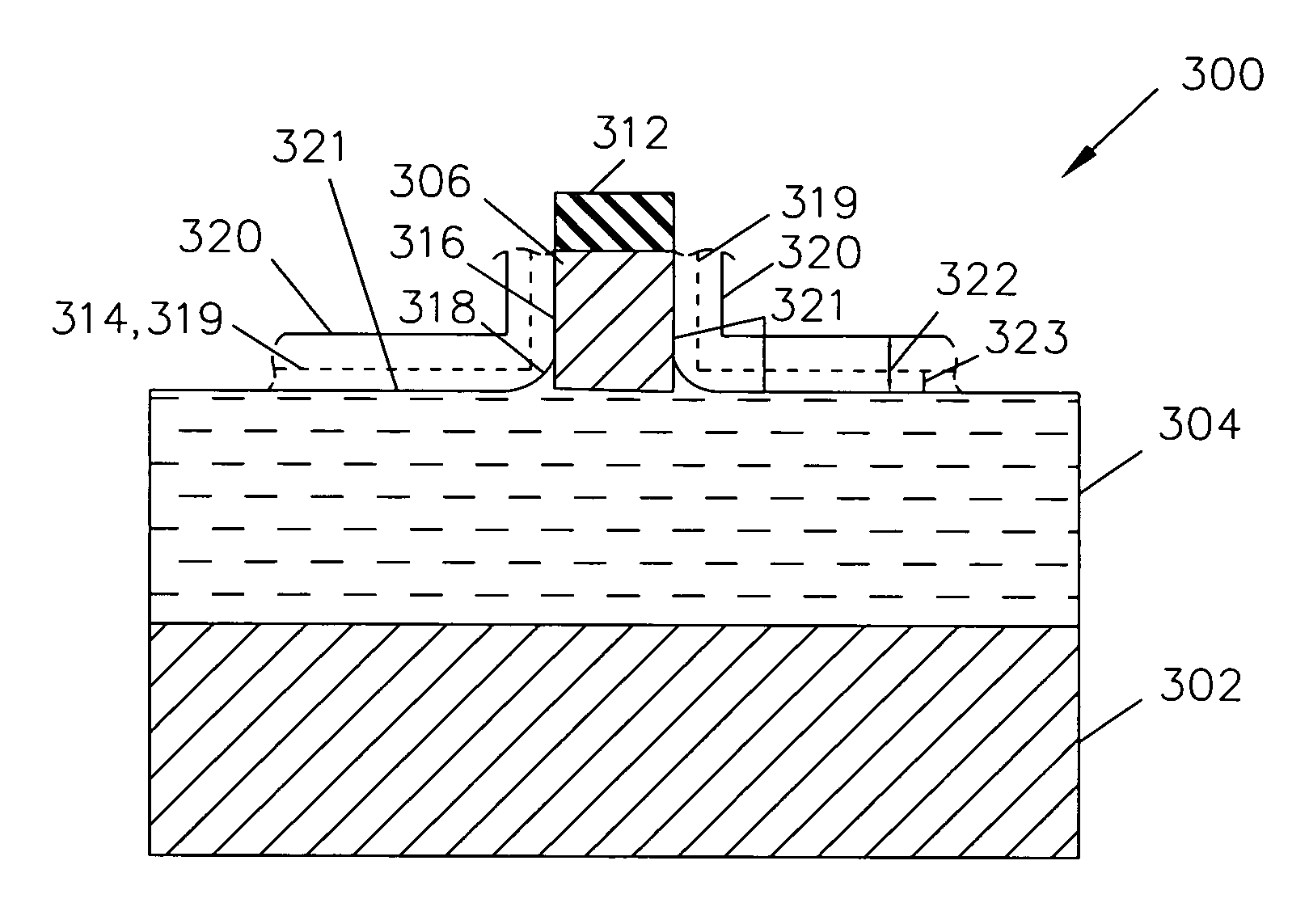

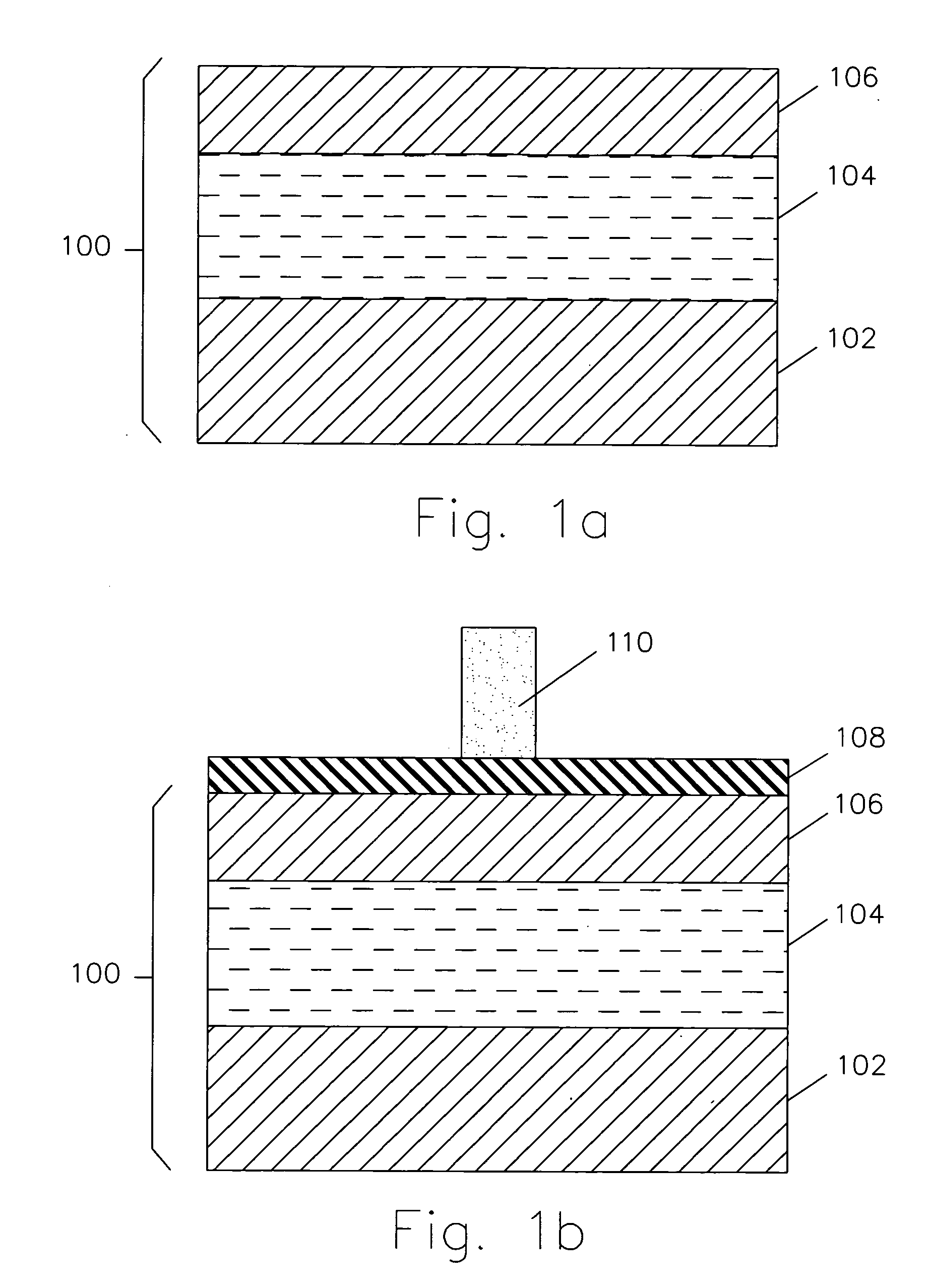

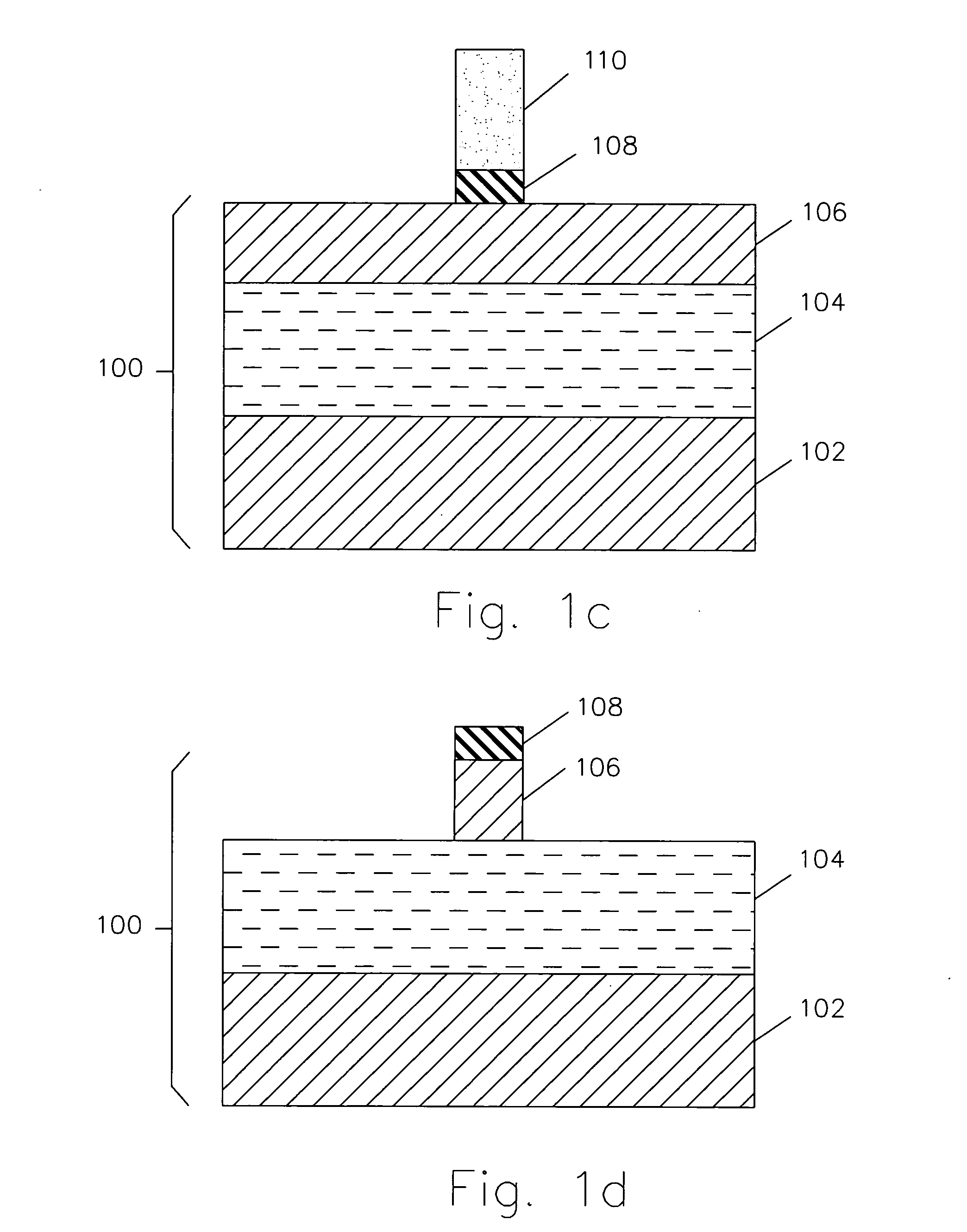

Resist sidewall spacer for C4 BLM undercut control

InactiveUS20060076677A1Avoid undercutAvoid layeringSemiconductor/solid-state device detailsSolid-state devicesResistEngineering

A method and system for preventing undercutting of the solder bump in a C4 package by forming a barrier of resist that effectively widens the footprint of the solder bump. The BLM is then etched to the perimeter edge of the barrier rather than the solder bump, thereby precluding any undercutting of the solder bump by the BLM. The barrier may formed by using a half-tone mask that fully exposes the immediately surrounding regions to define a sidewall enclosing the C4 cavity. The barrier may also be formed by applying a second resist prior to, or after, plating the solder and then patterning to inhibit etching directly adjacent to the C4 cavity. The barrier may additionally be formed by overfilling solder into the C4 cavity so that it spreads laterally over the sidewall portion of the resist layer. The resist is then etched anisotropically to leave the barrier. In another embodiment, a taper is introduced into the profile of the C4 cavity by reflowing the resist by an annealing step. The resist is then etched anisotropically to leave the barrier surrounding the C4 solder.

Owner:IBM CORP

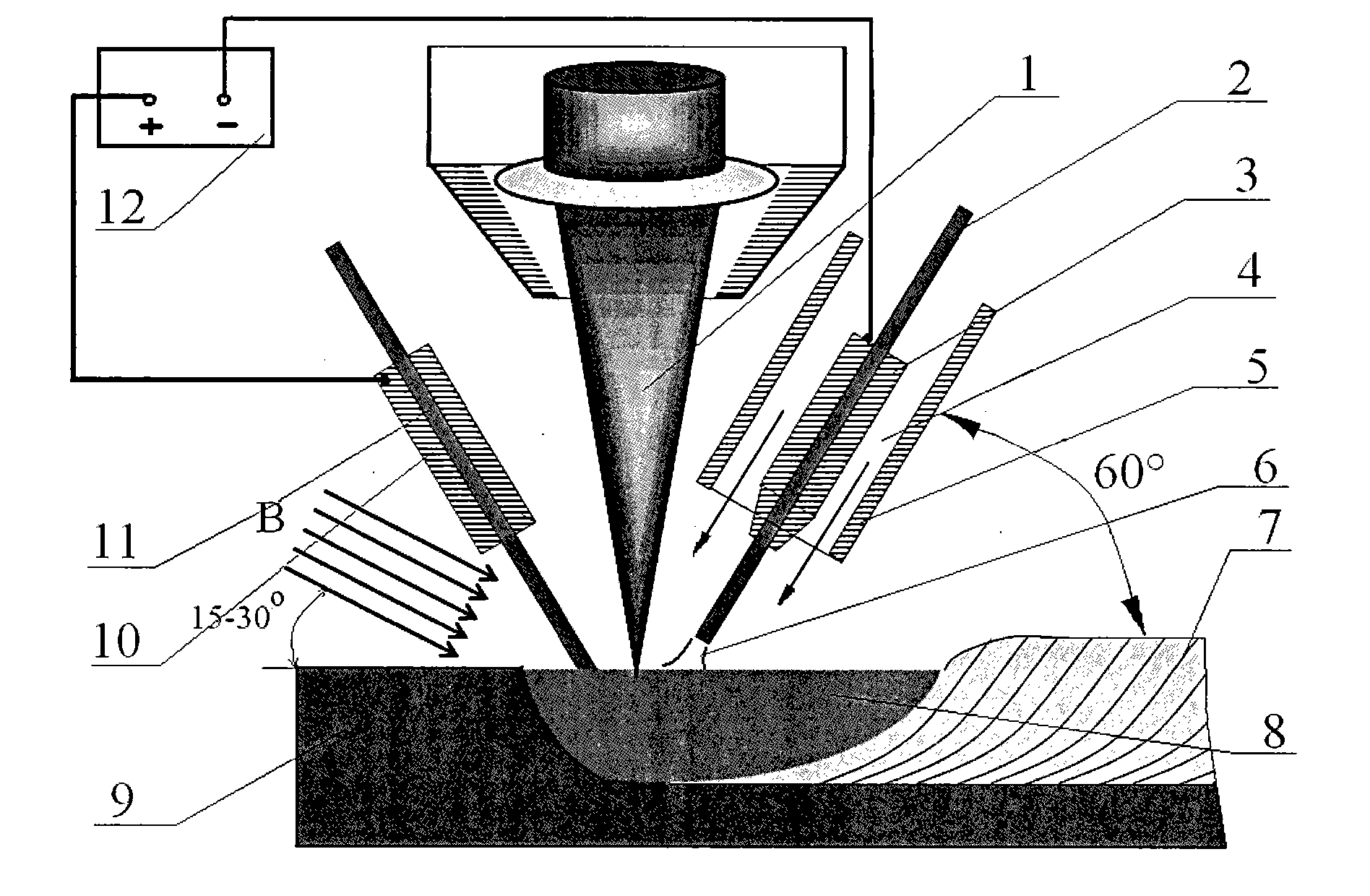

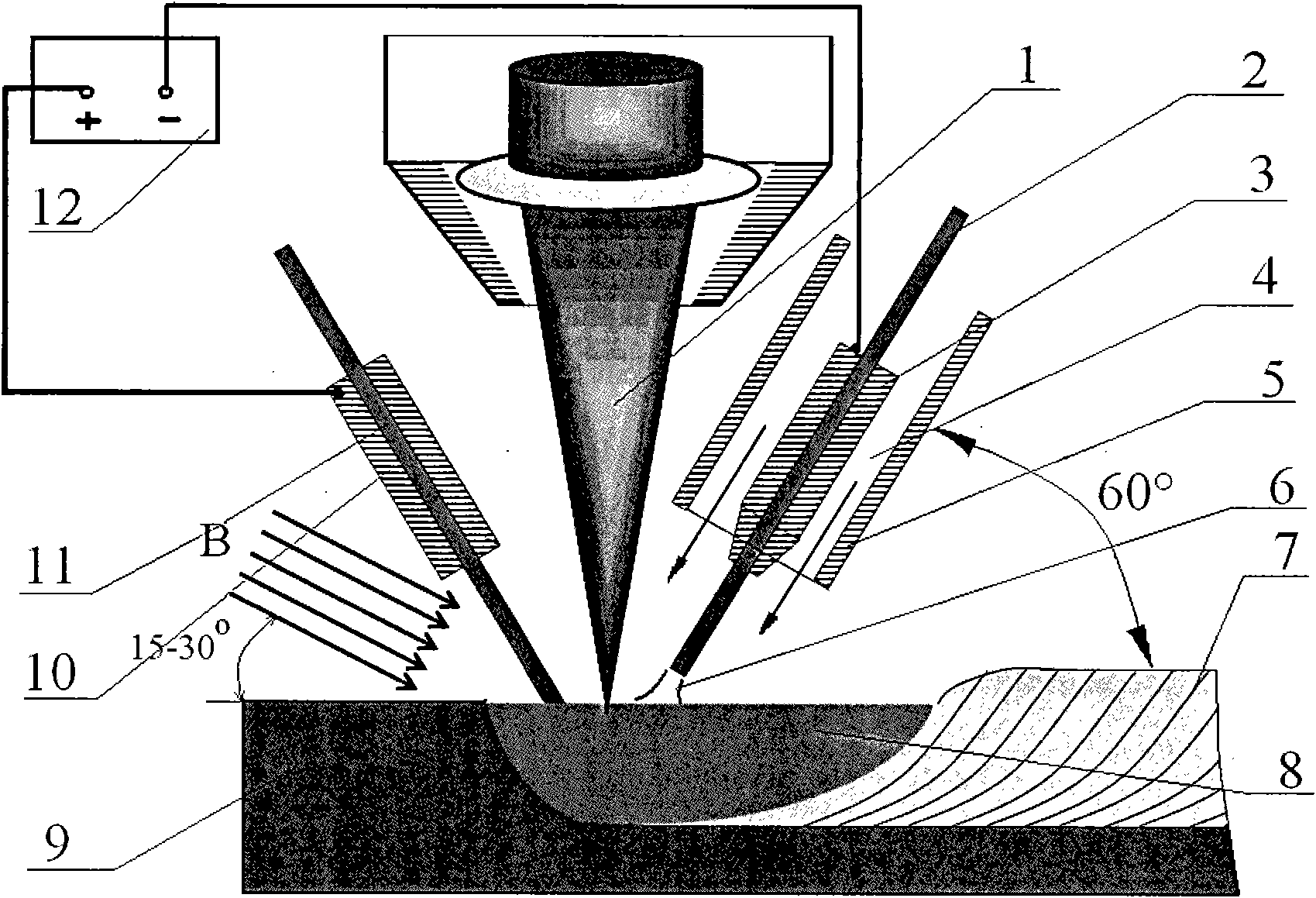

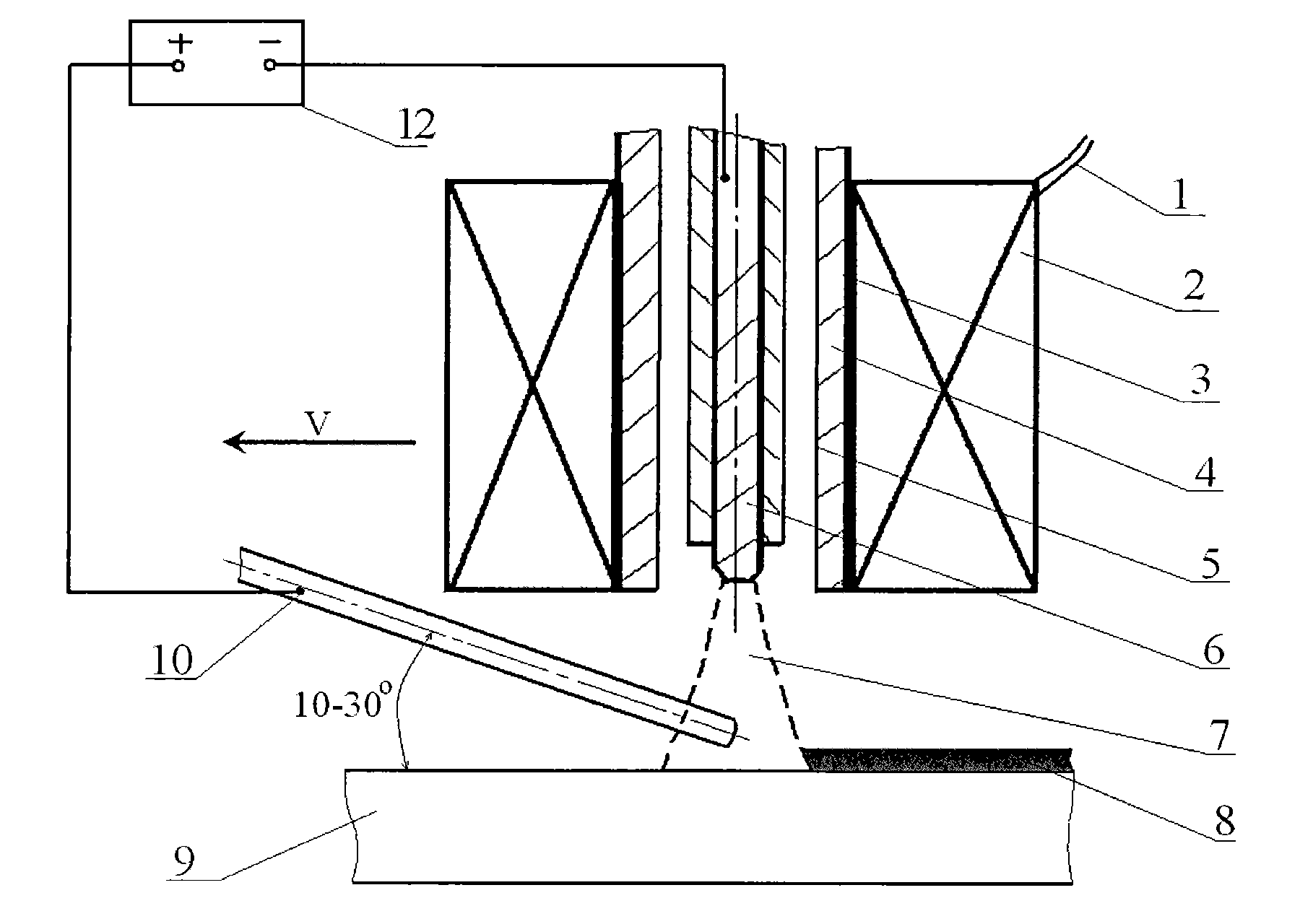

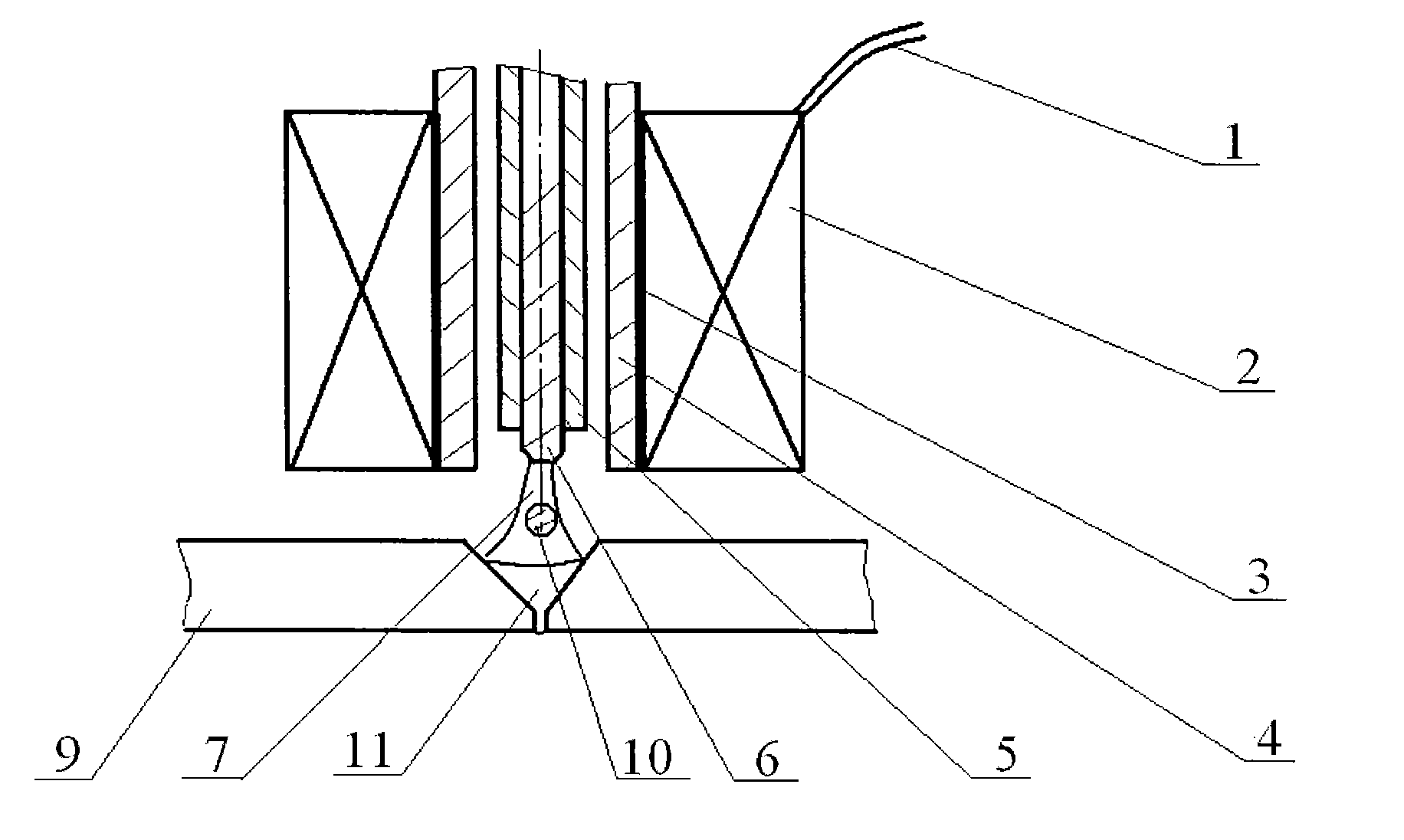

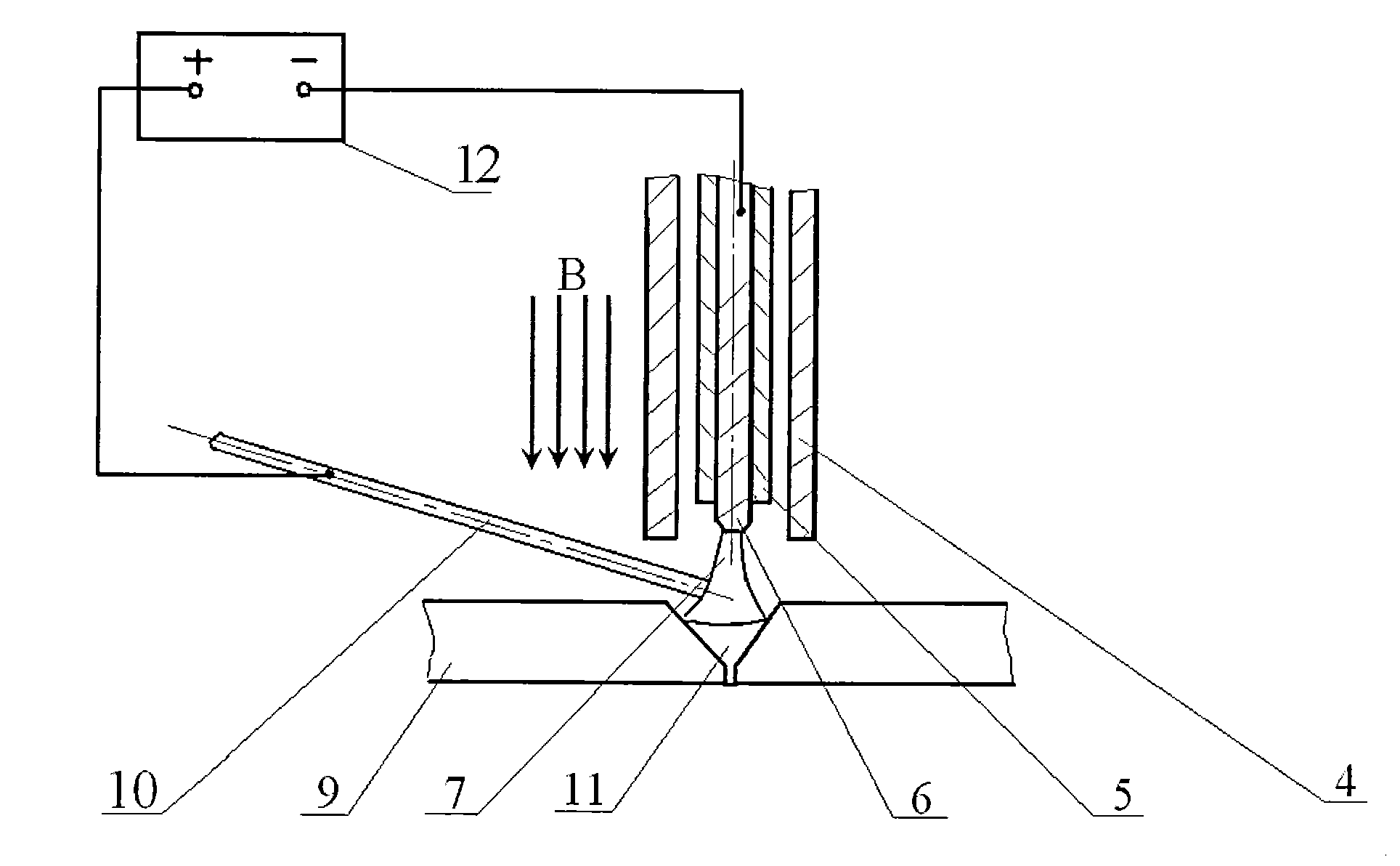

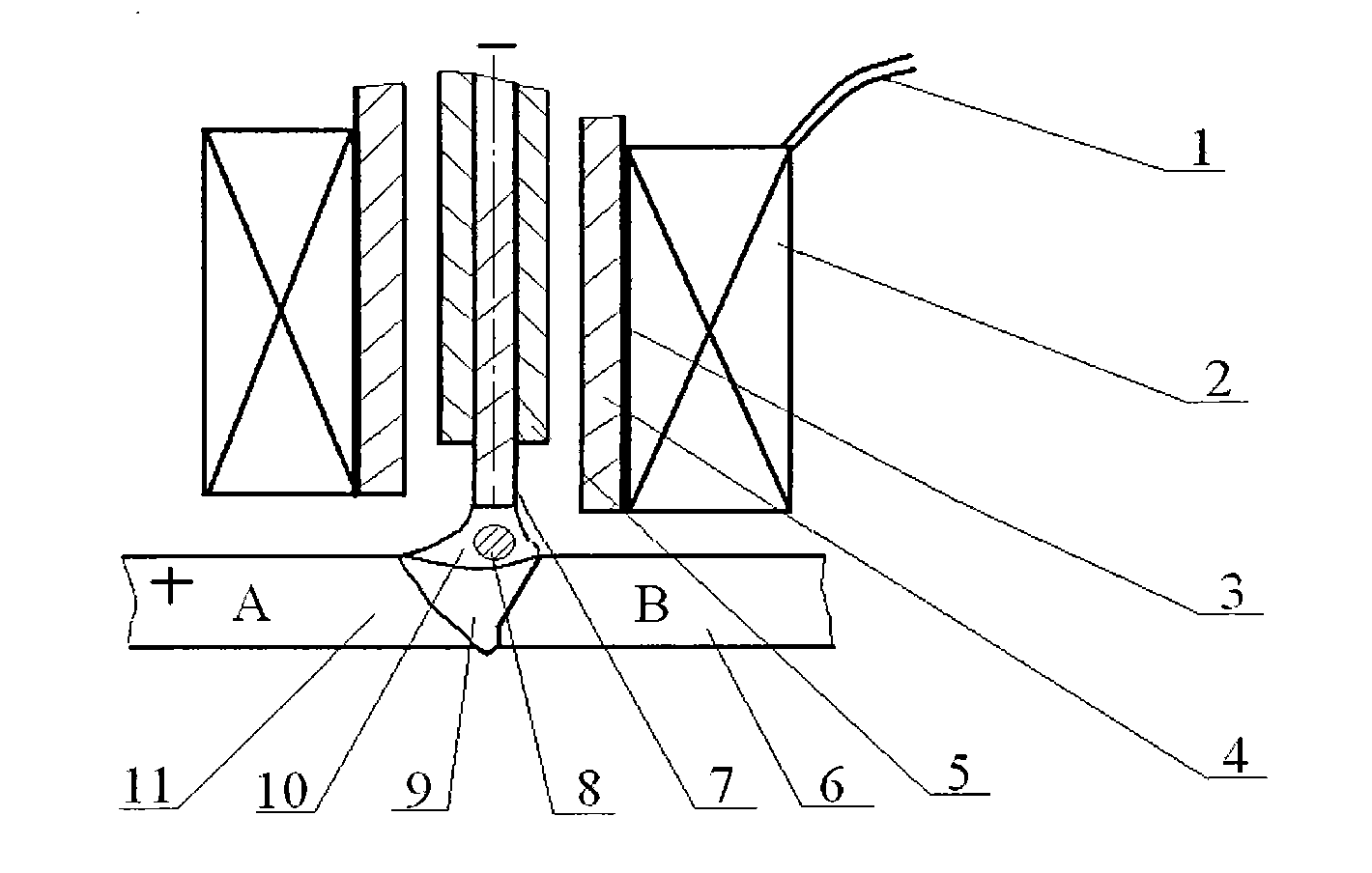

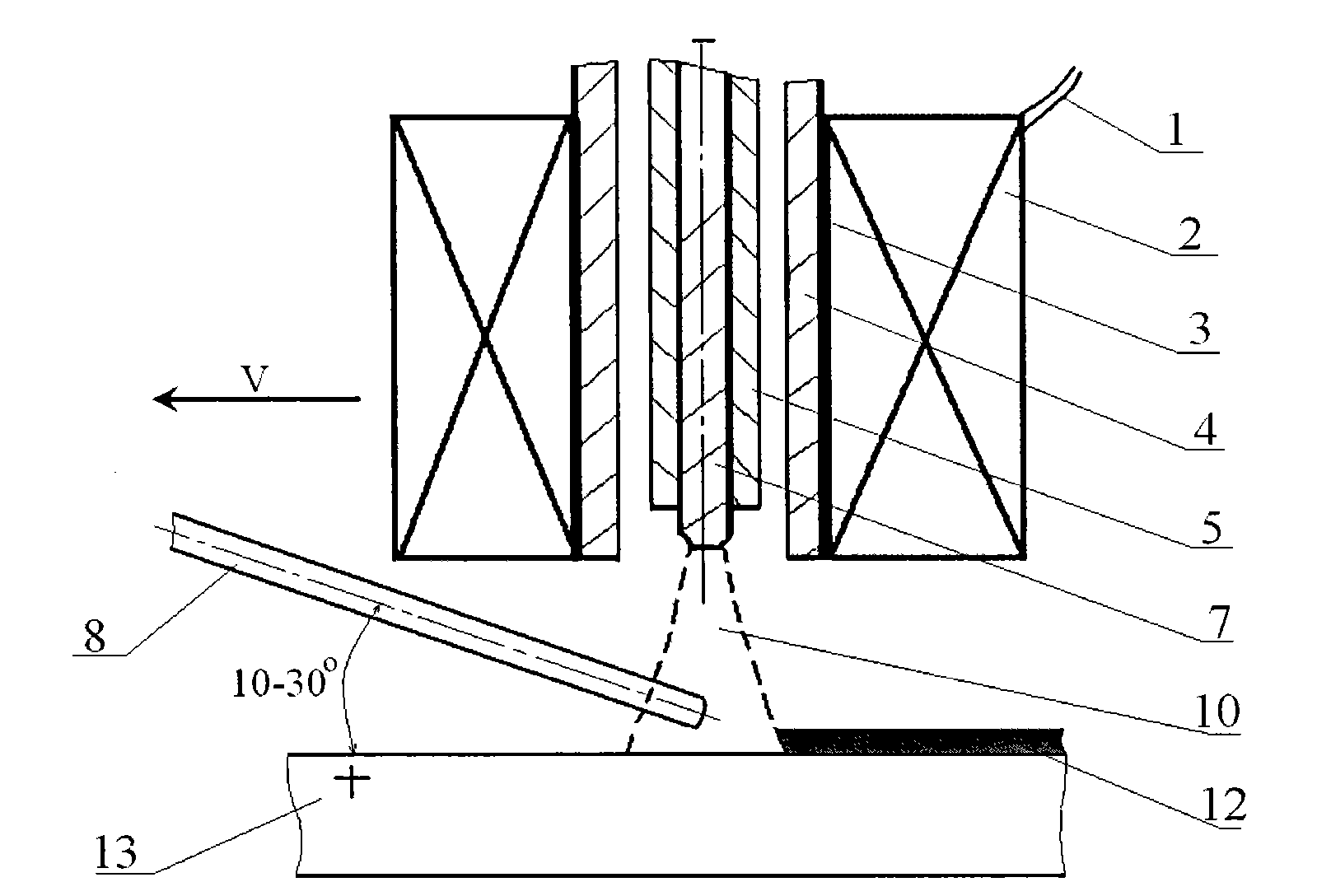

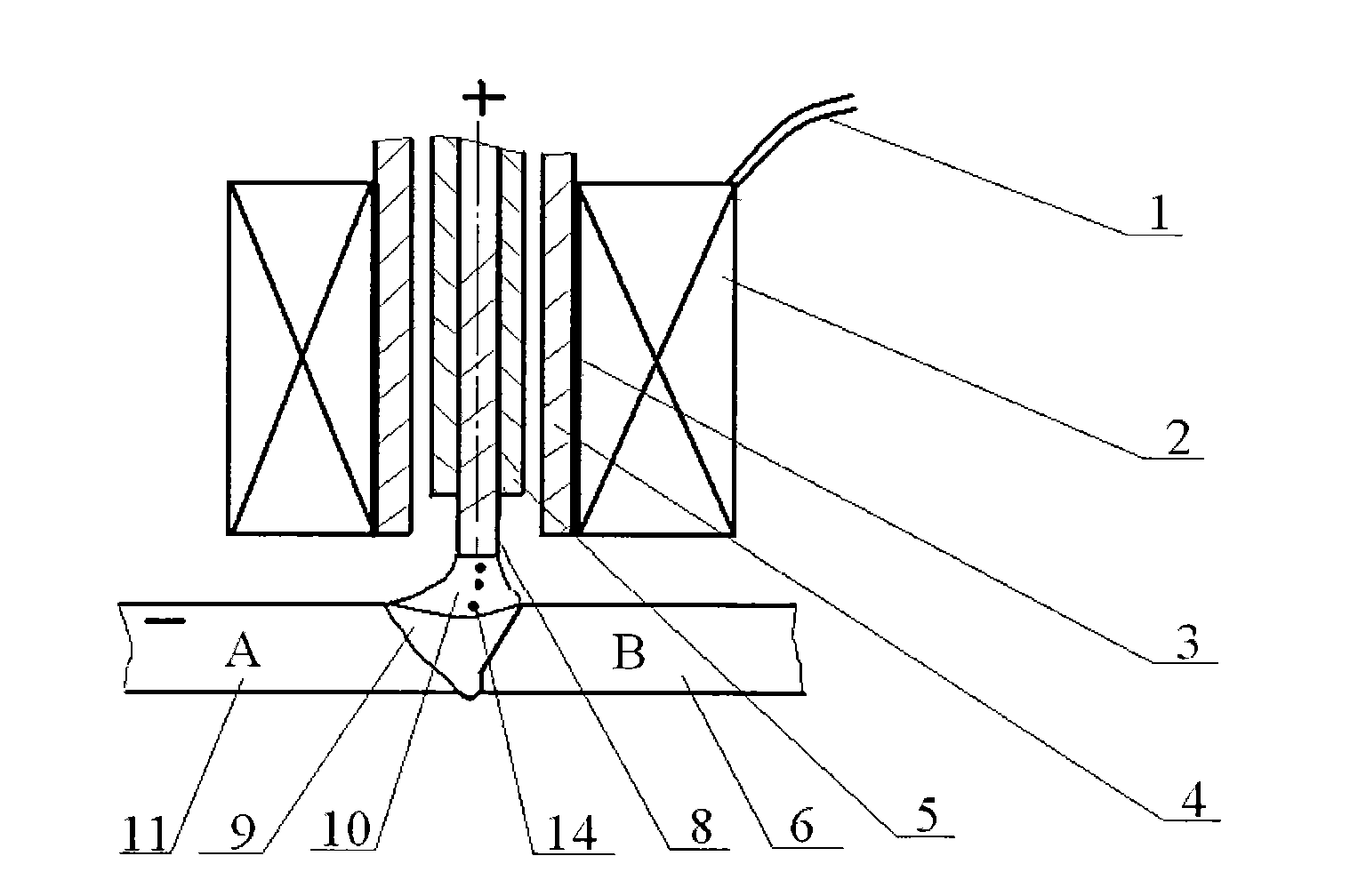

Electromagnetic current coupling field assisted hybrid melting-brazing method for laser-TIG arc and equipment

InactiveCN101862913AImprove connection qualityInhibition formationSoldering apparatusWelding apparatusMetallic materialsWelding defect

The invention discloses an electromagnetic current coupling field assisted hybrid melting-brazing method for a laser-TIG arc and equipment. In addition to the use of the welding zone, an alternating magnetic field is added to control properties of plasma formed through ionization of laser, arc and a raw material metal, thereby improving the laser utilization rate. Under the electric field assisted comprehensive effect, the weld melting depth is increased, and the assistant effect on the melting bath of the liquid-state brazing filler metal for laser-arc melting-brazing is realized through electromagnetic stirring and excitation and enhancement, thereby promoting the orderly flow of the liquid-state brazing filler metal and the rupture, wetting, spreading and proliferation of the liquid-state brazing filler metal on the surface of the high metal material, improving the full mixing of the liquid-state brazing filler metal and the base metal formed by melting the low-melting-point metal material, improving the uniformity of the components of the brazed weld, stabilizing the welding process, reducing welding defects, increasing the welding speed, improving the weld formation, optimizing the structure and performance of the brazed weld, and improving the quality of the brazed joint. Moreover, the equipment has the advantages of simple structure, flexible application, low cost, good effect and easy realization.

Owner:CHONGQING UNIV

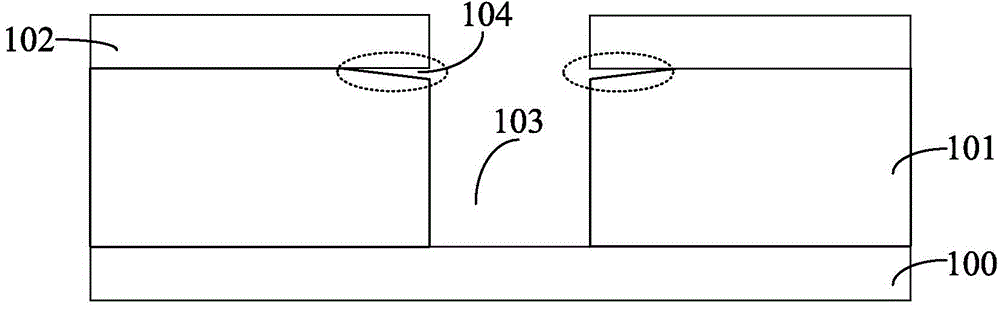

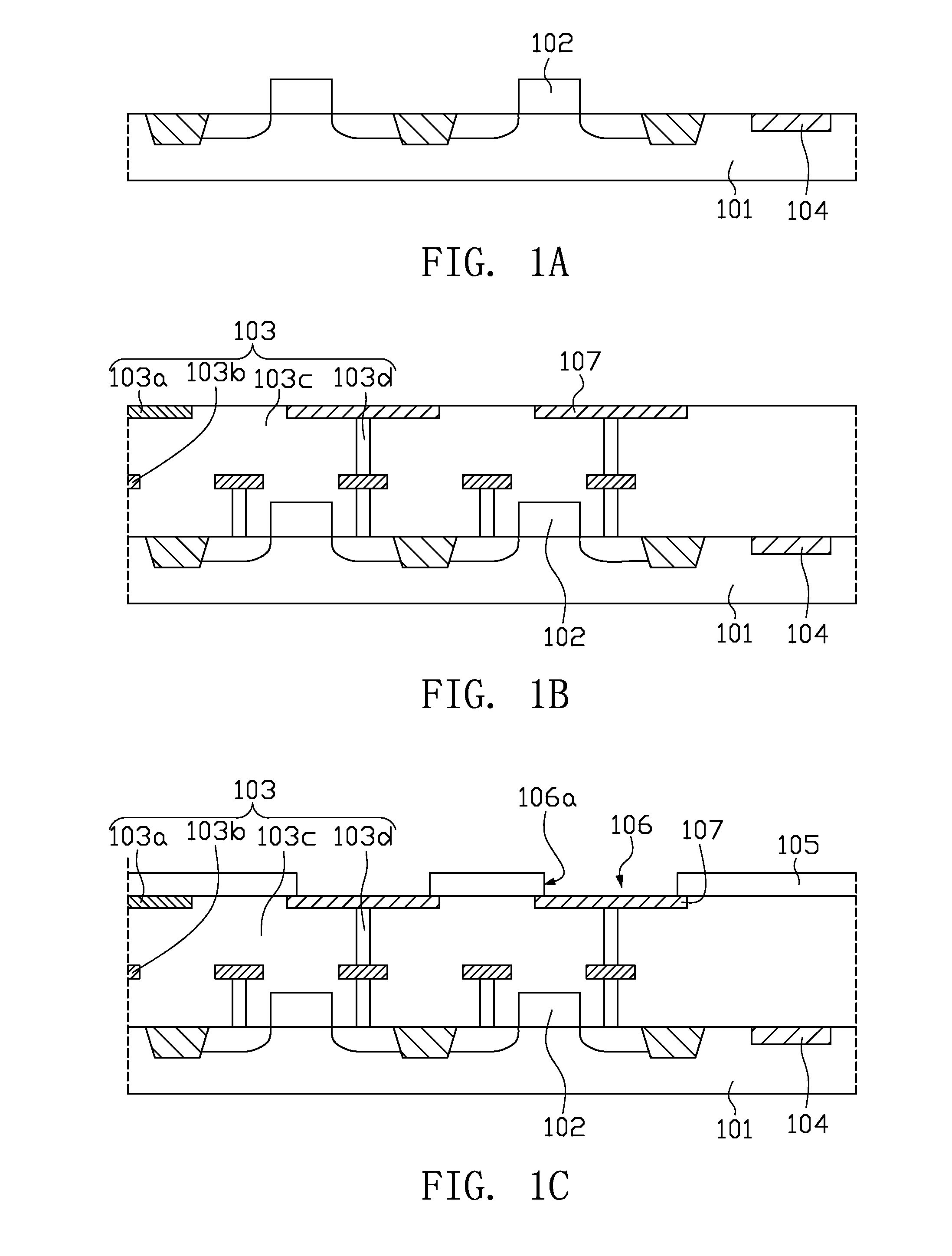

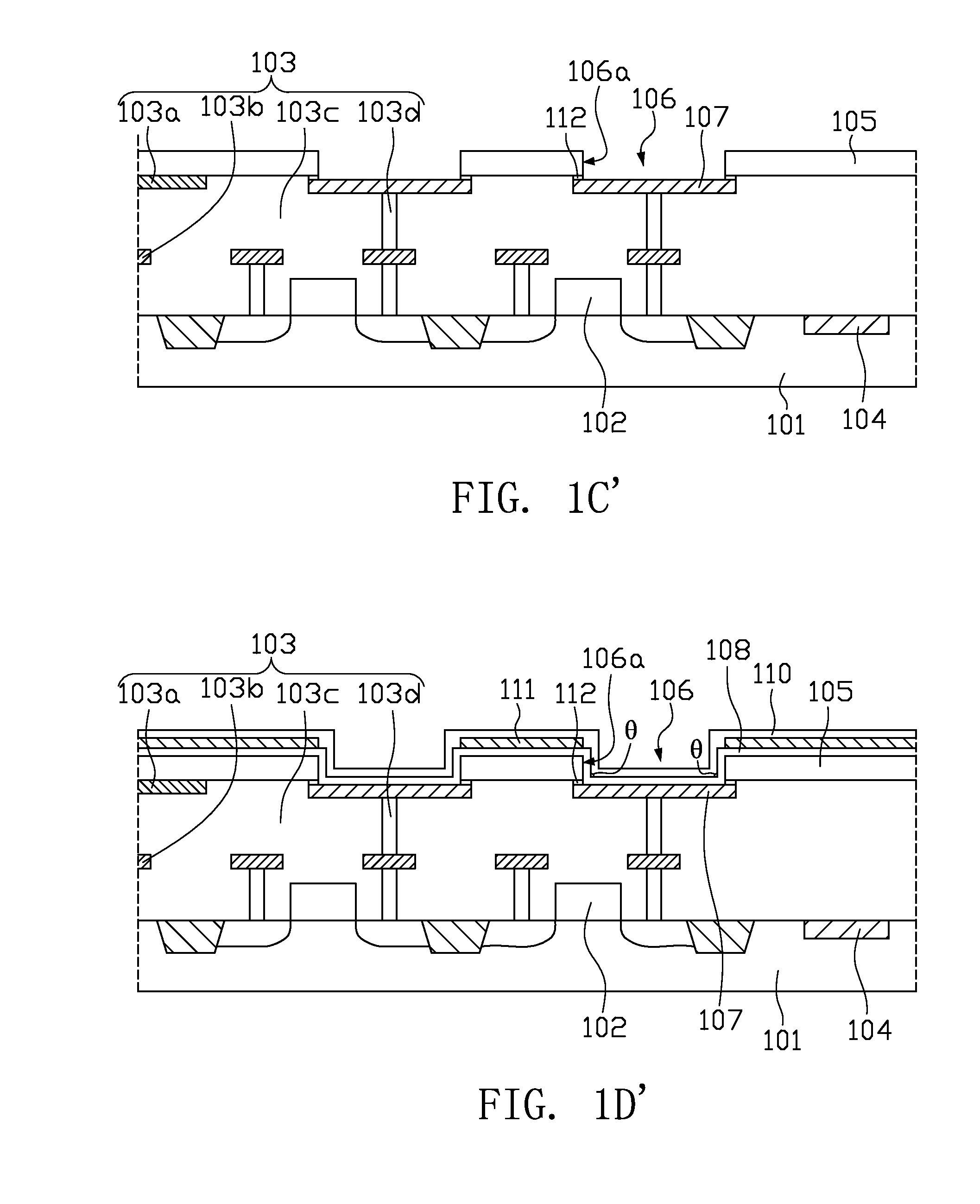

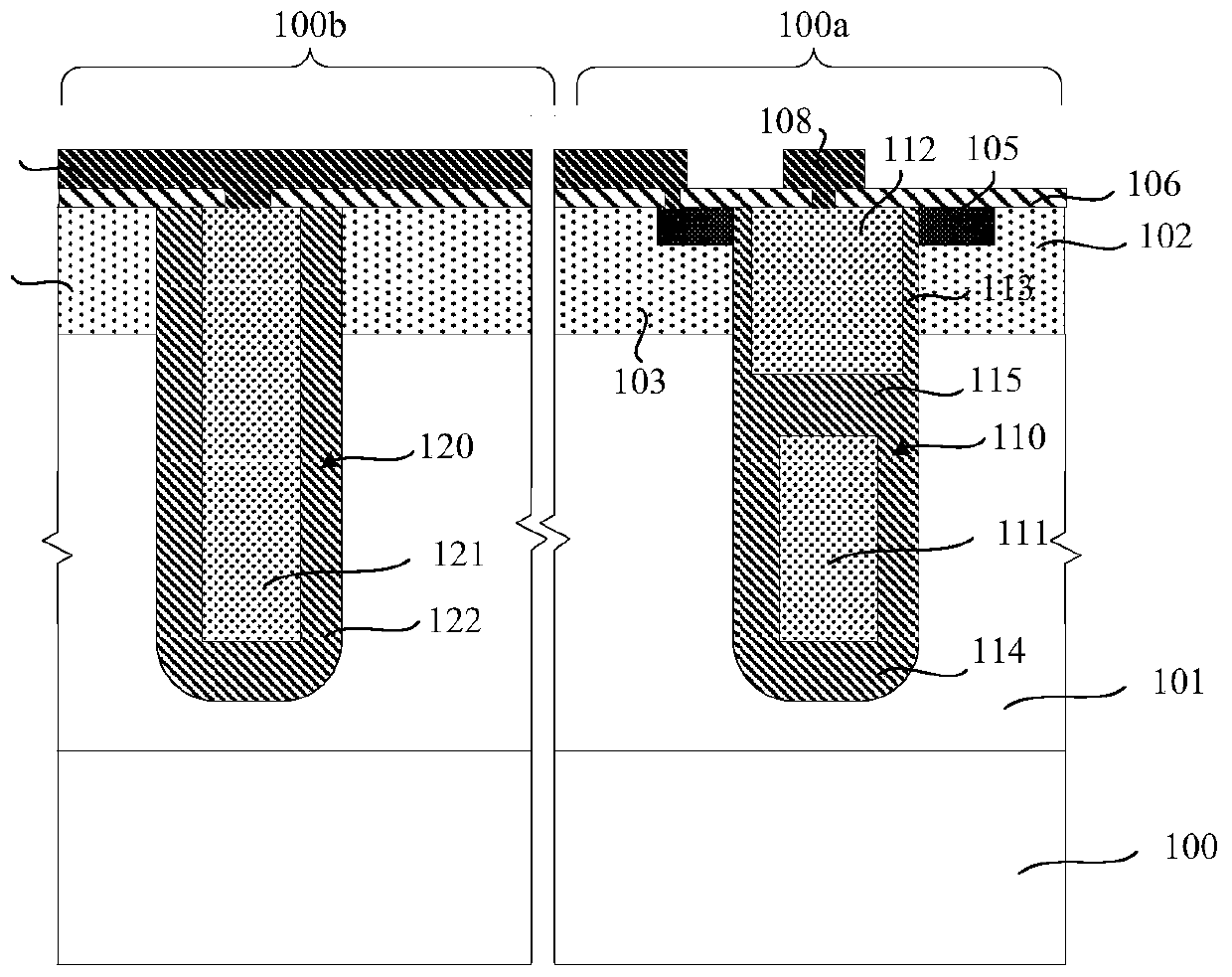

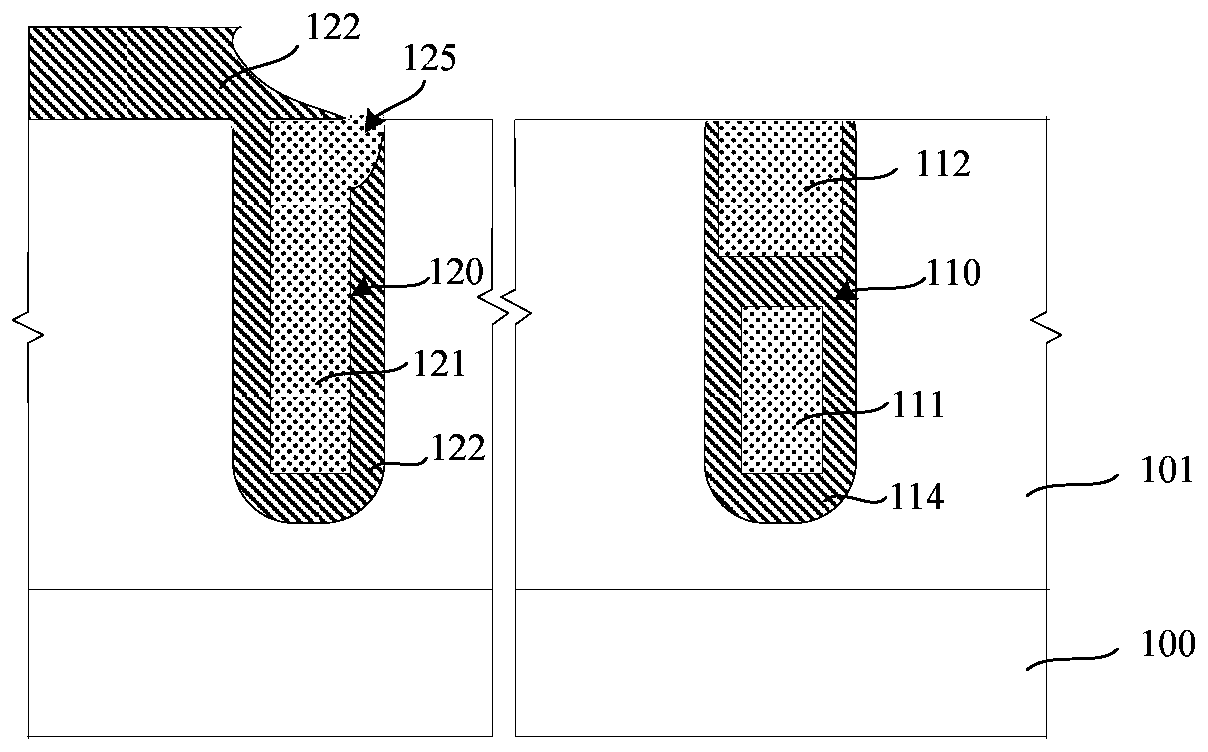

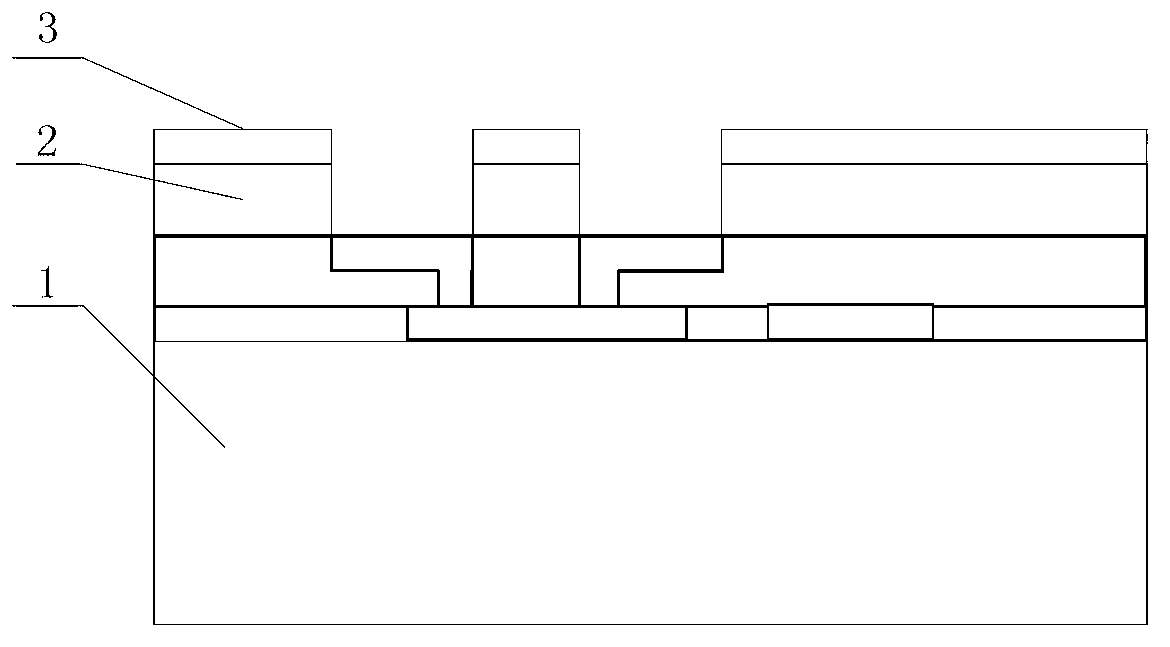

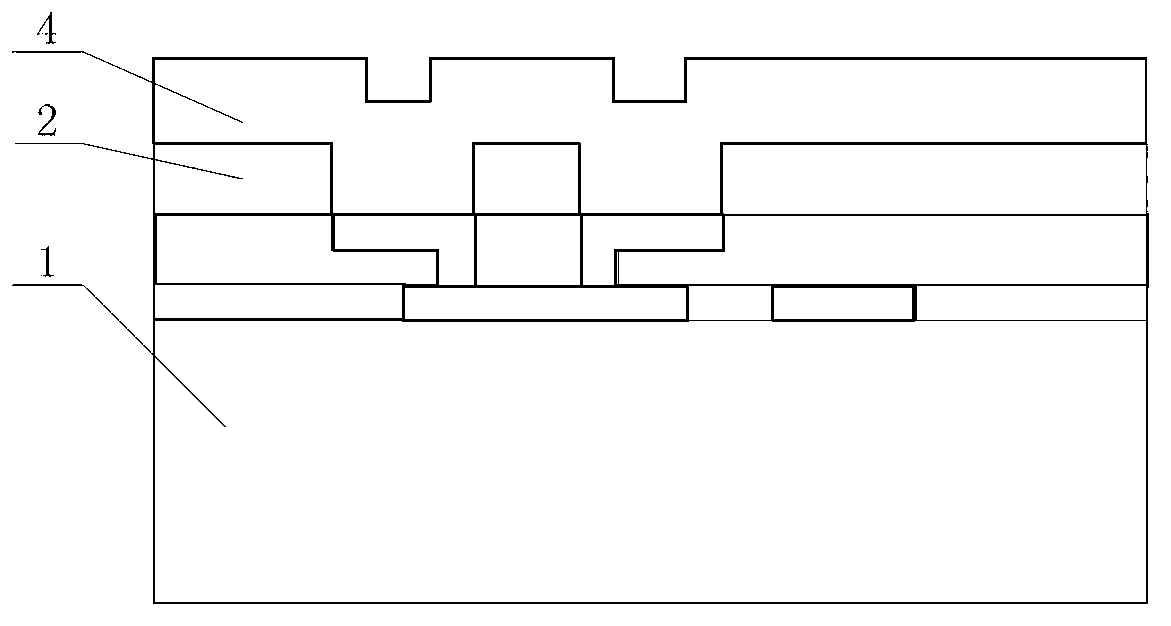

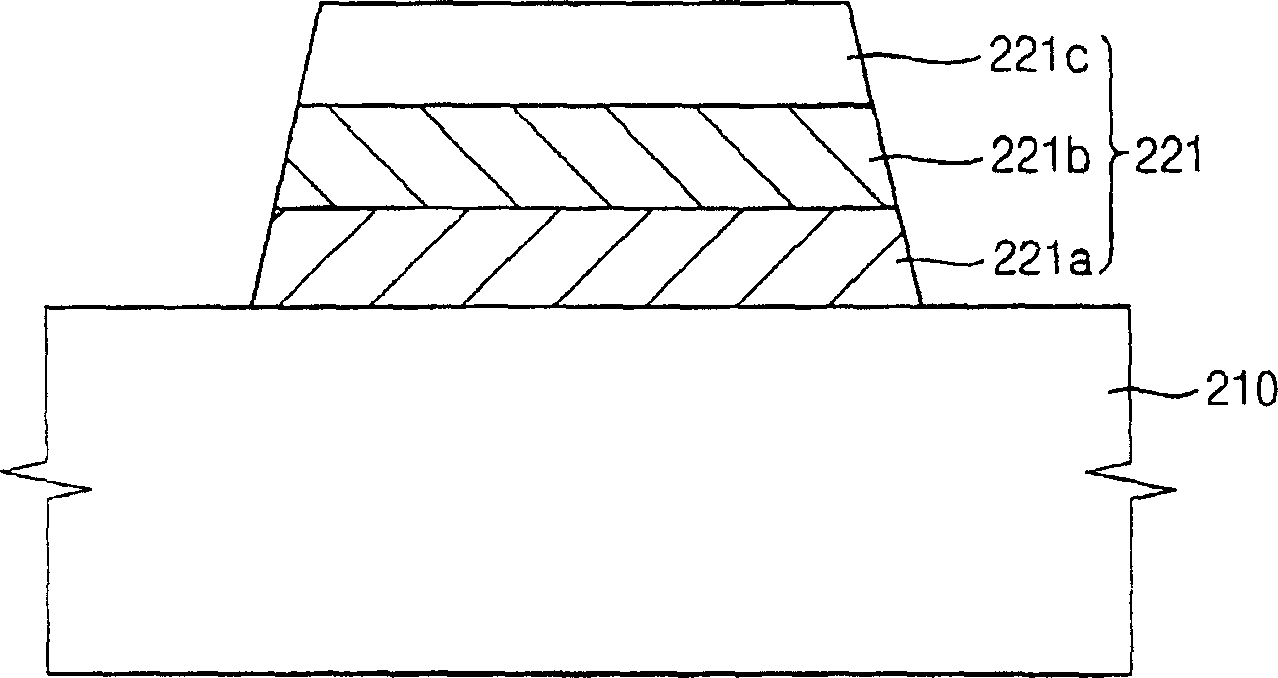

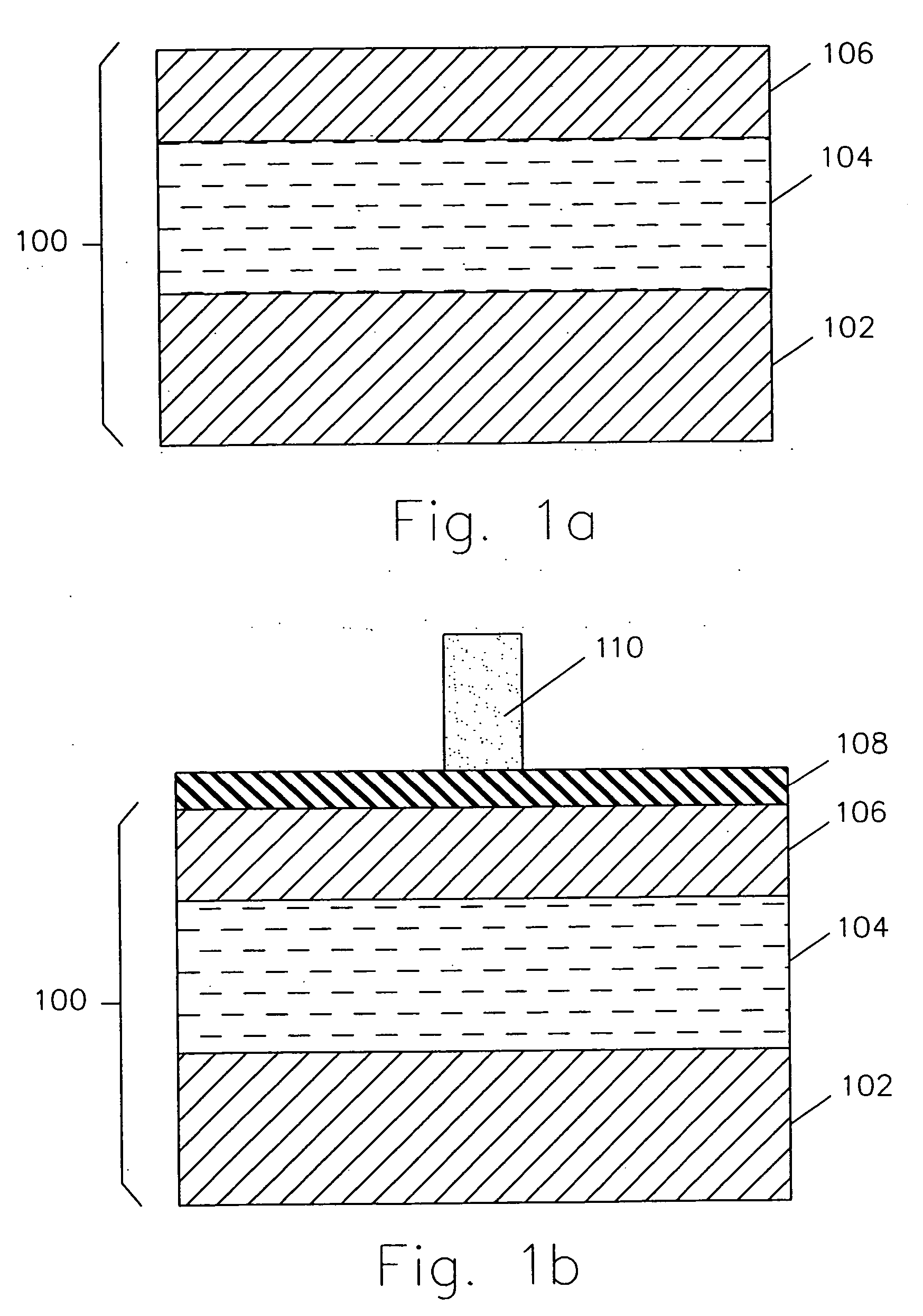

Semiconductor structure forming method

ActiveCN105097657AAvoid undercutInhibit sheddingSemiconductor/solid-state device manufacturingSemiconductor structureDielectric layer

The invention relates to a semiconductor structure. A semiconductor structure forming method comprises the following steps of providing a substrate; forming a carbon-containing dielectric layer on the surface of the substrate; forming a carbon-rich protecting layer on the surface of the carbon-containing dielectric layer, wherein the carbon atom concentration in the carbon-rich protecting layer material is greater than that in the carbon-containing dielectric layer material; forming a graphical hard mask layer on the surface of the carbon-rich protecting layer; and with the graphical hard mask layer as a mask, etching the carbon-rich protecting layer and the carbon-containing dielectric layer to form an opening, wherein the opening bottom makes the substrate surface exposed; and forming a metal layer filling the opening. An undercut phenomenon is prevented. The quality of the formed metal layer is improved. The performance of the semiconductor structure is further optimized.

Owner:SEMICON MFG INT (SHANGHAI) CORP

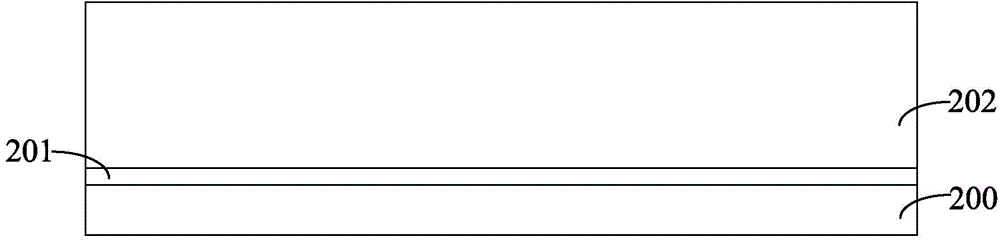

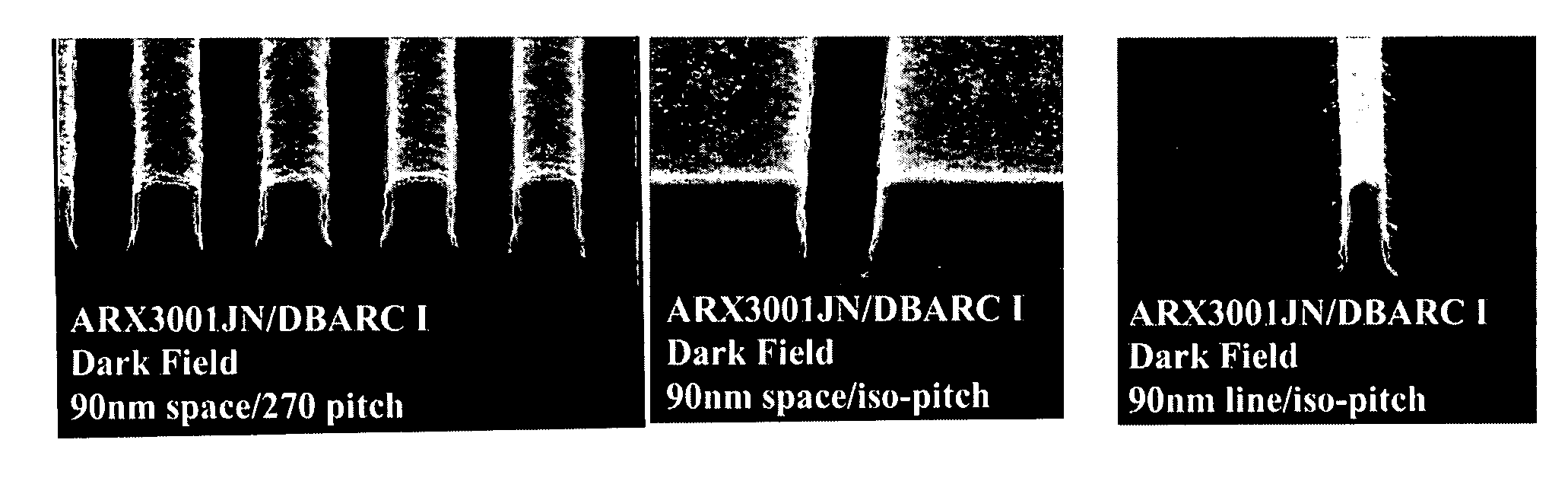

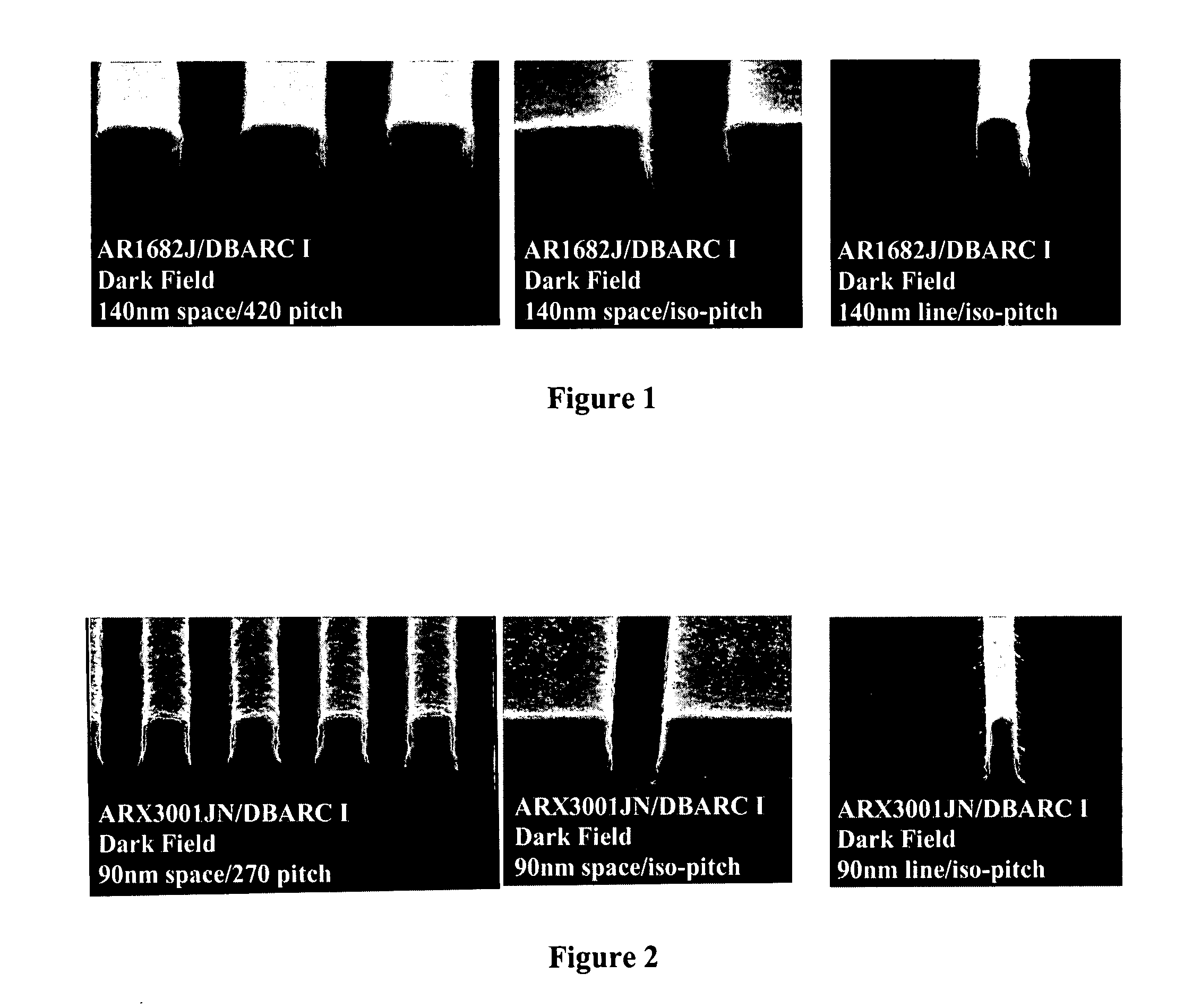

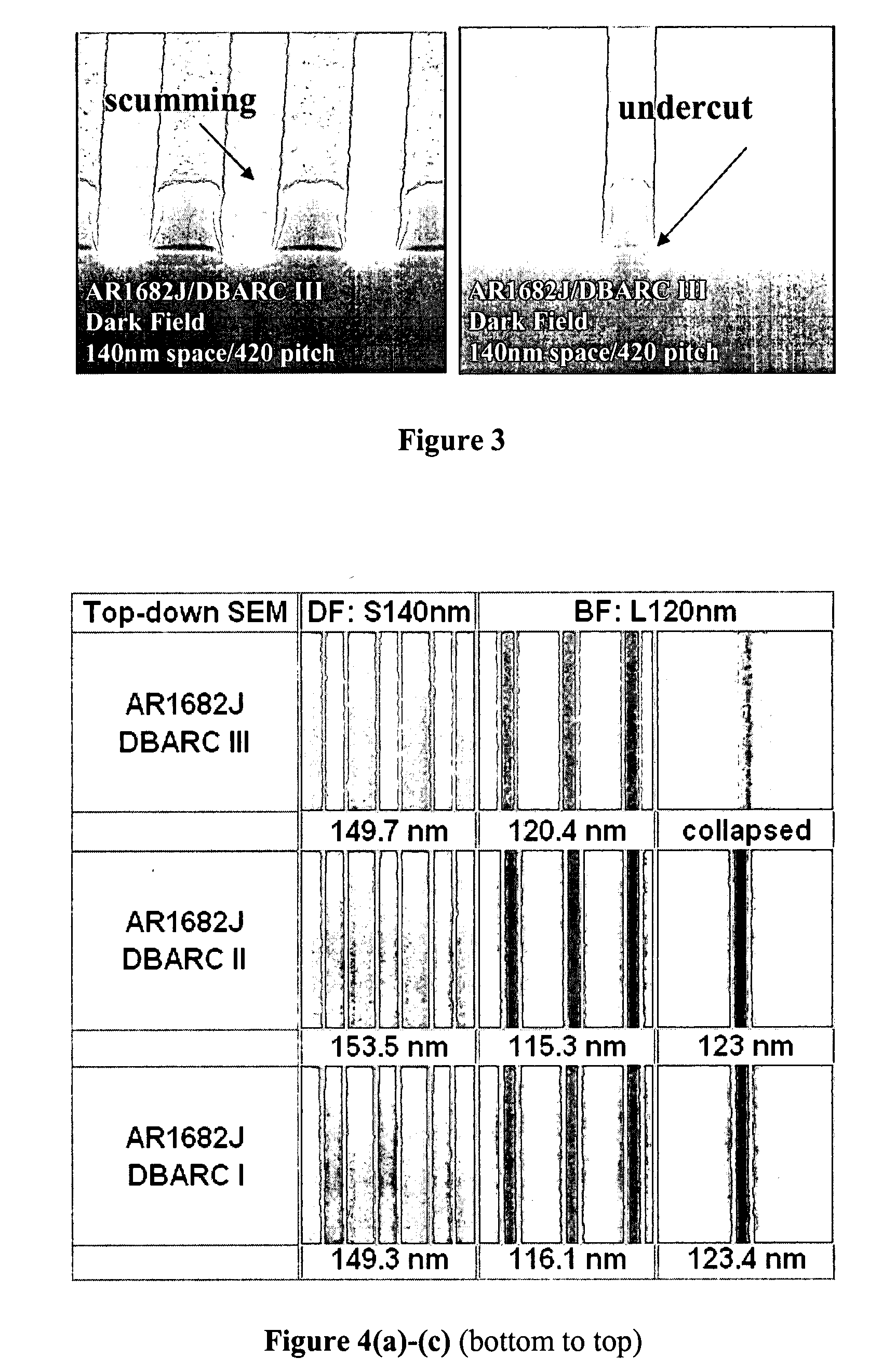

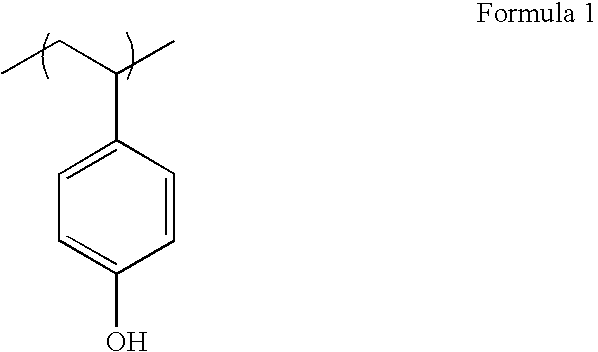

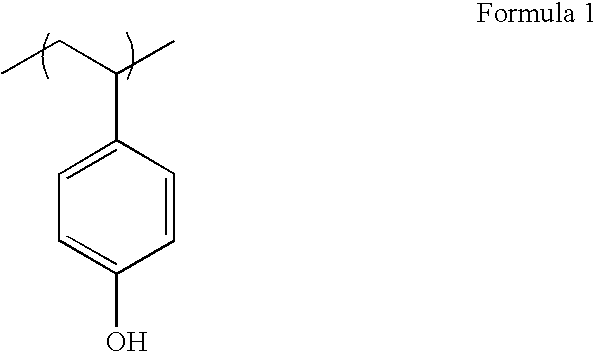

Radiation-Sensitive, Wet Developable Bottom Antireflective Coating Compositions and Their Applications in Semiconductor Manufacturing

InactiveUS20090098490A1Eliminates scummingReduce scumPhotosensitive materialsPhotomechanical apparatusPhotoacidPhotoacid generator

The present invention is directed to novel radiation-sensitive, wet developable bottom antireflective coating (DBARC) compositions and their use in semiconductor device manufacturing. The DBARC compositions contain a photoacid generator that produces a photoacid upon exposure to activating radiation. In a photolithographic imaging process, the relatively strong photoacid reduces or eliminates scumming. Further, the relatively large size of the photoacid limits its diffusion through the DBARC, thus minimizing or preventing undercut. The inventive method also limits diffusion of the photoacid by controlling the temperature of the post-exposure baking step. Use of the DBARC compositions with a photoresist in photolithography results in highly resolved features having essentially vertical profiles and no scumming and no undercut, which is critical as microelectronics and semiconductor components become increasingly miniaturized.

Owner:JSR MICRO

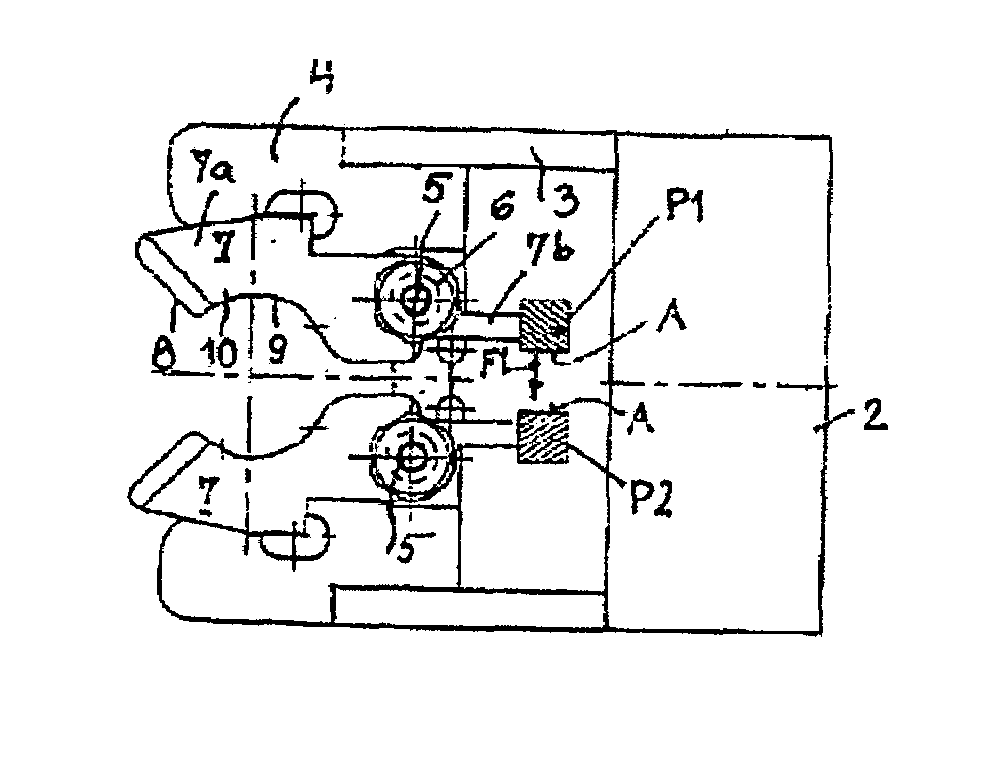

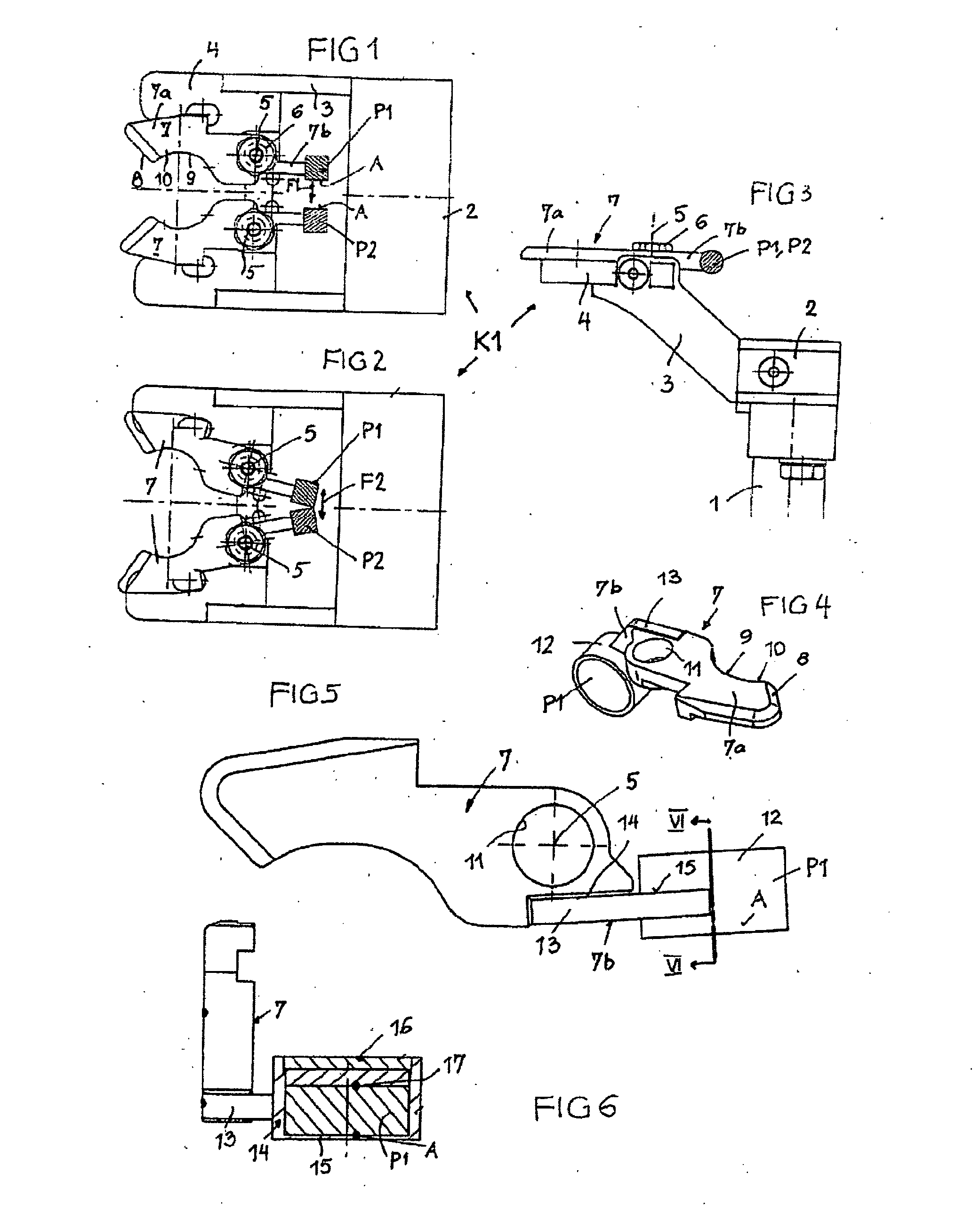

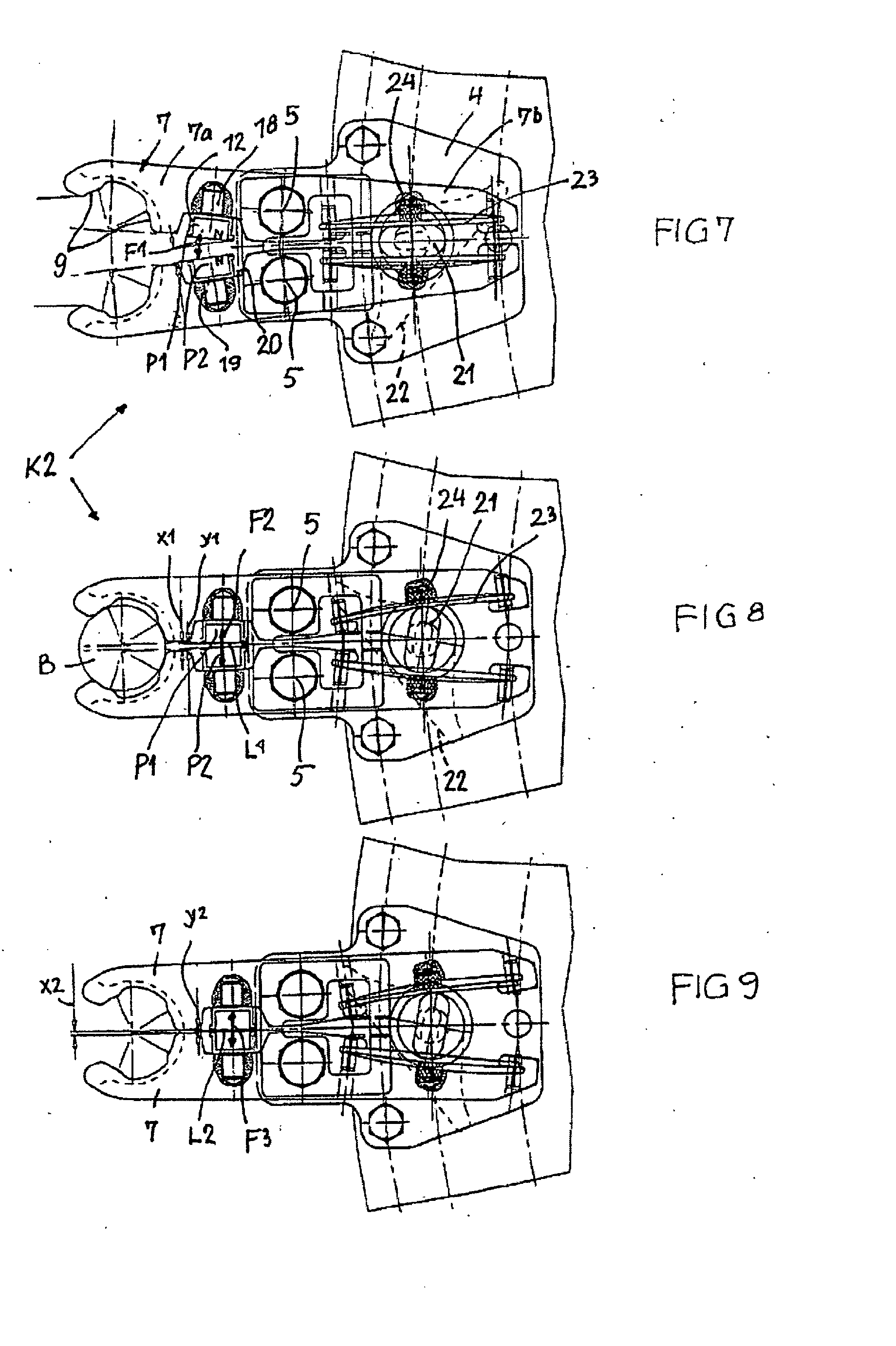

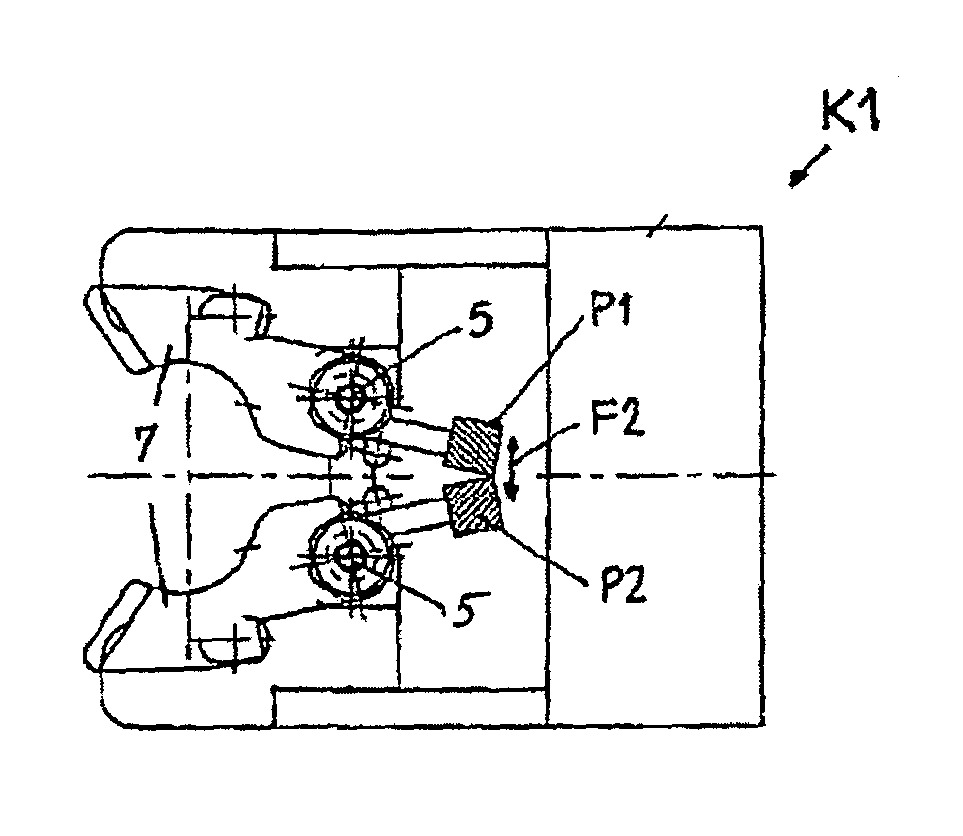

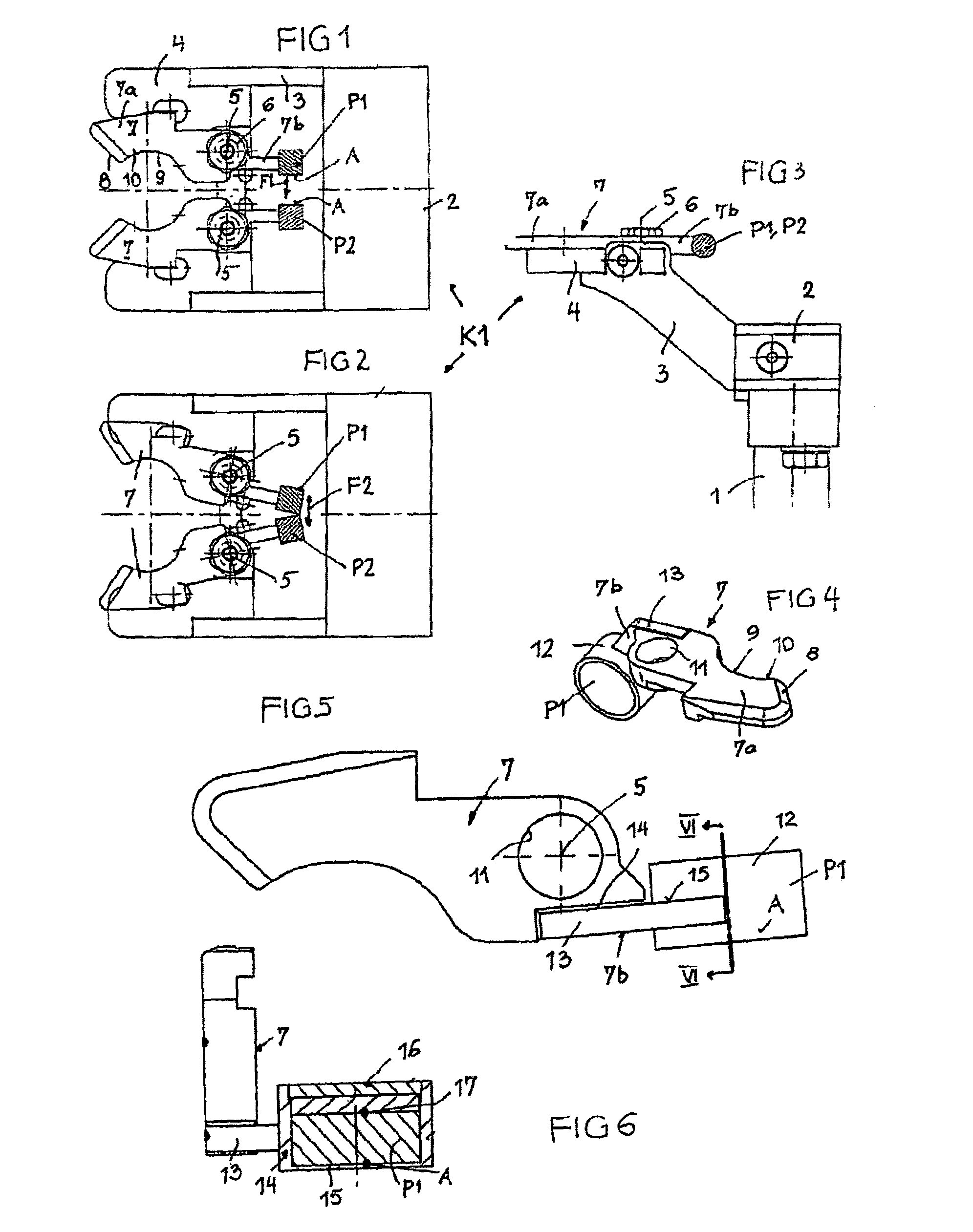

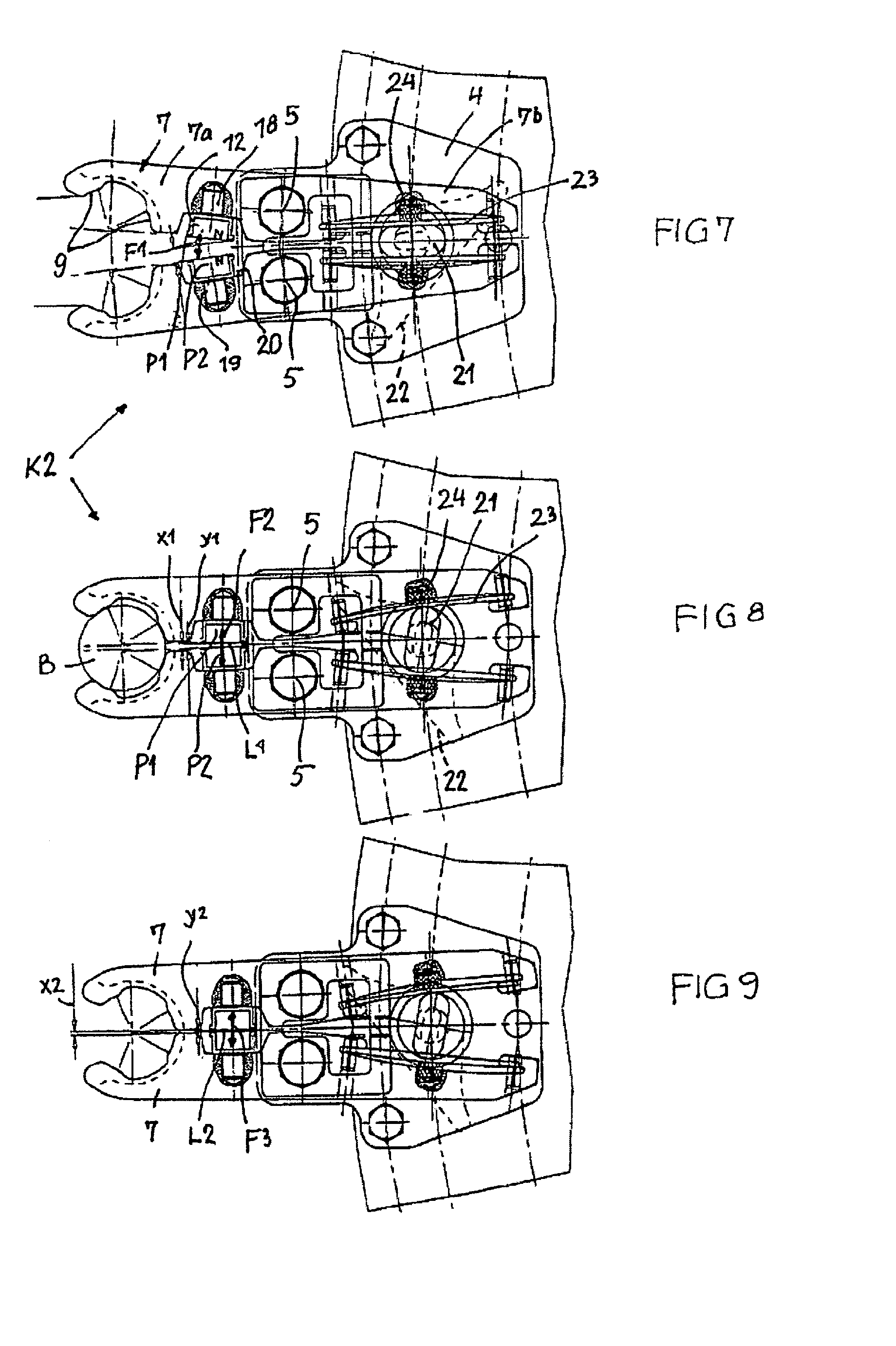

Claw for a Container Transporting System

A clamp grip for a container transport system including rare earth permanent magnets encapsulated in non-magnetic material such as high quality steel. Flexible positioning of the magnets allow for adapting to varied design specifications. A rotatable control cam or cams may be used to adjust grip arms between a grip and a release position. Air gap distances between permanent magnets may be designed to maximize repelling force to assist in the functioning of clamp grip mechanism.

Owner:KRONES AG

Bond pad structure and fabricating method thereof

ActiveUS20130093104A1Excellent etch resistanceAvoid undercutSemiconductor/solid-state device detailsSolid-state devicesIsolation layerInterconnection

A bond pad structure comprises an interconnection structure and an isolation layer. The dielectric layer has an opening and a metal pad. The isolation layer is disposed on the interconnection structure and extends into the opening until it is in contact with the metal pad, whereby the sidewalls of the opening is blanketed by the isolation layer, and a portion of the metal pad is exposed from the opening.

Owner:MARLIN SEMICON LTD

Claw for a container transporting system

A clamp grip for a container transport system including rare earth permanent magnets encapsulated in non-magnetic material such as high quality steel. Flexible positioning of the magnets allow for adapting to varied design specifications. A rotatable control cam or cams may be used to adjust grip arms between a grip and a release position. Air gap distances between permanent magnets may be designed to maximize repelling force to assist in the functioning of clamp grip mechanism.

Owner:KRONES AG

Electromagnetic excited TIG arc melting-brazing hybrid welding method and equipment

InactiveCN101862873AAvoid severe burnsLow heat inputSoldering apparatusMetal working apparatusMetallic materialsWelding defect

The invention discloses an electromagnetic excited TIG arc melting-brazing hybrid welding method and equipment. In addition to the use of the welding zone, an alternating magnetic field is added to control properties of a welding arc, and the assistant effect on the melting bath of the liquid-state brazing filler metal for arc melting-brazing is realized through electromagnetic stirring and excitation and enhancement, thereby promoting the orderly flow of the liquid-state brazing filler metal and the rupture, wetting, spreading and proliferation of the liquid-state brazing filler metal on the surface of the high metal material, improving the full mixing of the liquid-state brazing filler metal and the base metal formed by melting the low-melting-point metal material, improving the uniformity of the components of the brazed weld, reducing welding defects, increasing the welding speed, improving the weld formation, optimizing the structure and performance of the brazed weld, and improving the quality of the brazed joint. Moreover, the equipment has the advantages of simple structure, flexible application, low cost, good effect and easy realization.

Owner:CHONGQING UNIV

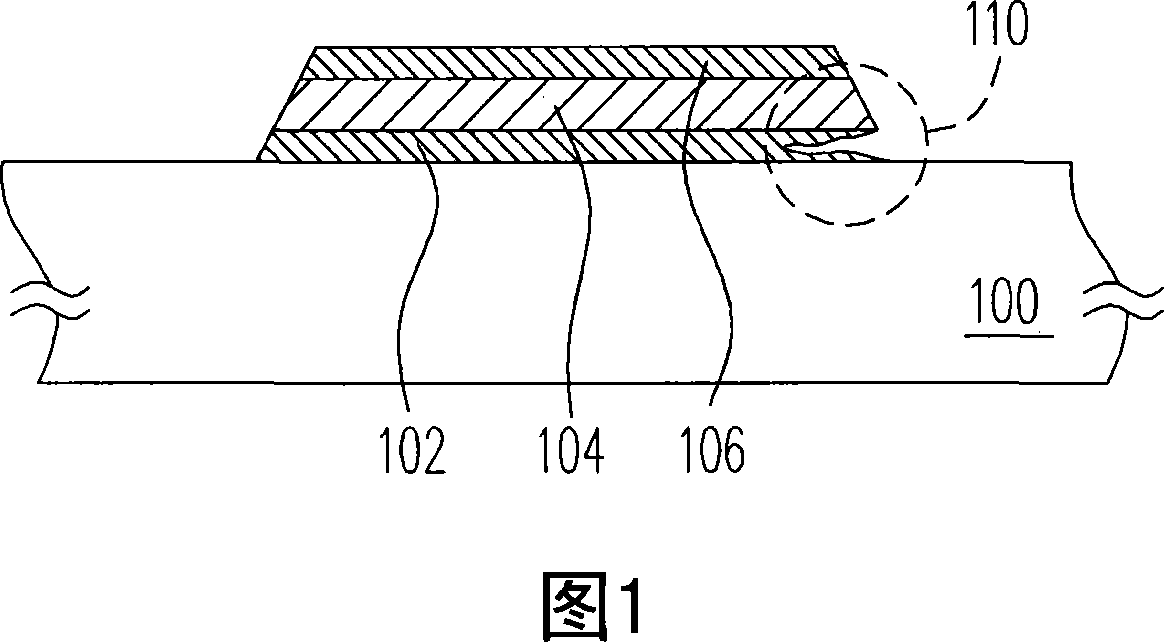

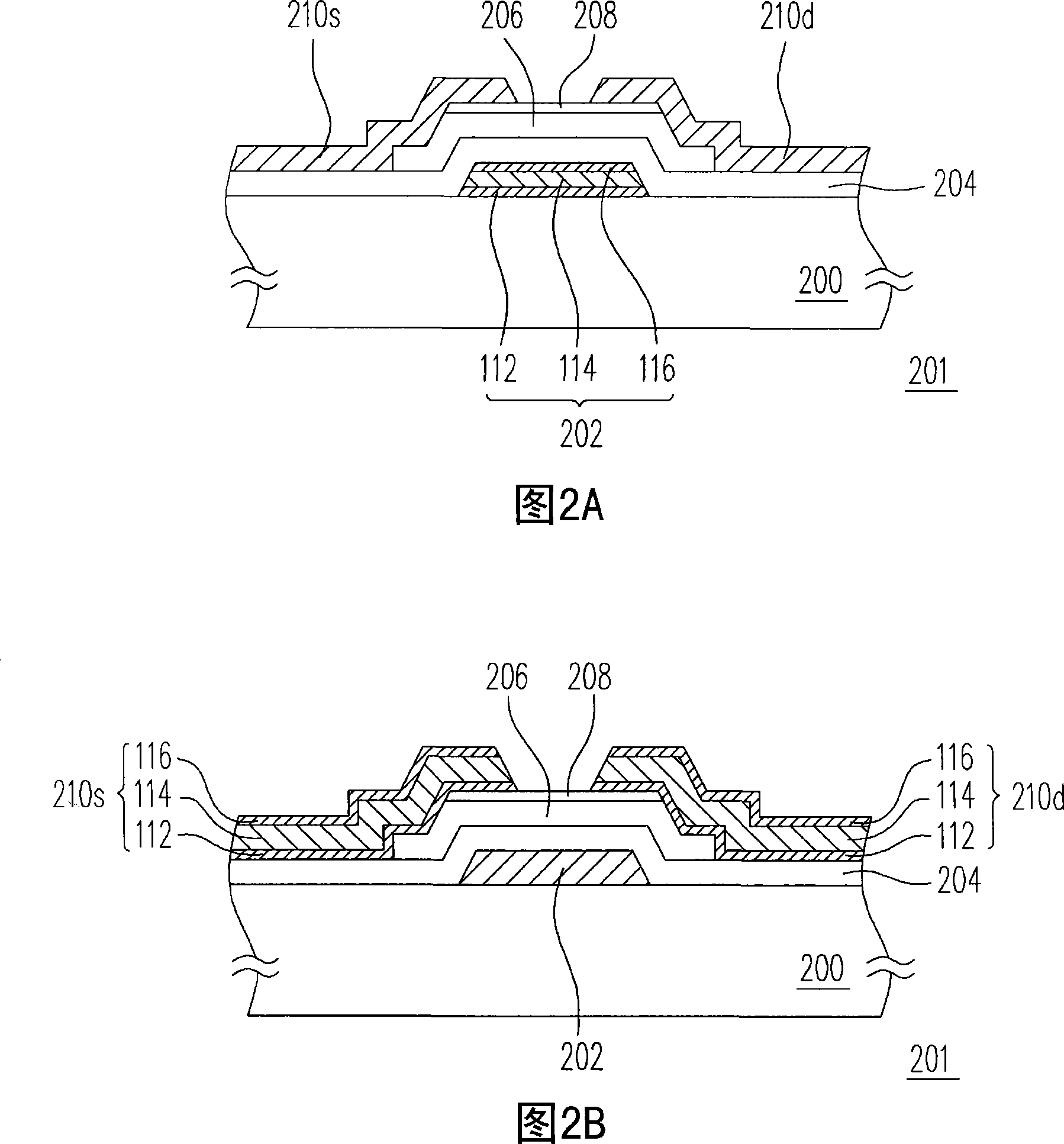

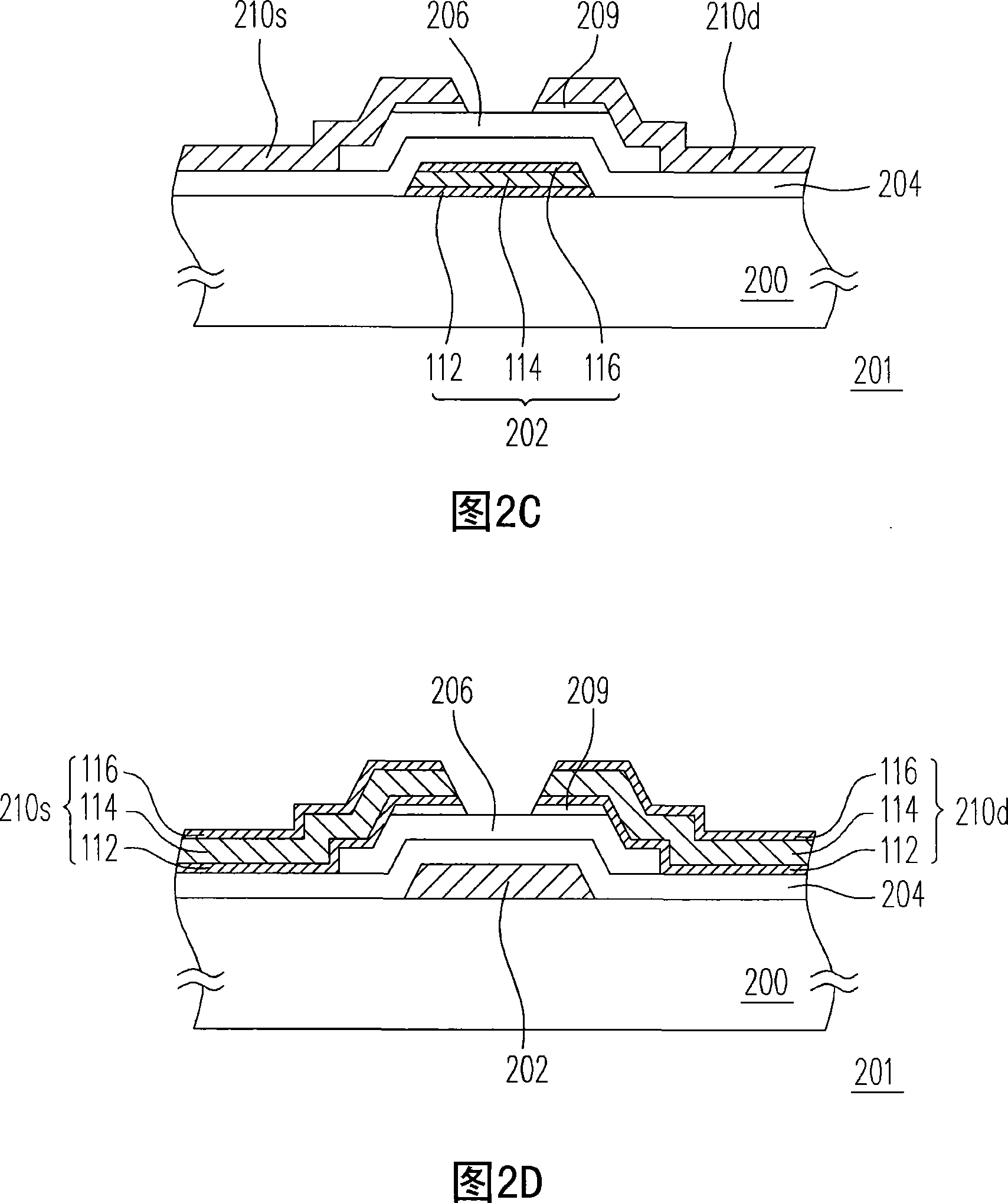

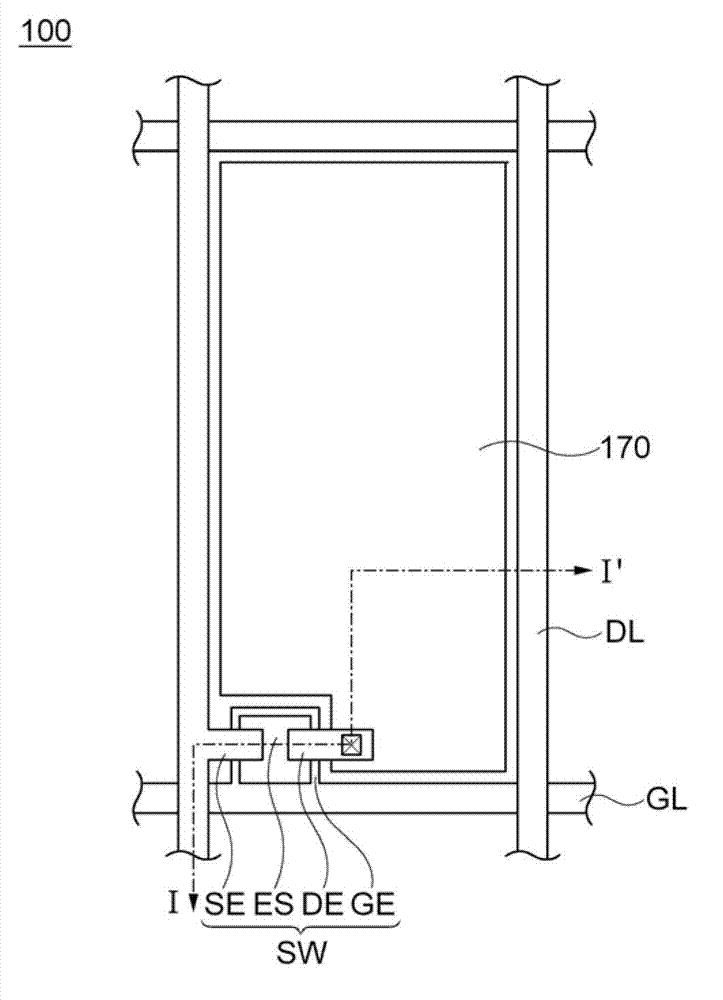

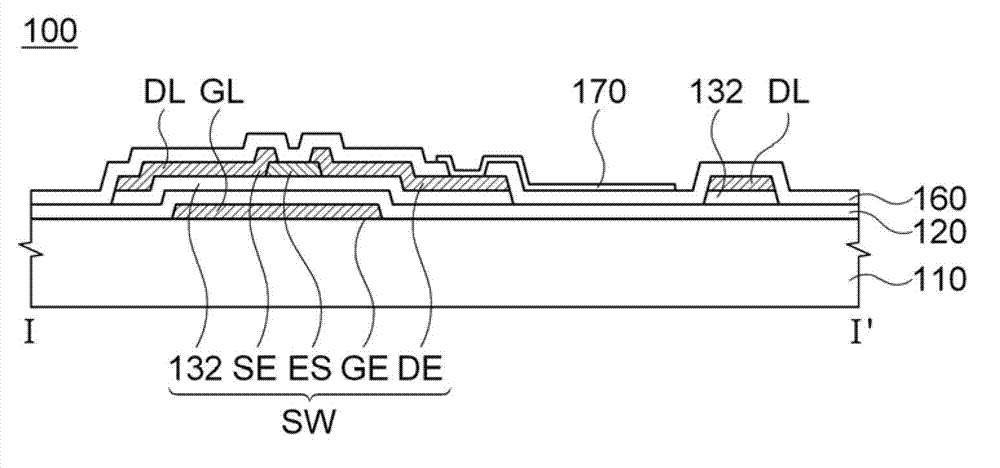

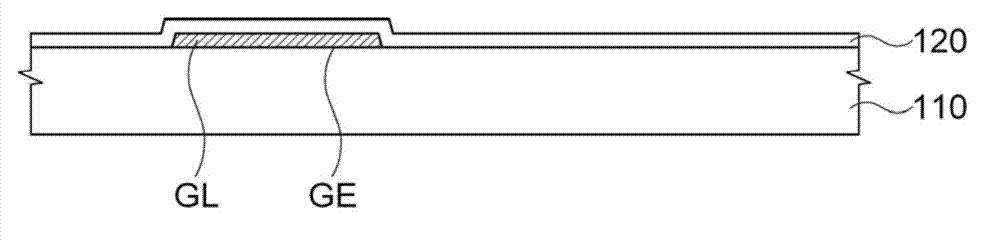

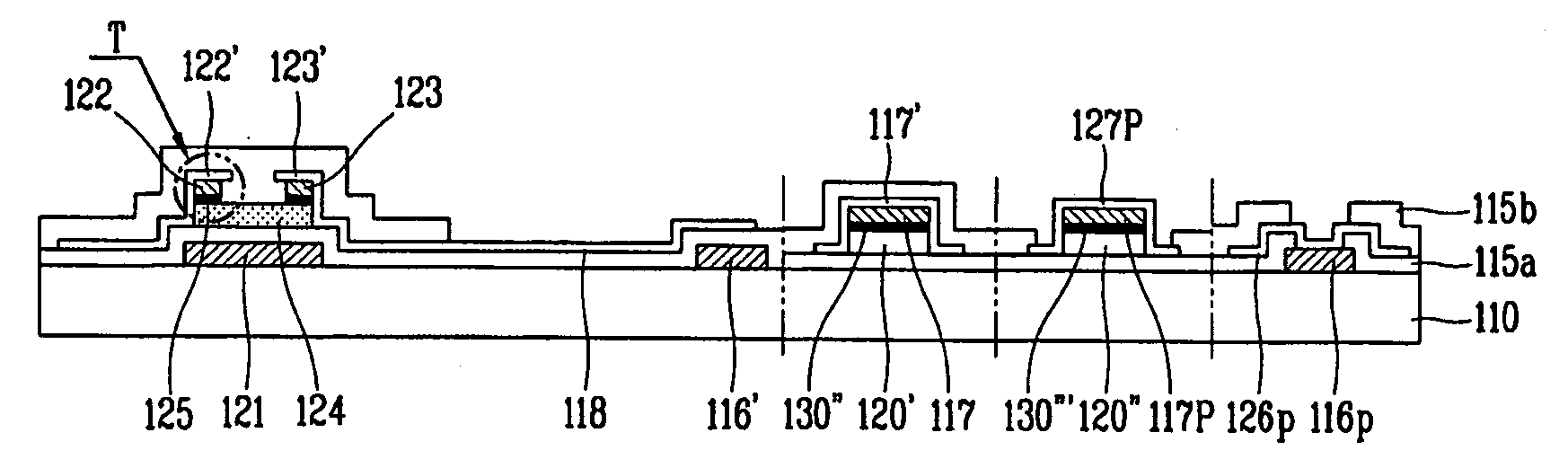

Thin-film transistor, active element array substrate as well as liquid crystal display panel

InactiveCN101226964AAvoid undercutGuaranteed display qualityTransistorSolid-state devicesLiquid-crystal displayEngineering

The invention discloses a thin film transistor, an active element array base plate and a liquid crystal display panel, wherein the thin film transistor comprises a base plate, a gate, a gate insulating layer, a channel layer, a source electrode and a drain electrode, the gate and the gate insulating layer are arranged on the base plate, and the gate insulating layer is covered on the gate. The channel layer is arranged on the gate insulating layer which is arranged on the upper of the gate, and the source electrode and the drain electrode are respectively arranged on a part of the channel layer, which are arranged on the two sides of the gate. At least one of the gate, the source electrode and the drain electrode is equipped with a conductive interlayer which is equipped with a bottom conductive layer and a top conductive layer and is located between the bottom conductive layer and the top conductive layer, the materials of the bottom conductive layer and the top conductive layer are different, and substantially, the thickness of the bottom conductive layer is smaller or equal to 150 angstrom. An electrode with the above structure is capable of avoiding that the gate, the source electrode and the drain electrode produce an undercut phenomenon during processing, thereby corresponding thin film transistors are capable of normally operating to maintain the element characteristics and the normal operation of a pixel and further maintain the display quality of the corresponding liquid crystal display panel.

Owner:AU OPTRONICS CORP

Etching liquid for copper nickel multilayer film

The invention relates to etching liquid capable of selectively etching a copper nickel multilayer film in a semiconductor device with an oxide semiconductor layer and the copper nickel multilayer film. The etching liquid contains hydrogen peroxide, an etching inhibitor, a chelating agent, organic acid, a hydrogen peroxide stabilizer, a pH modifier and a water medium; according to total weight of the etching liquid, hydrogen peroxide is 5-30%; according to total weight of the etching liquid, the etching inhibitor is 0.01-5%; according to total weight of the etching liquid, the chelating agent is 0.1-5%; according to total weight of the etching liquid, the organic acid is 1-10%; according to total weight of the etching liquid, the hydrogen peroxide stabilizer is 0.01-0.1%; the content of the pH modifier enables the pH value of the etching liquid to be 3-5; and the balance is the water medium. After etching by the etching liquid, the wiring section shape is excellent, and the undercutting phenomenon can be effectively prevented.

Owner:惠州达诚微电子材料有限公司

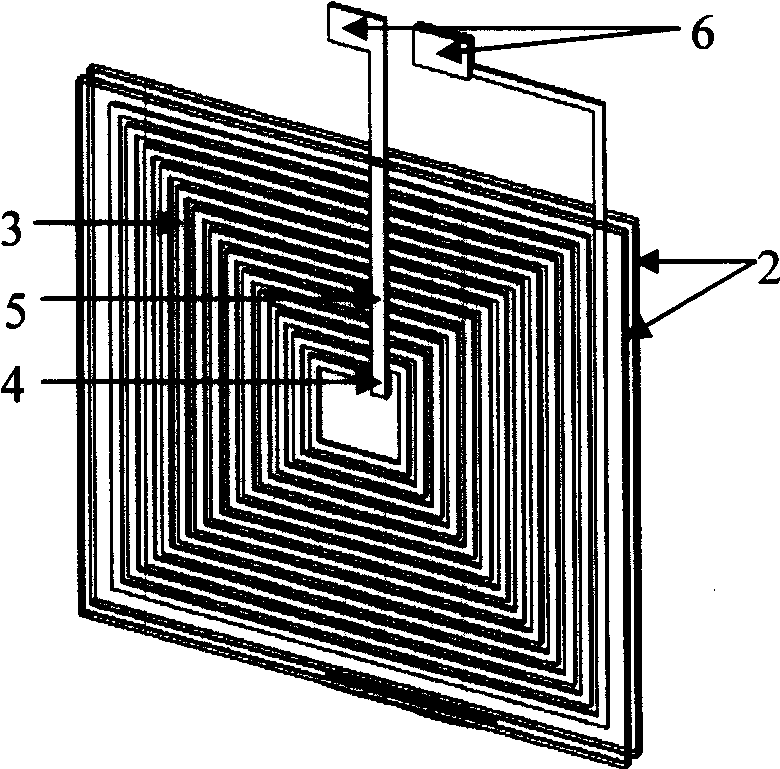

Micro-inductor device in planar magnetic core helical structure and preparation thereof

InactiveCN101477873AIncrease working frequencySmall sizeTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresSputteringInductor

The invention relates to a micro-inductor with a planar core helical structure, and a preparation method thereof, which belong to the microelectronic technical field. The micro-inductor comprises a substrate, a magnetic core material, an insulating material, a coil with a planar helical structure, pins and lead wires, wherein, the coil with the planar helical structure is wrapped by two layers of core material and separated by polyimide; and a central pin is connected with external pins. The process is as follows: sputtering of a layer of Cr, whirl coating, photoetching, developing, etching and overlay alignment symbols making; bonding of the magnetic core material, whirl coating, photoetching, developing, etching of the magnetic core material; fling, drying and solidifying of polyimide, and polishing; sputtering, whirl coating, photoetching, developing, galvanization, and manufacturing of the coil with a planar helical structure, lead wires and pins; fling, drying and solidifying of polyimide, and polishing; sputtering of a layer of Ti, whirl coating, photoetching, developing and etching; and bonding of the magnetic core material, whirl coating, photoetching, developing, and etching of the magnetic core material. The method greatly reduces the high-frequency loss of the micro-inductor and effectively improves the high-frequency property thereof.

Owner:SHANGHAI JIAO TONG UNIV

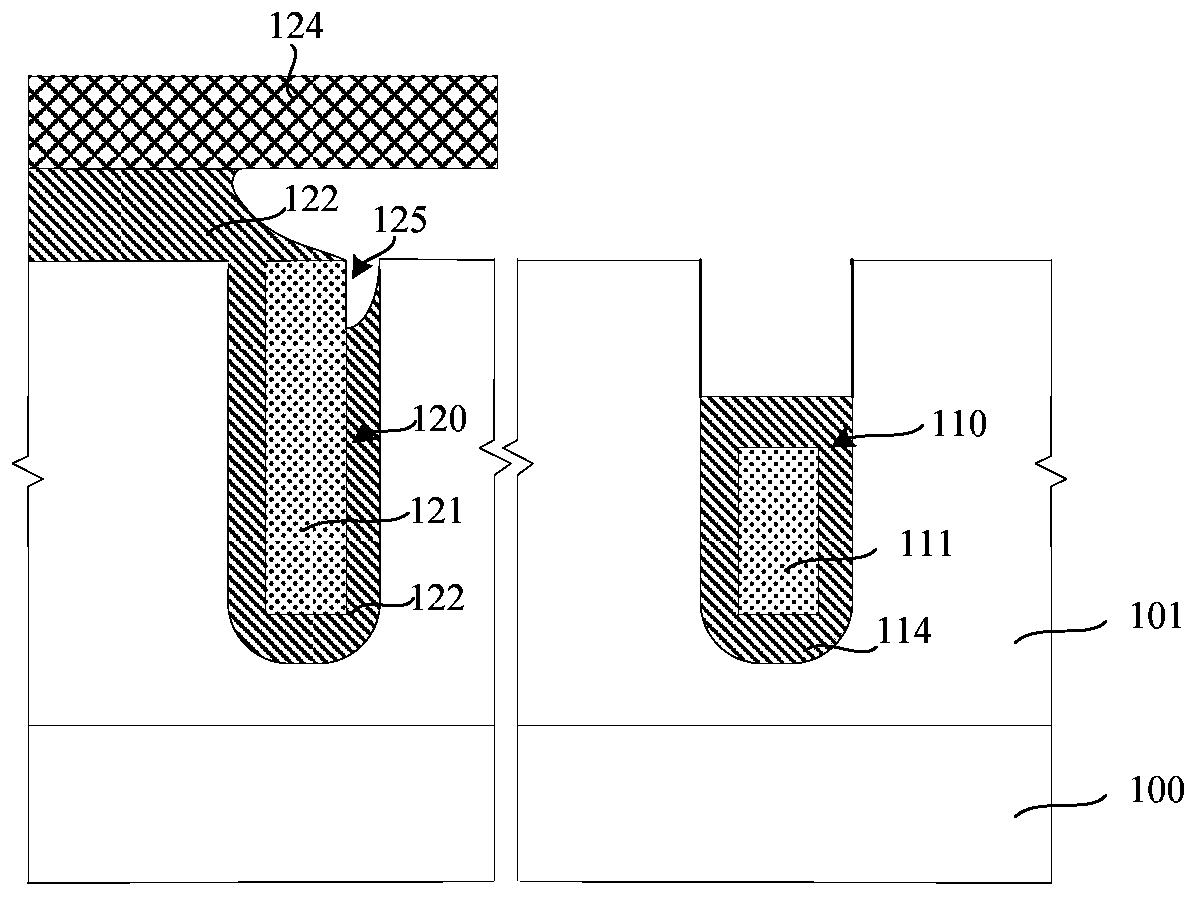

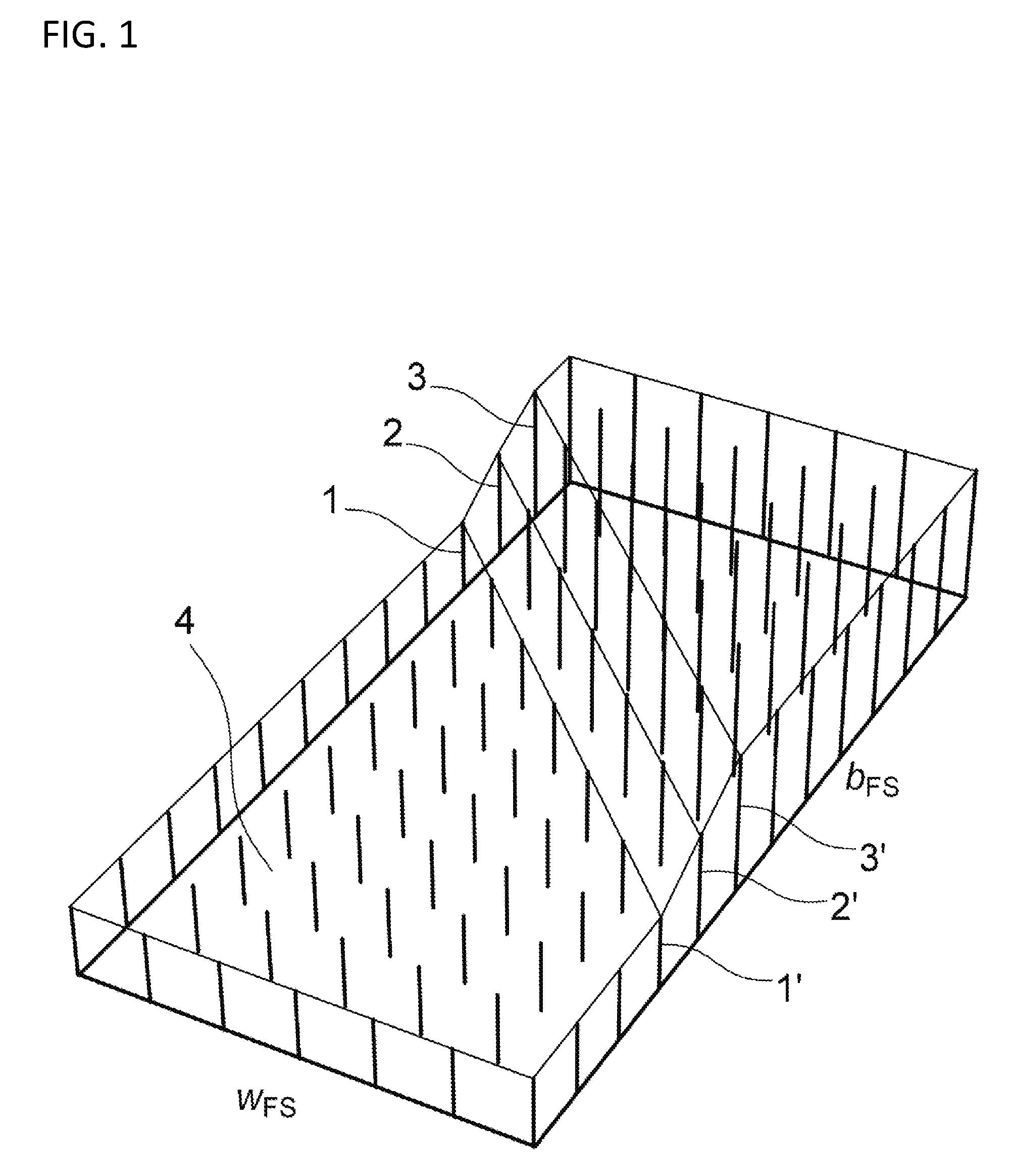

Manufacturing method of shield gate trench power device

PendingCN111081540AShorten process timeAvoid undercutting problemsSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsElectrically conductive

The invention provides a manufacturing method of a shield gate trench power device. The method comprises the following steps of: providing a substrate, forming at least one first trench in a device unit region of the substrate, forming at least one second trench in an electrode connection region of the substrate, and forming first dielectric layers on the side walls and the bottoms of the first trench and the second trench; forming a shielding gate in the first trench, partially filling the first trench with the shielding gate, and filling the second trench with a conductive material; forminga second dielectric layer which fills the first trench and covers the surface of the substrate and the conductive material; removing the second dielectric layer on the device unit region by adopting adry isotropic etching process, and exposing a part of the first trench; forming a gate in the first trench. According to the invention, before the gate is formed, the second dielectric layer on the device unit region is removed through dry isotropic etching, and part of the first trench is exposed, so that compared with the traditional wet etching removal, the process time is shortened, and the undercutting problem is effectively reduced and even avoided.

Owner:GUANGZHOU CANSEMI TECH INC

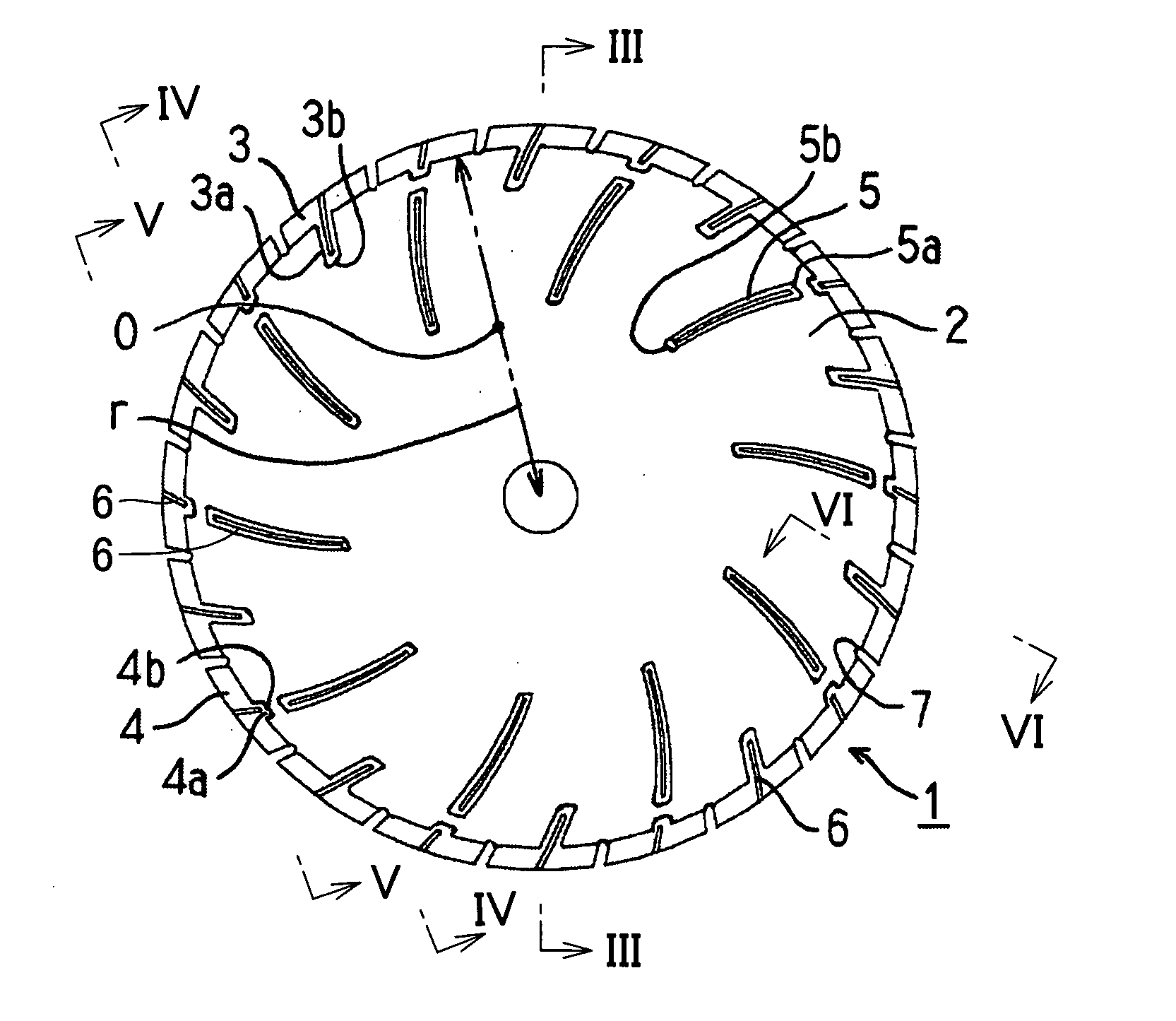

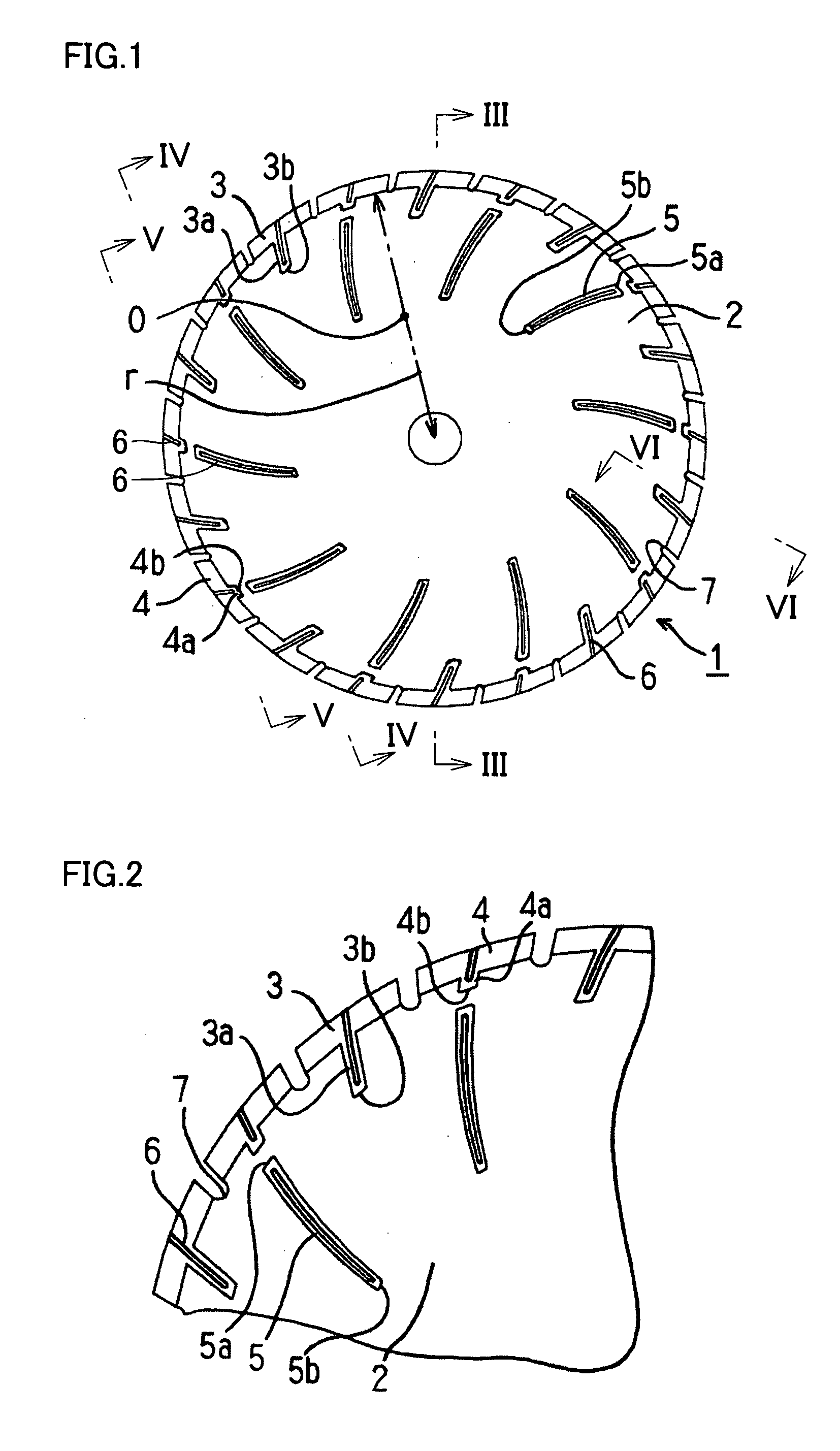

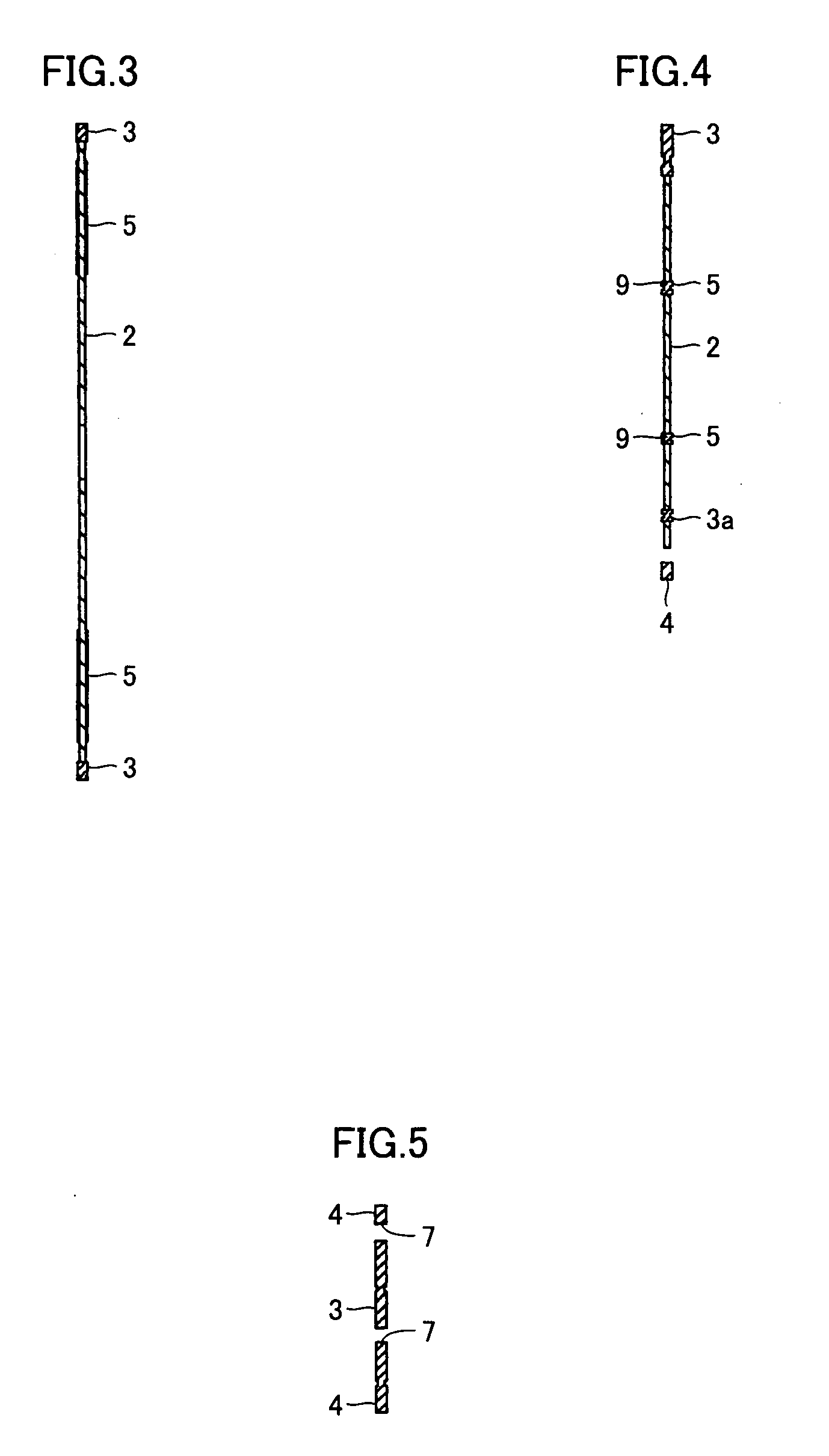

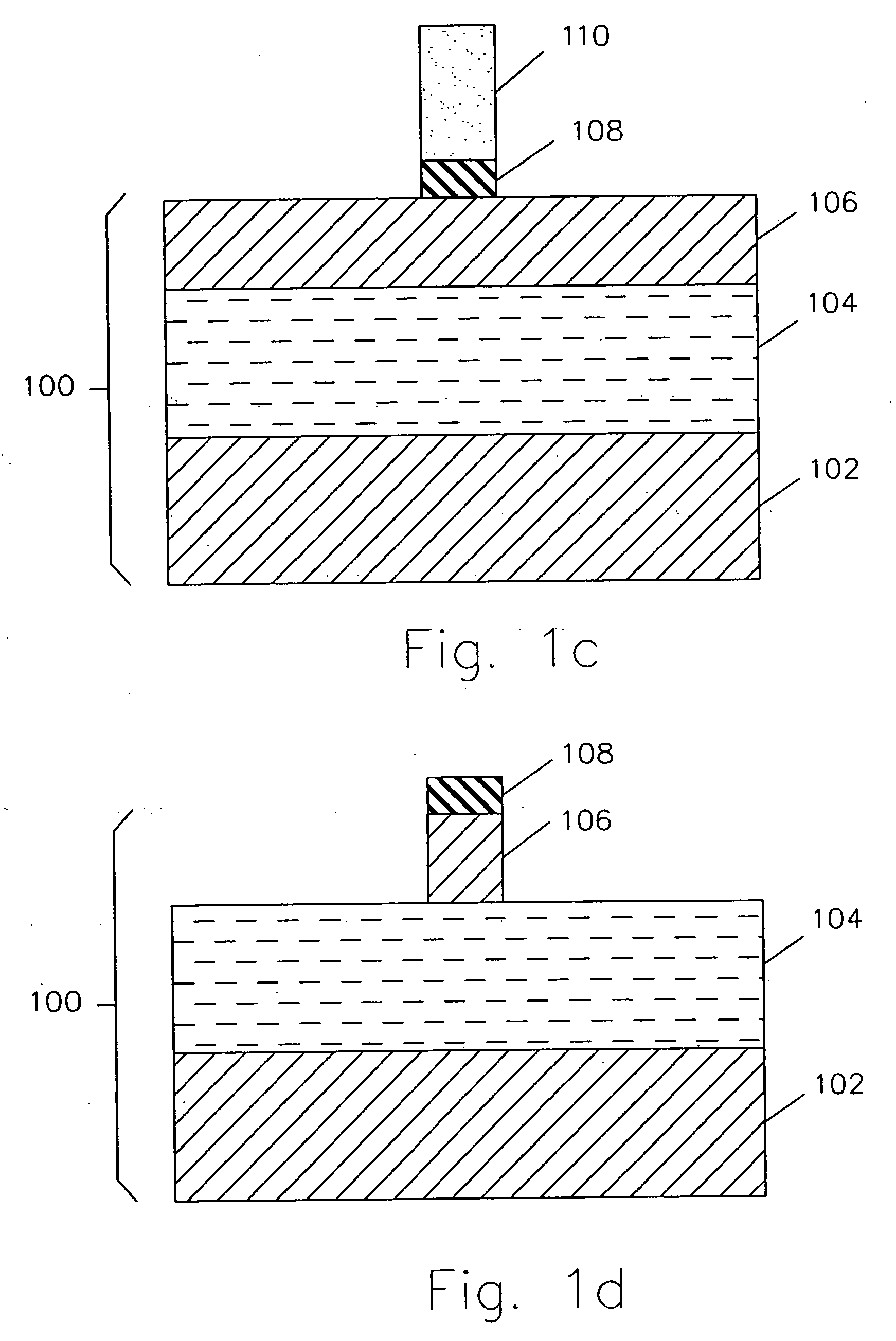

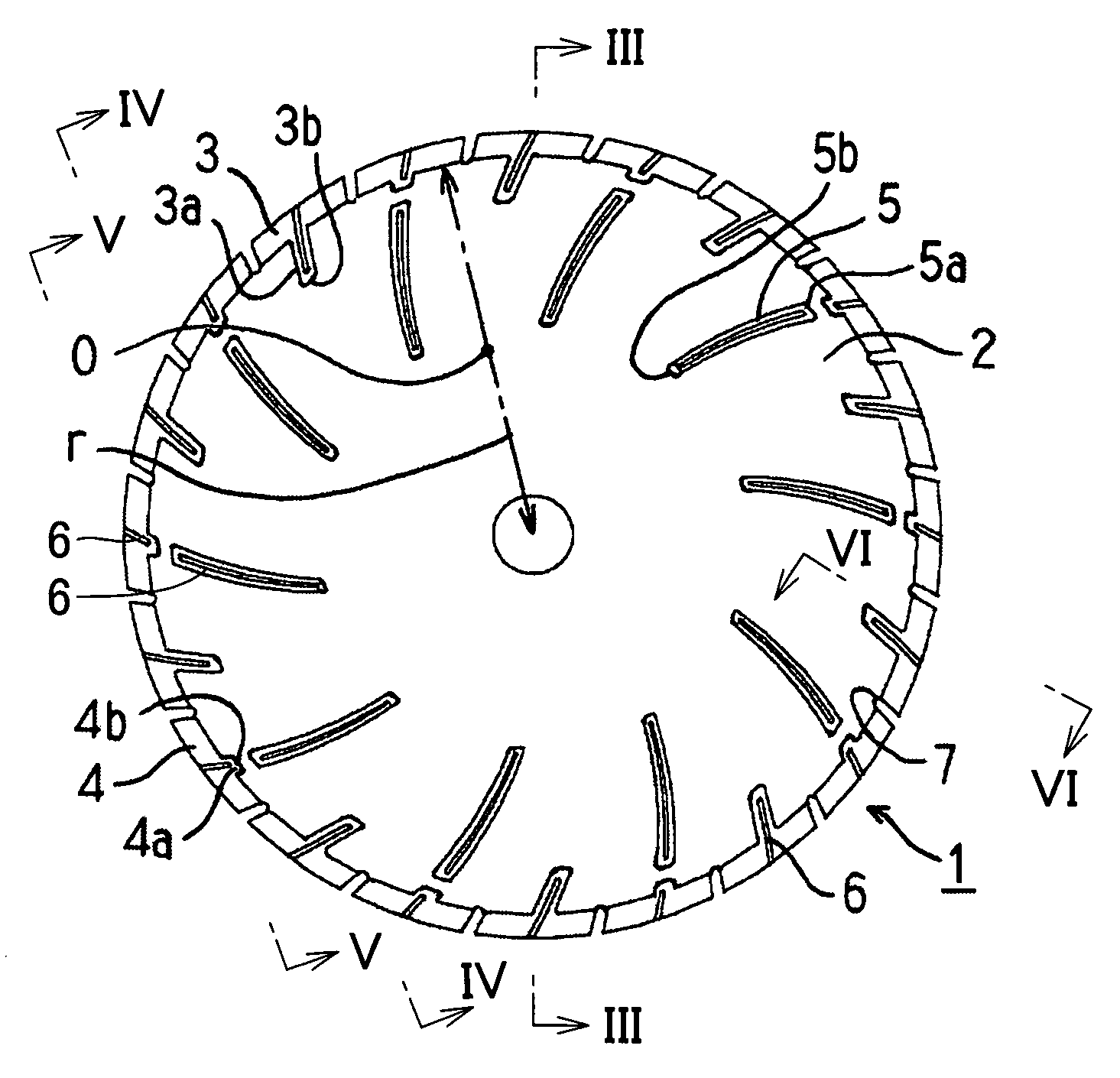

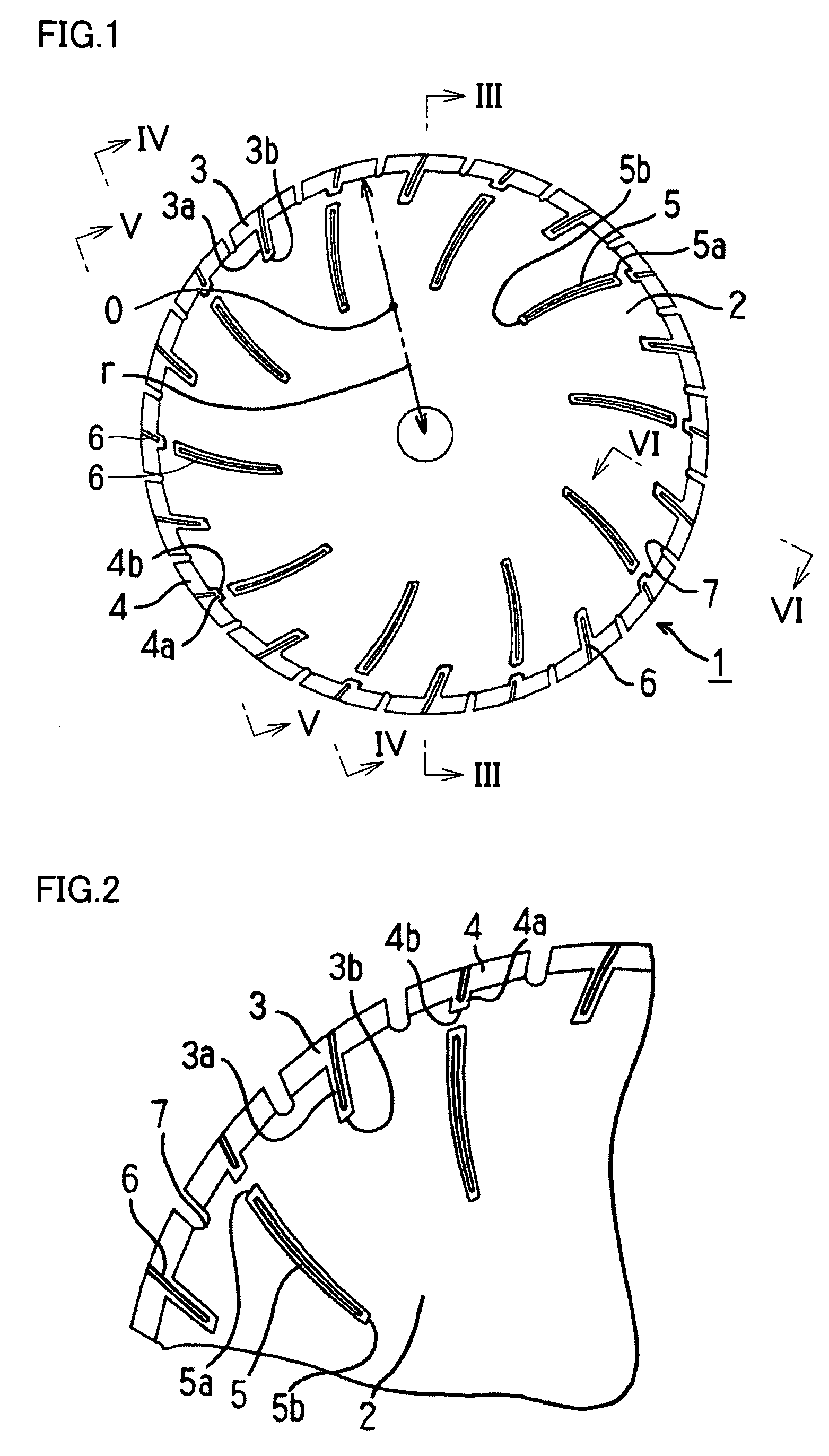

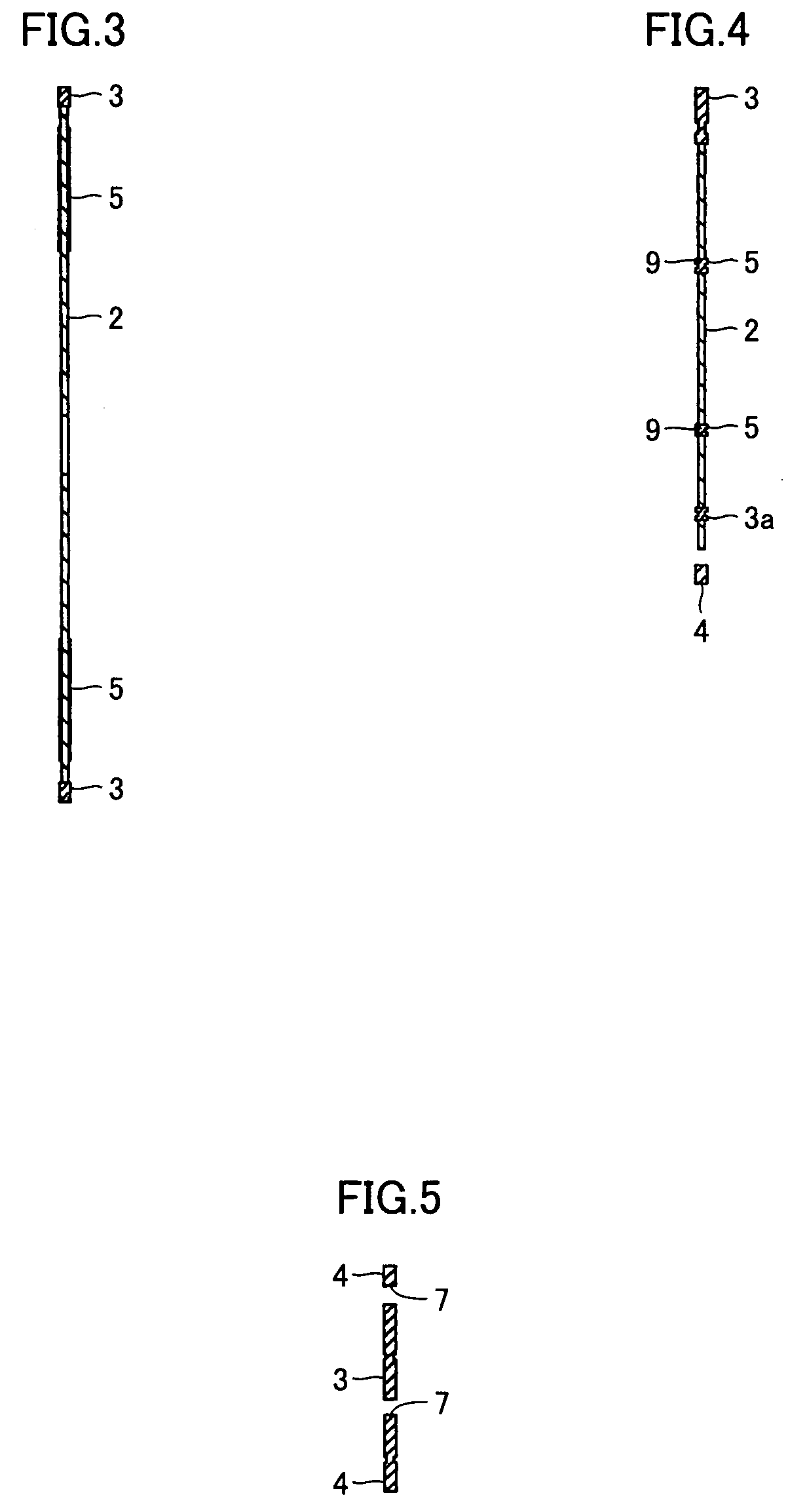

Diamond blade

InactiveUS20050121017A1Avoid undercutLittle wobbleRevolution surface grinding machinesMetal sawing toolsMechanical engineeringDiamond blade

In relation to a blade cutting stone or concrete, a blade, preventing wearing of a core while preventing the core from wobbling, cuttable at a stable speed is provided. In a blade formed by providing slots on the outer peripheral edge of a circular core and fixing a superabrasive layer to a portion of the outer peripheral surface of the core located between the slots, the superabrasive layer consists of a first superabrasive layer having an extension formed by partially extending the superabrasive layer toward the inner periphery of the core and a second superabrasive layer. A reinforcing superabrasive layer extending from the outer periphery toward the inner periphery of the core is formed on the inner peripheral side of the second superabrasive layer while the reinforcing superabrasive layer is located closer to the outer periphery than a radial central portion of the core, and an outer peripheral end of the reinforcing superabrasive layer is located closer to the outer periphery than an inner peripheral end of the extension of the first superabrasive layer. The second superabrasive layer can also be provided with an extension having a relatively short radial length with respect to the extension of the first superabrasive layer.

Owner:ALLIED MATERIAL

Organic anti-reflective coating composition and method for forming photoresist patterns using the same

InactiveUS6835532B2Excellent photoresist patternLow dispersionRadiation applicationsSemiconductor/solid-state device manufacturingAnti-reflective coatingLength wave

An organic anti-reflective coating composition and a method for forming photoresist patterns using the same are disclosed which can prevent reflection of the lower film layer or substrate and reduce standing waves caused by light and variation of in the thickness of the photoresist itself, thereby, increasing uniformity of the photoresist pattern, with respect to a microfine pattern-forming process using photoresists for a photolithography by using ArF with 193 nm wavelength among processes for manufacturing semiconductor device. More particularly, an organic anti-reflective coating composition and a method for forming photoresist patterns using the same are disclosed which can obtain perpendicular photoresist patterns and thus inhibit breakdown and / or collapse of the patterns by comprising an acid-diffusion inhibitor.

Owner:SK HYNIX INC

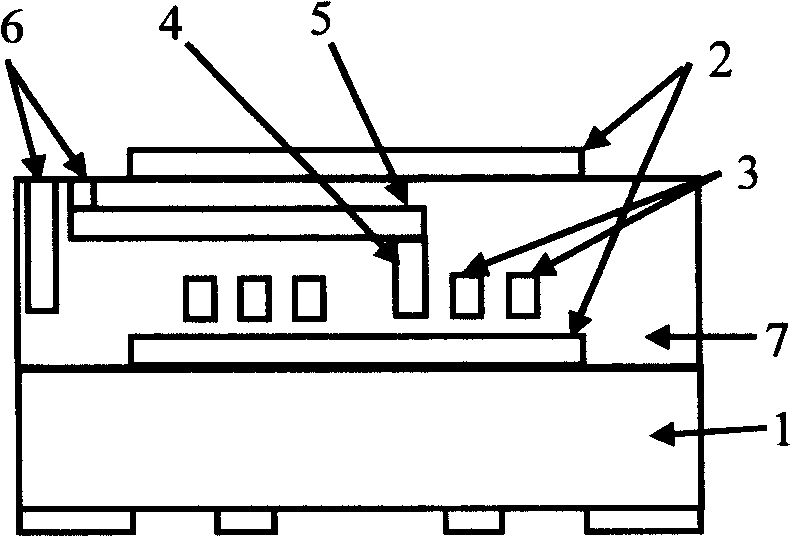

Method for manufacturing miniaturized fluxgate sensor

InactiveCN101481080AEase of mass productionGood repeatabilityTelevision system detailsSemi-permeable membranesResistElectrical conductor

The invention provides a method for producing a minimized fluxgate sensor in the micro electromechanical technical field, which comprises the following steps: producing a double-sized alignment symbol; sputtering a bottom layer; flinging positive photoresists, exposing and developing; plating a drive coil and a bottom layer coil of a receiving coil, connecting a conductor with a pin of the coil; removing photosensitive resist and a bottom layer; flinging polyimide, solidifying and polishing; sputtering the bottom layer; flinging positive photoresists, exposing and developing; plating a magnetic core, connecting the conductor with a pin; removing positive photoresists and the bottom layer; flinging polyimide, solidifying and polishing; sputtering the bottom layer; flinging the positive photoresists, exposing and developing; plating the drive coil and a top layer coil of the receiving coil and a pin; removing the photosensitive resist and the bottom layer; and magnetic annealing. The invention solves the problems of the traditional fluxgate sensor of poor stability, poor repetitiveness and poor mass production, ensures that the production technique is compatible with the large-scale integrated circuit technique, can be manufactured by integrating the interface circuit, and is widely applied in a plurality of new fields.

Owner:SHANGHAI JIAO TONG UNIV

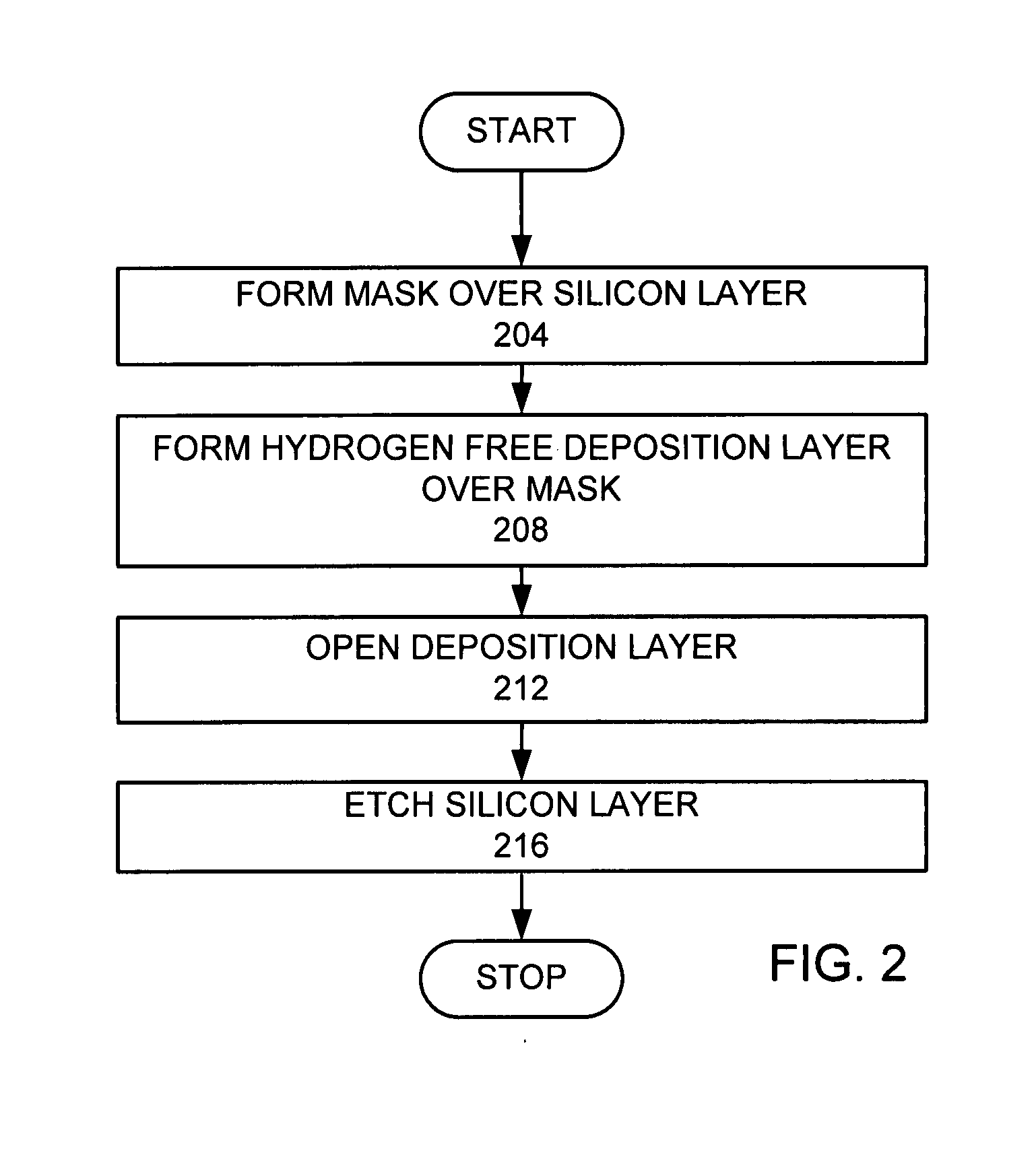

Minimization of mask undercut on deep silicon etch

ActiveUS20080308526A1Avoid undercutDecorative surface effectsSemiconductor/solid-state device manufacturingPolymer scienceHydrogen

A method for forming features in a silicon layer is provided. A mask is formed with a plurality of mask openings over the silicon layer. A polymer layer is deposited over the mask by flowing a hydrogen free deposition gas comprising C4F8, forming a plasma from the deposition gas, depositing a polymer from the plasma for at least 20 seconds, and stopping the depositing the polymer after the at least 20 seconds. The deposited polymer layer is opened by flowing an opening gas, forming a plasma from the opening gas which selectively removes the deposited polymer on bottoms of the plurality of mask openings with respect to deposited polymer on sides of the plurality of mask openings, and stopping the opening when at least some of the plurality of mask features are opened. The silicon layer is etched through the mask and deposited polymer layer.

Owner:LAM RES CORP

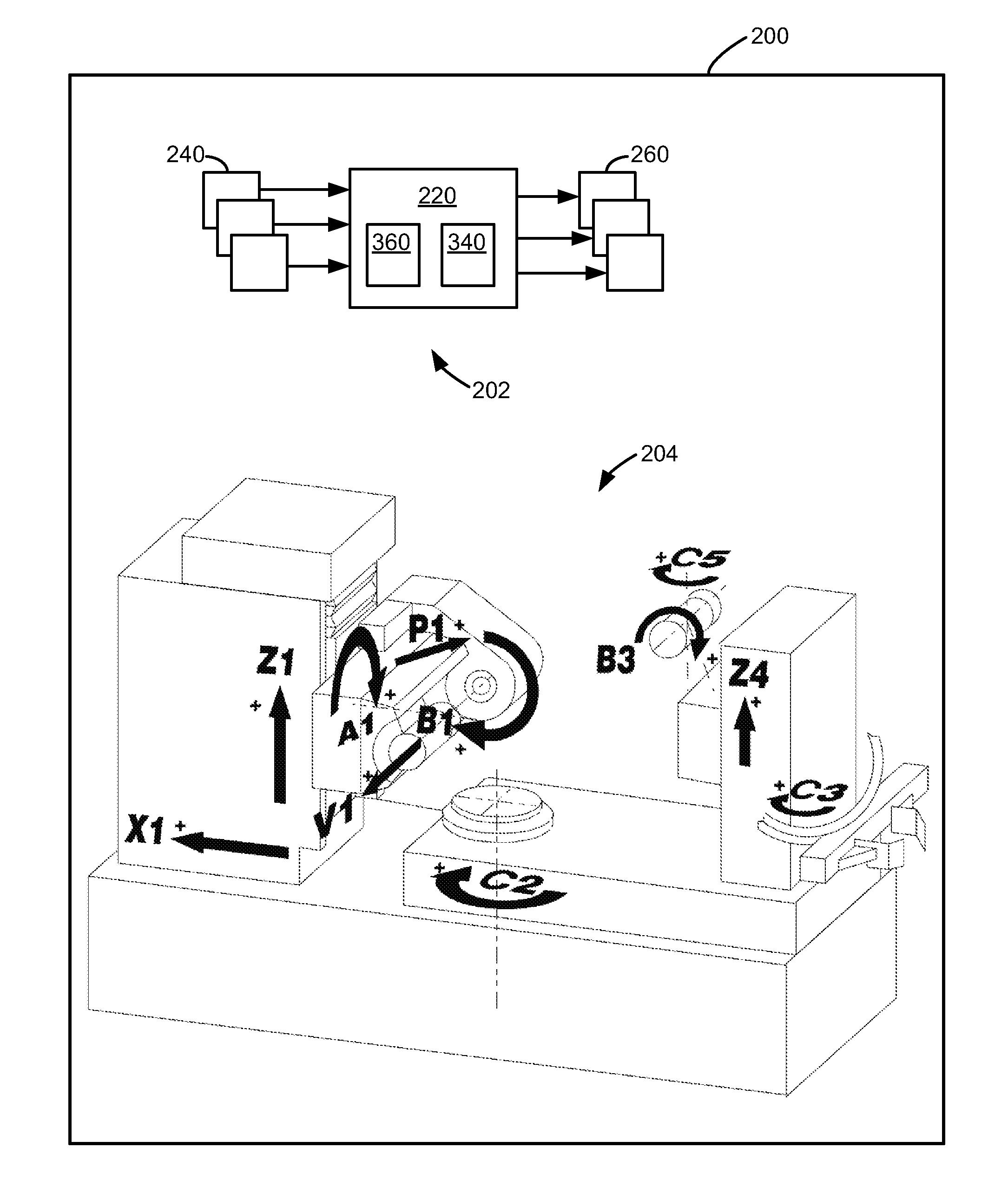

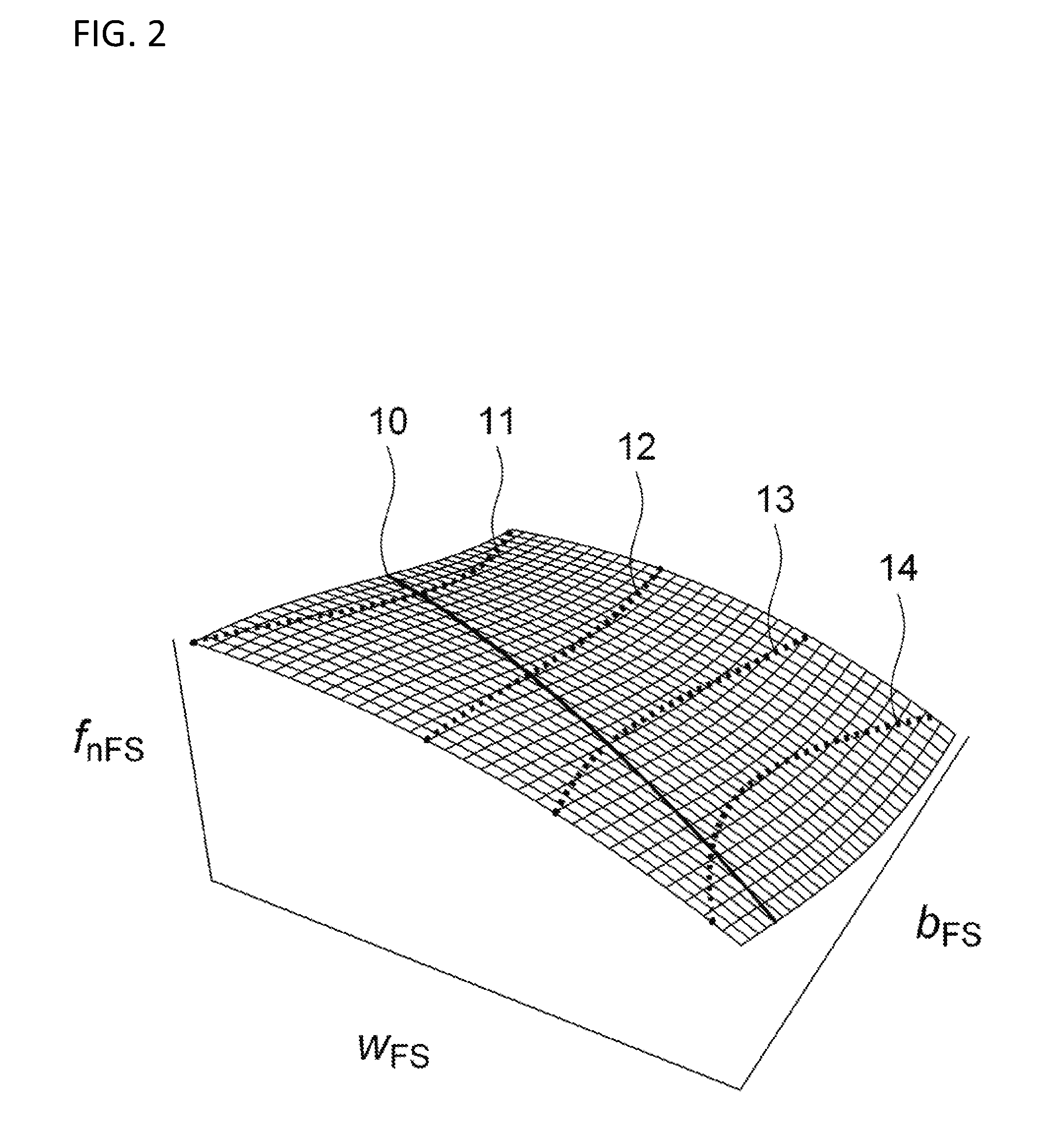

Grinding wheel normal tracing method during complex curve grinding process

InactiveCN1699020AImplement automatic normal trackingImplement normal trackingAutomatic grinding controlMathematical modelEngineering

This invention relates to an abrasive wheel normal tracing method in complex curve grind process, which is used in curve fine grinding field. The method comprises the following steps: a) adding a spinnig axis of bench sliding seat to the digital control shaft, which makes the work-piece outline alterable relative to the abrasive wheel axial cord; b) setting up mathematical model of normal tracing, computing the separation angle theta i between the outline normal line in grinding point and the radical admission shaft; c) making the bench sliding seat deflecting a certain angle with C axis, and making the abrasive wheel axial cord coincidence with the normal line of grinding point according to the theta i of each grinding point. The invention can remain the cutting status of abrasive wheel, and the abrasive wheel is forced evenly, which can avoid the interference from abrasive wheel and work-piece.

Owner:RAYMOND BEIJING VALVE MFG

Method of dressing a tool

ActiveUS20170008109A1Avoid undercutEasy to controlAbrasive surface conditioning devicesTotal factory controlEngineeringSurface geometry

A tool which can be used for gear manufacturing machining of a workpiece may be dressed on a dressing machine, and the dressing may take place with line contact between the dresser and the tool. A specific modification of the surface geometry of the tool is produced by the suitable selection of the position of the dresser with respect to the tool during dressing. The specific modification of the surface geometry of the workpiece is specifiable with regard to various parameters.

Owner:LIEBHERR VERZAHNTECHNIK GMBH

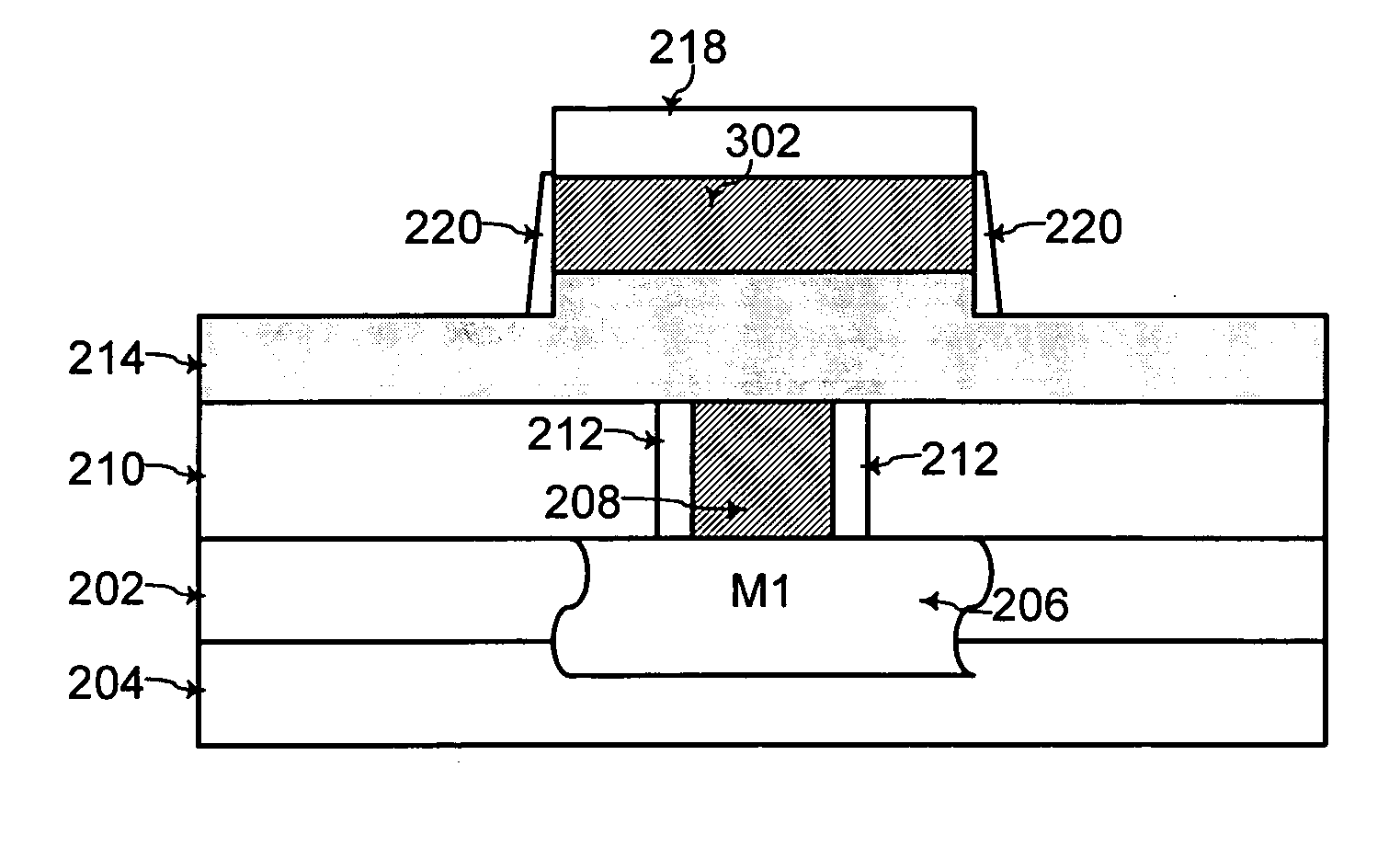

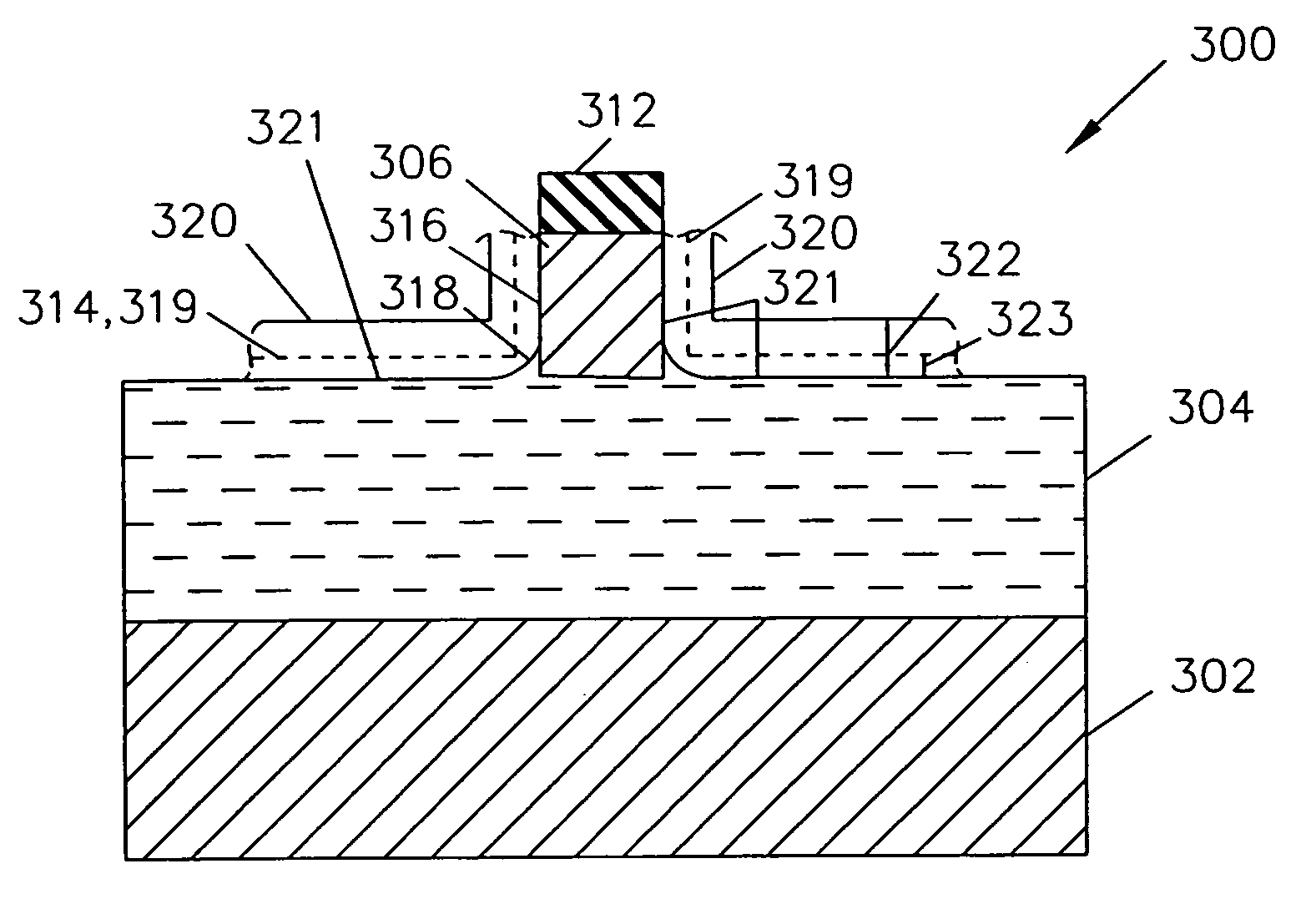

Phase change memory cell and method and system for forming the same

ActiveUS20080026586A1Easy to disassemblePrevent materialSemiconductor/solid-state device manufacturingDigital storagePhase-change memoryBromine

For fabricating a phase change memory cell, a layer of phase change material and a layer of a first electrode material are deposited. In addition, the first electrode material is patterned using an etchant including a low-reactivity halogen element such as bromine or iodine to form a first electrode. By using the low-reactivity halogen element, change to the composition of the phase change material and formation of undercut and deleterious halogen by-product are avoided.

Owner:SAMSUNG ELECTRONICS CO LTD

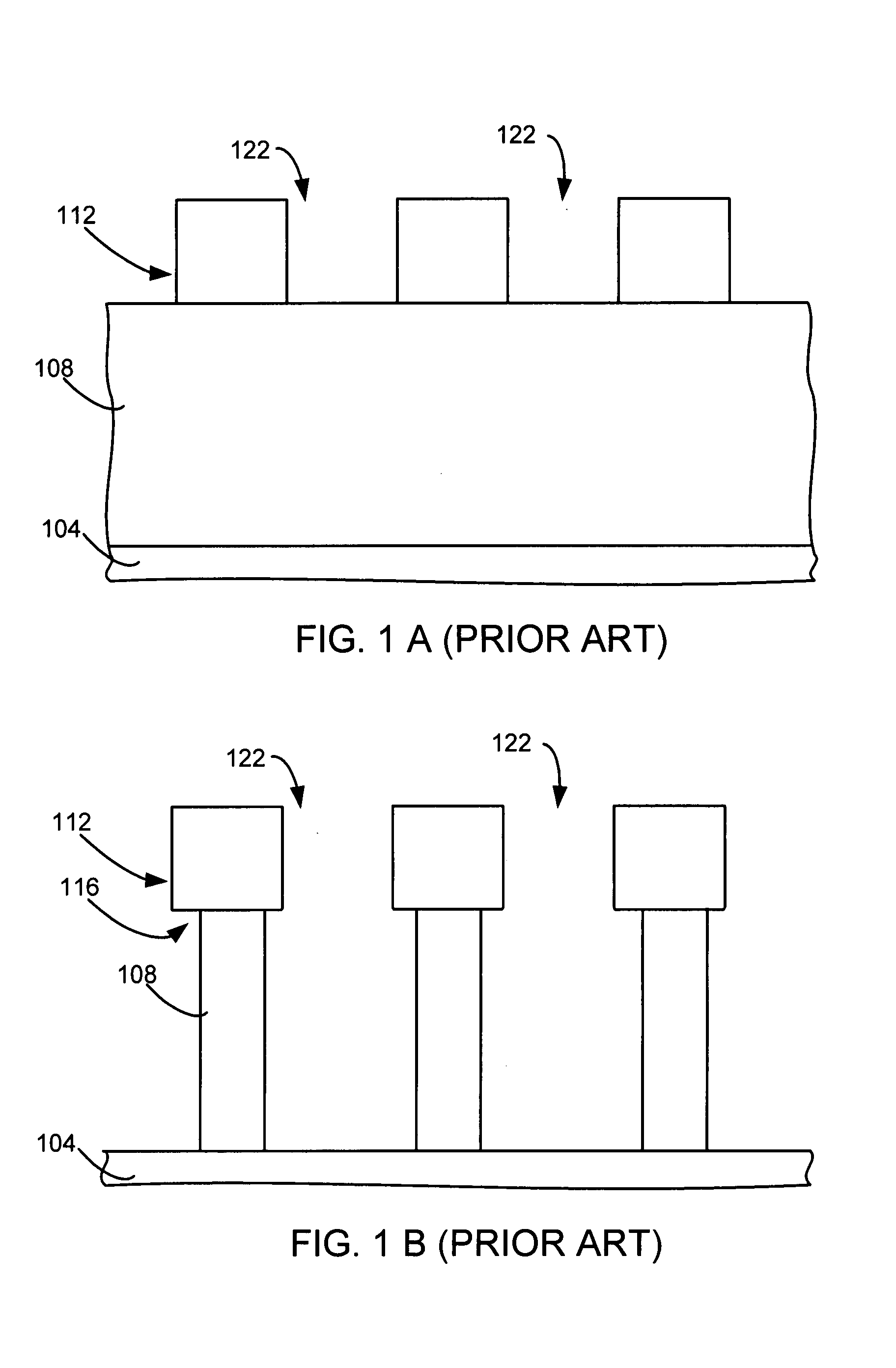

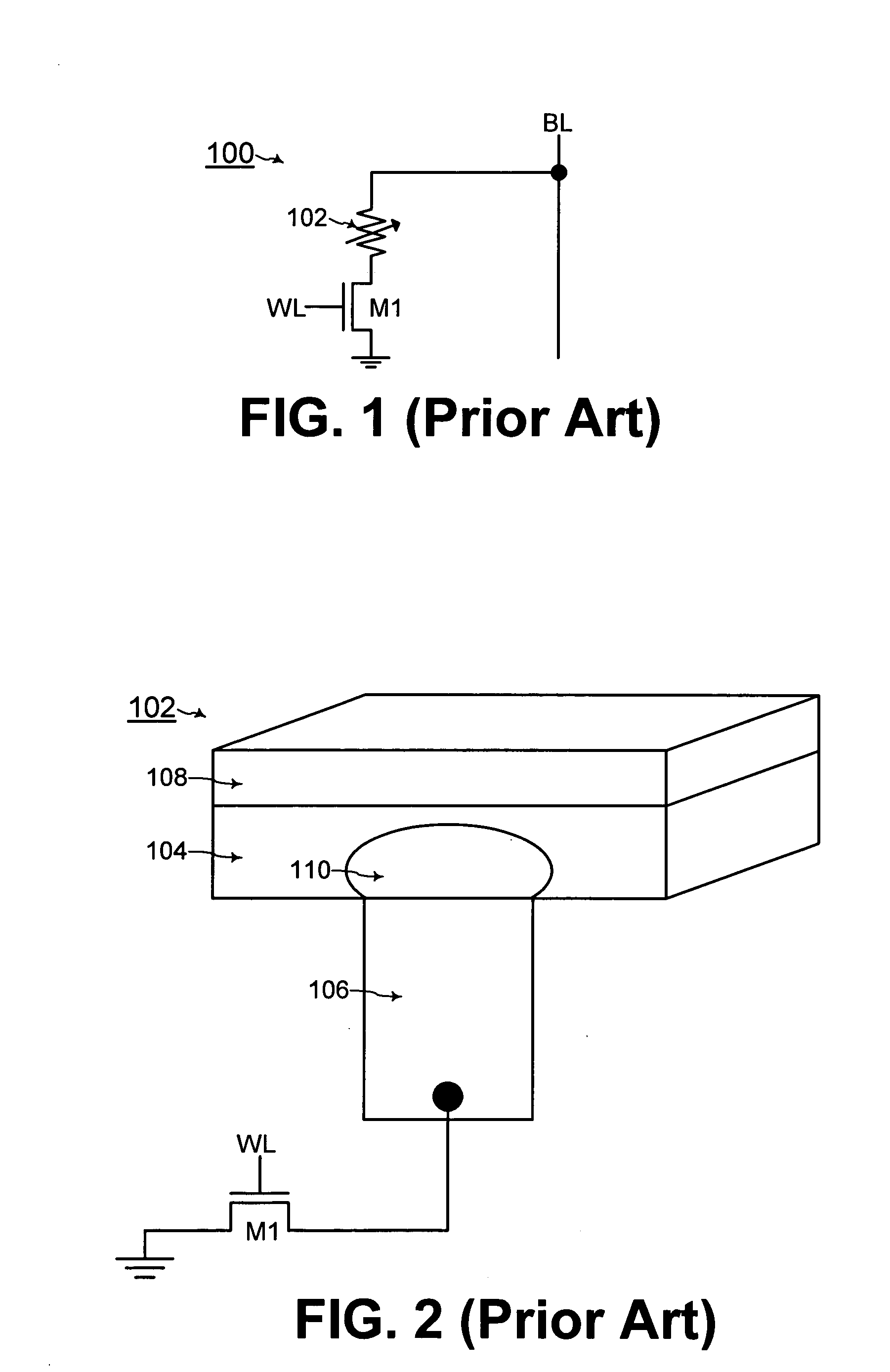

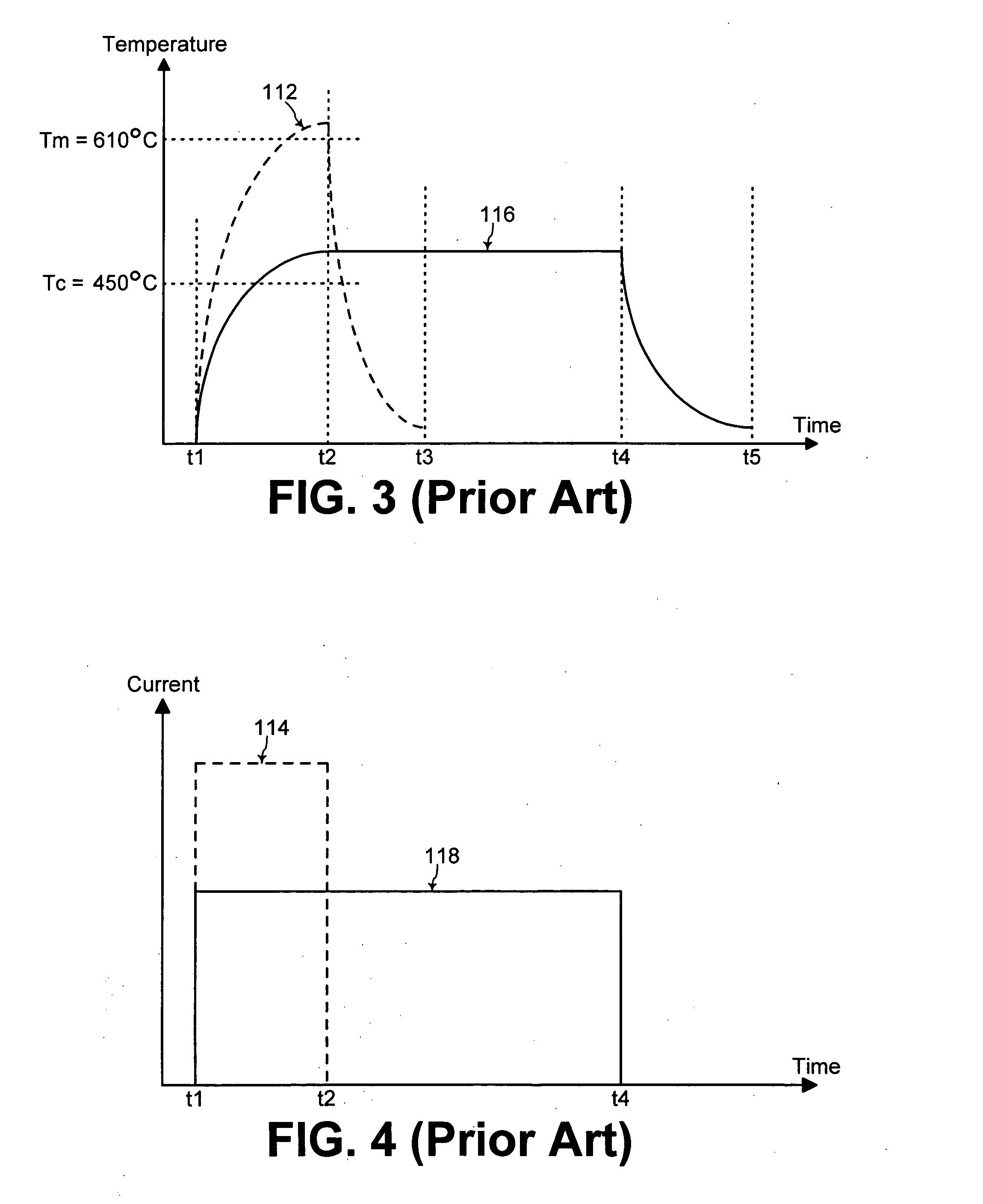

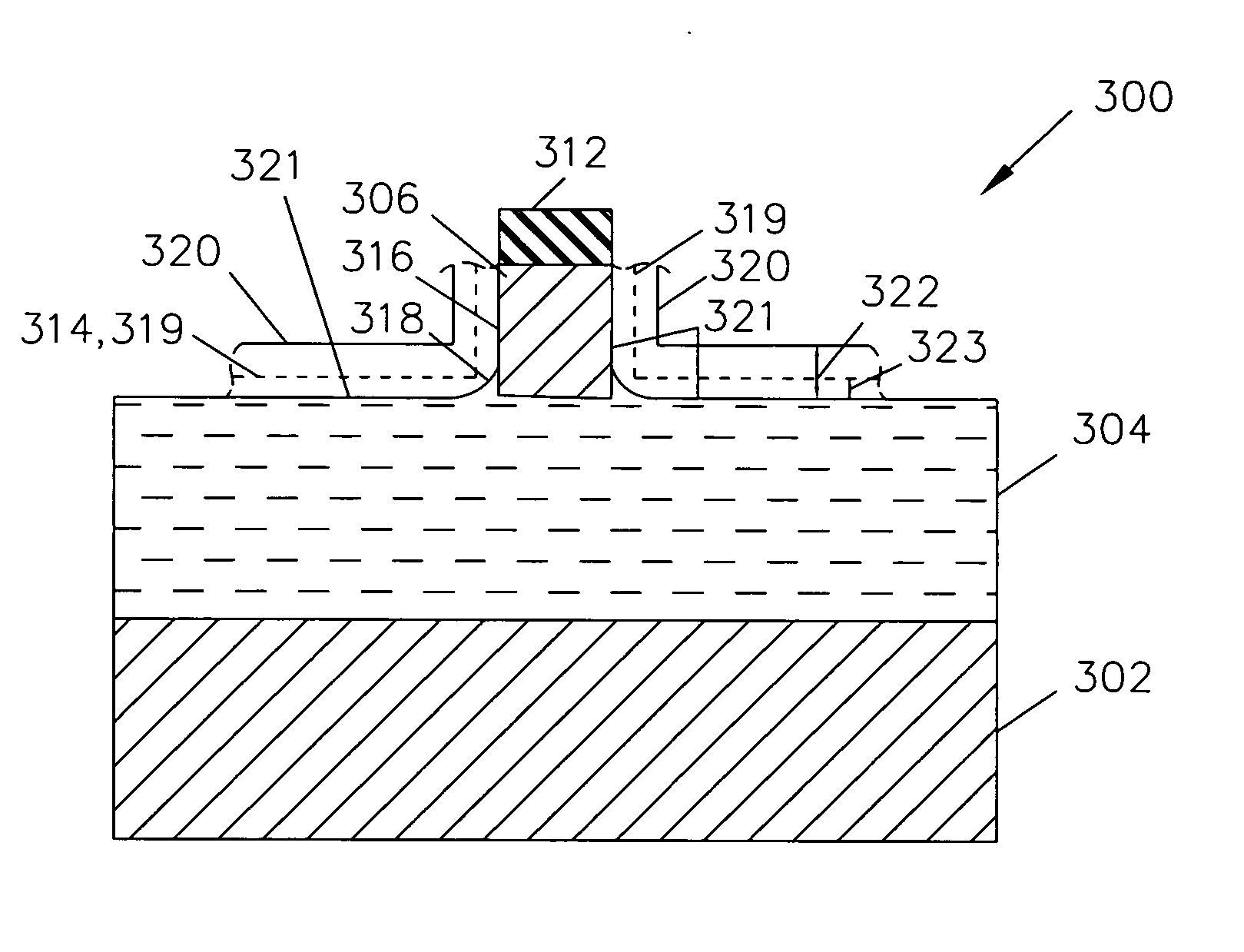

Structure and method to fabricate FinFET devices

InactiveUS7049662B2Minimizes and eliminates negative effectMinimize and eliminate negative effectTransistorSolid-state devicesSelf limitingEngineering

There is provided a method for fabricating a FinFET in which a self-limiting reaction is employed to produce a unique and useful structure that may be detectable with simple failure analysis techniques. The structure is an improved vertical fin with a gently sloping base portion that is sufficient to reduce or prevent the formation of an undercut area in the base of the vertical fin. The structure is formed via the self-limiting properties of the reaction so that the products of the reaction form both vertically on a surface of the vertical fin and horizontally on a surface of an insulating layer (e.g., buried oxide). The products preferentially accumulate faster at the base of the vertical fin where the products from both the horizontal and vertical surfaces overlap. This accumulation or build-up results from a volume expansion stemming from the reaction. The faster accumulation in the corner areas near the base, limits the reaction first in the base region, thereby etching less material and forming the remaining, un-etched material into the sloping dielectric base.

Owner:GLOBALFOUNDRIES INC

Method and relevant device for achieving metal mutual connection through preparation of micro-protruding-points with superfine spaces

ActiveCN103258791AMetal end heightAvoid undercutSemiconductor/solid-state device detailsSolid-state devicesNanometer sizeAnti oxidative

The invention discloses a method for achieving metal mutual connection through preparation of micro-protruding-points with superfine spaces and a relevant device for achieving the metal mutual connection through the preparation of the micro-protruding-points with the superfine spaces. The method includes the steps: first depositing silicon carbide to etch a stop layer and an electrolyte layer, gluing, conducting etching on the electrolyte layer to form a hole in a dying mode, depositing a metal seed layer, filling metal, utilizing CMP to clear metal on a face, conducting etching on the electrolyte layer, forming a metal exposed head structure and plating anti-oxidative or low-melting-point metal, and then conducting bonding. The method avoids protruding point drilling etch, the spaces of the protruding points can be reduced into a plurality of micron sizes and even into a plurality of nanometer sizes which are far smaller than the sizes of the spaces of existing protruding points. Due to fact that a metal end face is higher than the electrolyte layer, the phenomenon of depressions in the surface of metal caused by the CMP can be overcome, during bonding, complete contacting between upper metal and lower metal can be guaranteed through plastic deformation, and requirements to evenness are lowered after wafers undergo the CMP. Bonding can be completed under low temperature through a general hot-pressing method. The relevant device has the advantages of being low in cost.

Owner:NAT CENT FOR ADVANCED PACKAGING

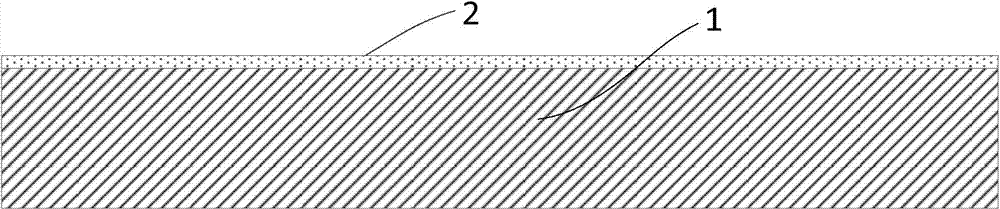

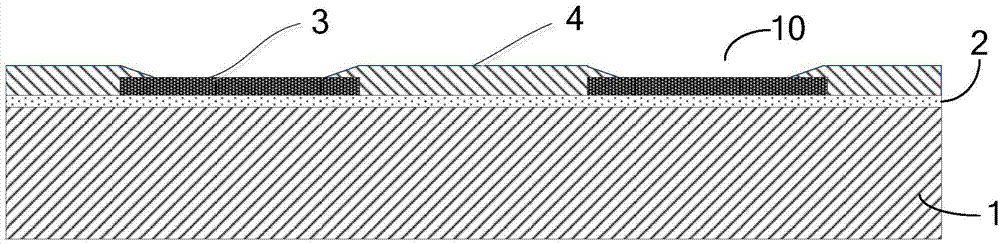

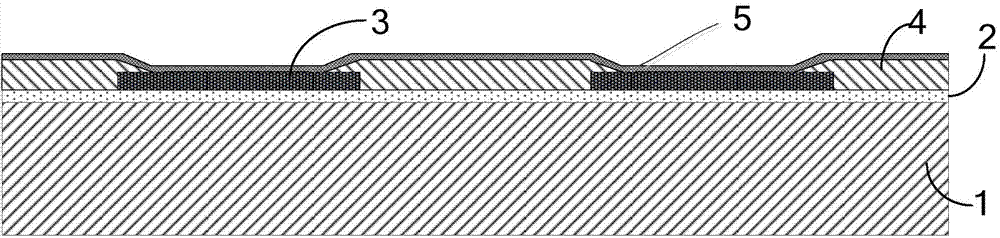

Array substrate for display device

InactiveCN1901208AAvoid undercutEliminate etchTransistorSemiconductor/solid-state device detailsElectrical resistance and conductanceInsulation layer

A substrate for an LCD display device exhibiting improved display quality through lower contact resistance and elimination of undercutting. The display switches have three electrodes, at least one of which has three metal layers, the third of which is formed by nitrating the second metal layer. The pixel electrode is electrically connected to the second metal layer through a contact hole formed through an insulation layer and the second metal layer of the switching device.

Owner:SAMSUNG DISPLAY CO LTD

Method for manufacturing display device and etching solution composition

ActiveCN103000509AAvoid undercutImprove productivitySemiconductor/solid-state device manufacturingNon-linear opticsProduction rateDisplay device

The invention discloses a method for manufacturing a display device and an etching solution composition which is used for the method. The etching solution composition for a copper metal layer / metal oxide layer is used to simultaneously etch a data metal layer containing the copper metal layer and an oxide semiconductor layer containing the metal oxide layer. Patterns of the data metal layer and the oxide semiconductor layer are formed in order by the etching solution composition, so as to facilitate formation of semiconductor patterns and source patterns comprising a data line, a source electrode and a drain electrode. In this way, the composition of the invention is effectively suitable for the method for manufacturing a display device, and guarantees the improvement of the production rate of thin film transistors and display devices and the reliability of the process of manufacturing the thin film transistors and the display devices.

Owner:DONGWOO FINE CHEM CO LTD

Method and device for performing electric magnetization arc welding-braze welding compounding on dissimilar materials

InactiveCN101844259AImprove connection qualityInhibition formationSoldering apparatusMetal working apparatusMetallic materialsMagnetization

The invention discloses a method and a device for performing electric magnetization resistance welding-braze welding compounding on dissimilar materials. In the process of performing arc welding-braze welding on the dissimilar metal material, a brazed liquid solder molten pool is subjected to the reinforced booster action of electromagnetic stirring and electric magnetization by using the characteristic that a magnet exciting coil generates an external applied alternating magnetic field in a welding area to control a welding arc so as to promote ordered flow of the liquid solder, and rupture of membranes, wetting, spreading and diffusion of the liquid solder on the surface of the metal material with a higher melting point, promote the liquid solder and a base metal which is molten by the metal material with a lower melting point to be mixed fully, improve uniformity of compositions of a soldered seam, reduce the weld defects, optimize the compositions and the performance of the soldered seam, and improve the soldered joint; and the device has the advantages of simple structure, flexible application, lower cost, good effect, and easy implementation.

Owner:CHONGQING UNIV

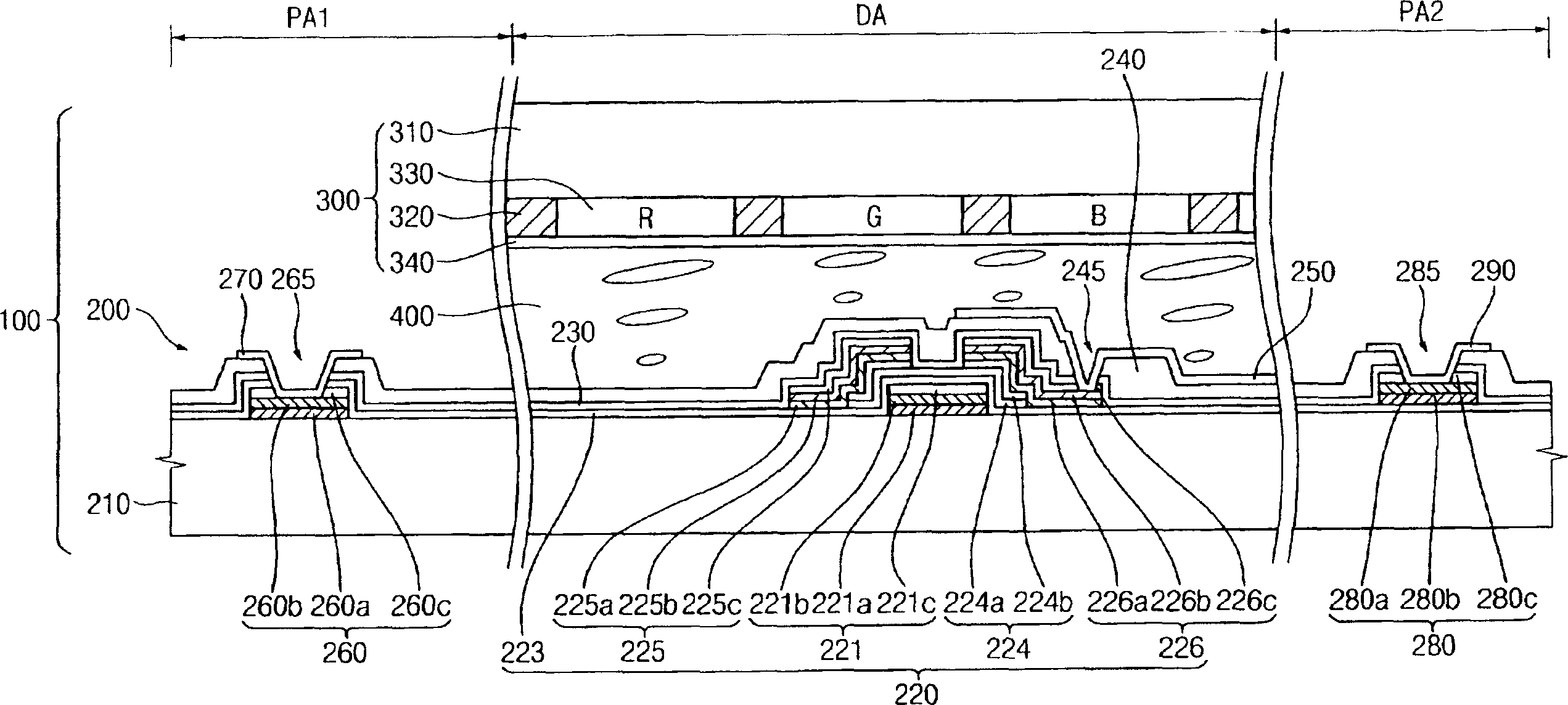

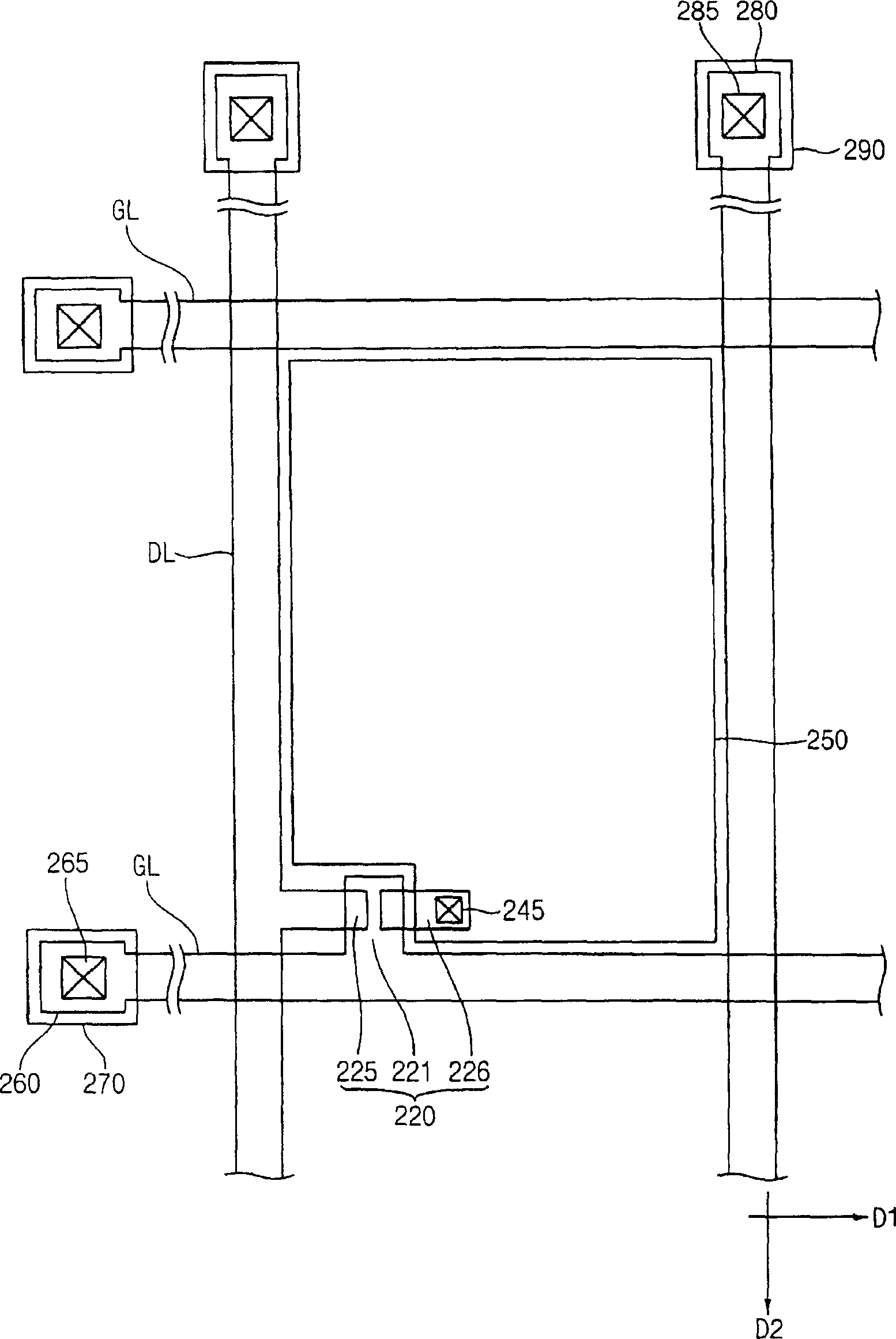

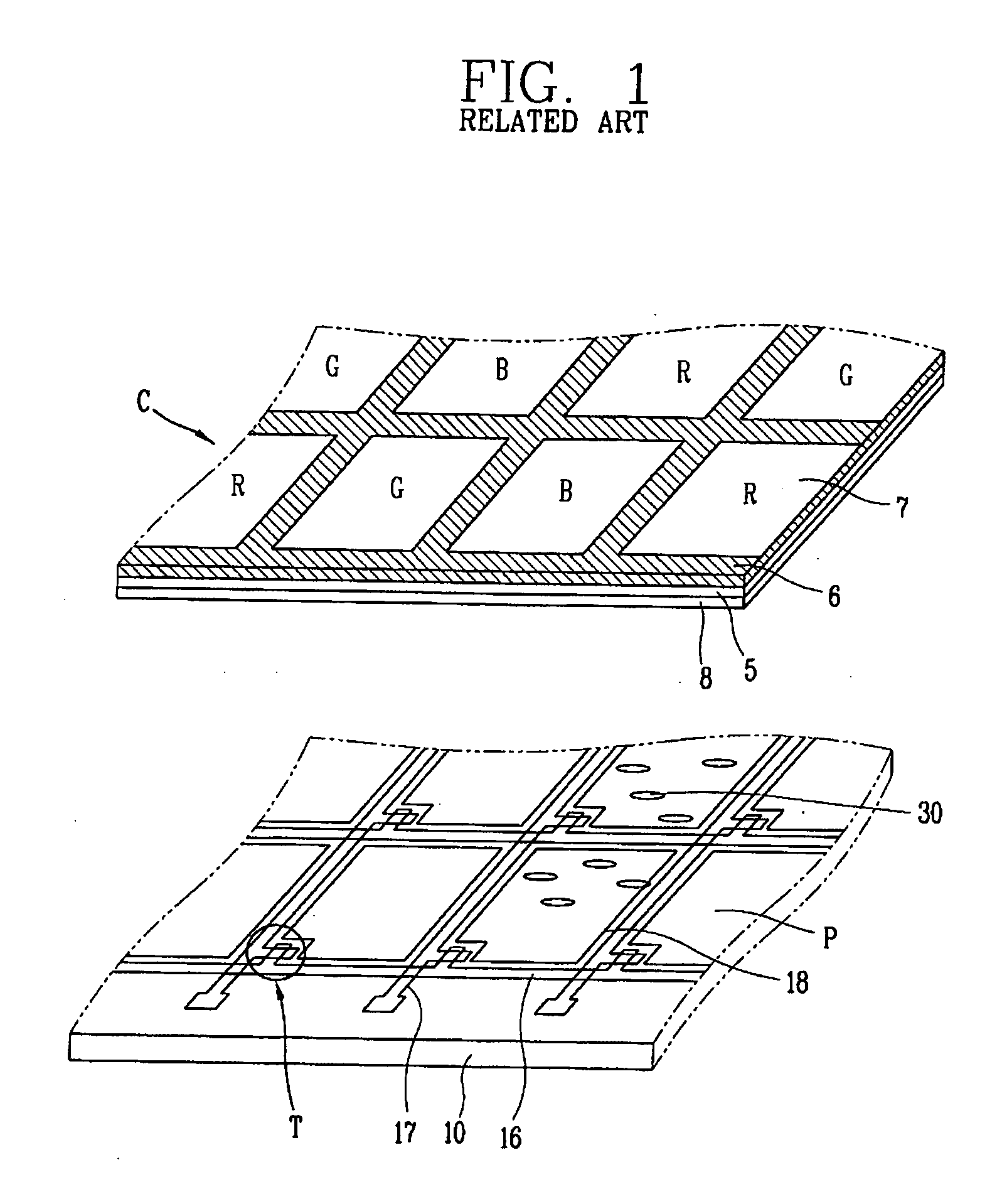

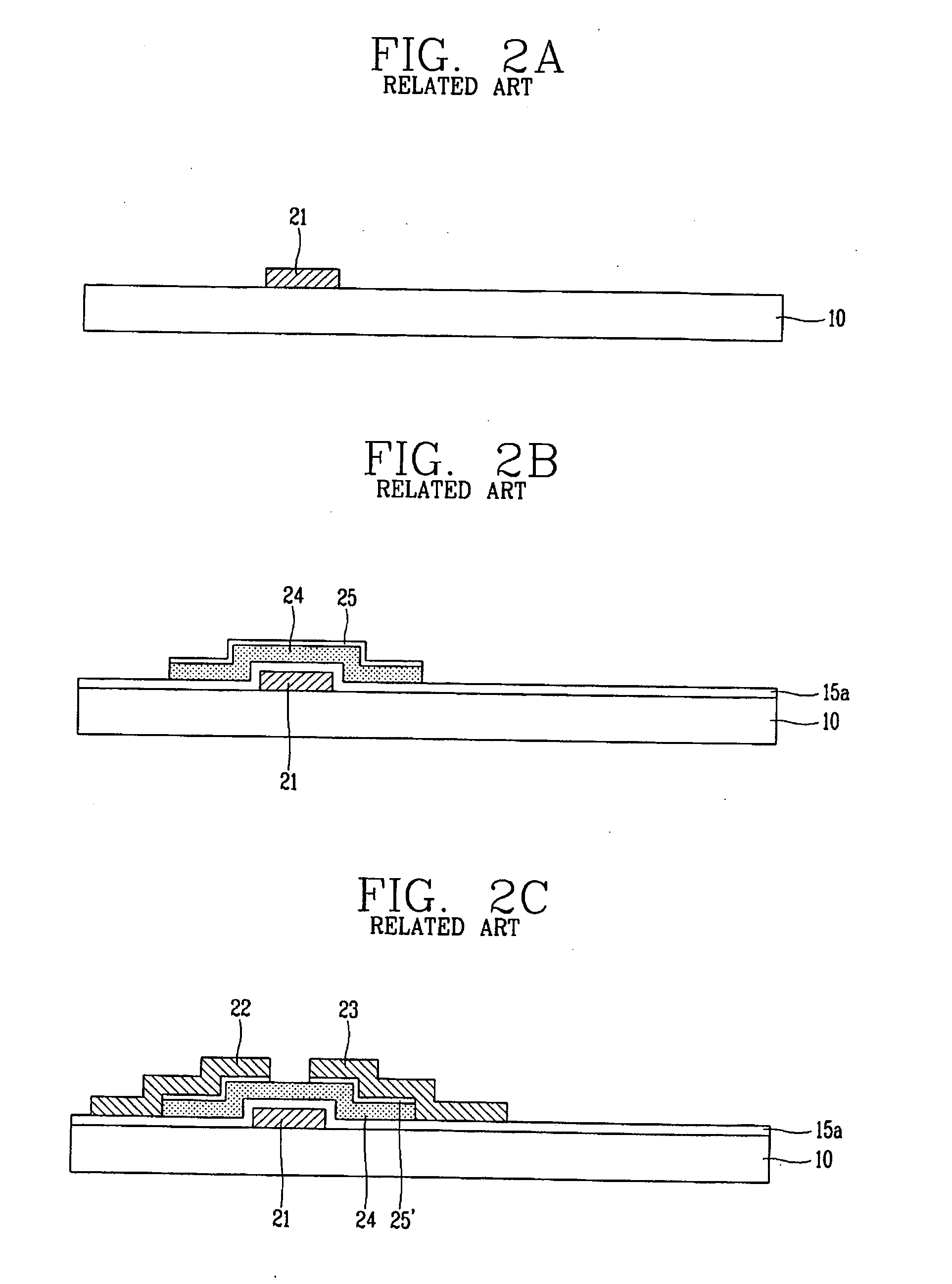

Liquid crystal display device and fabrication method thereof

ActiveUS20080174711A1High picture qualityHigh luminanceSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

A liquid crystal display (LCD) device includes: a first substrate divided into a pixel part and first and second pad parts; a gate electrode and a gate line formed at the pixel part of the first substrate; an active pattern as an island formed over the gate electrode with a first insulation film interposed therebetween, and having a width smaller than the gate electrode; an ohmic-contact layer formed on source and drain regions of the active pattern on the first substrate; source and drain electrodes formed as islands over the gate electrode of the first substrate and electrically connected with the source and drain regions of the active pattern via the ohmic-contact layer; a data line formed on the pixel part of the first substrate and crossing the gate line to define a pixel region; a pixel electrode formed at the pixel region and electrically connected with the drain electrode; a second insulation film formed on the first substrate; and a second substrate attached to the first substrate in a facing manner.

Owner:LG DISPLAY CO LTD

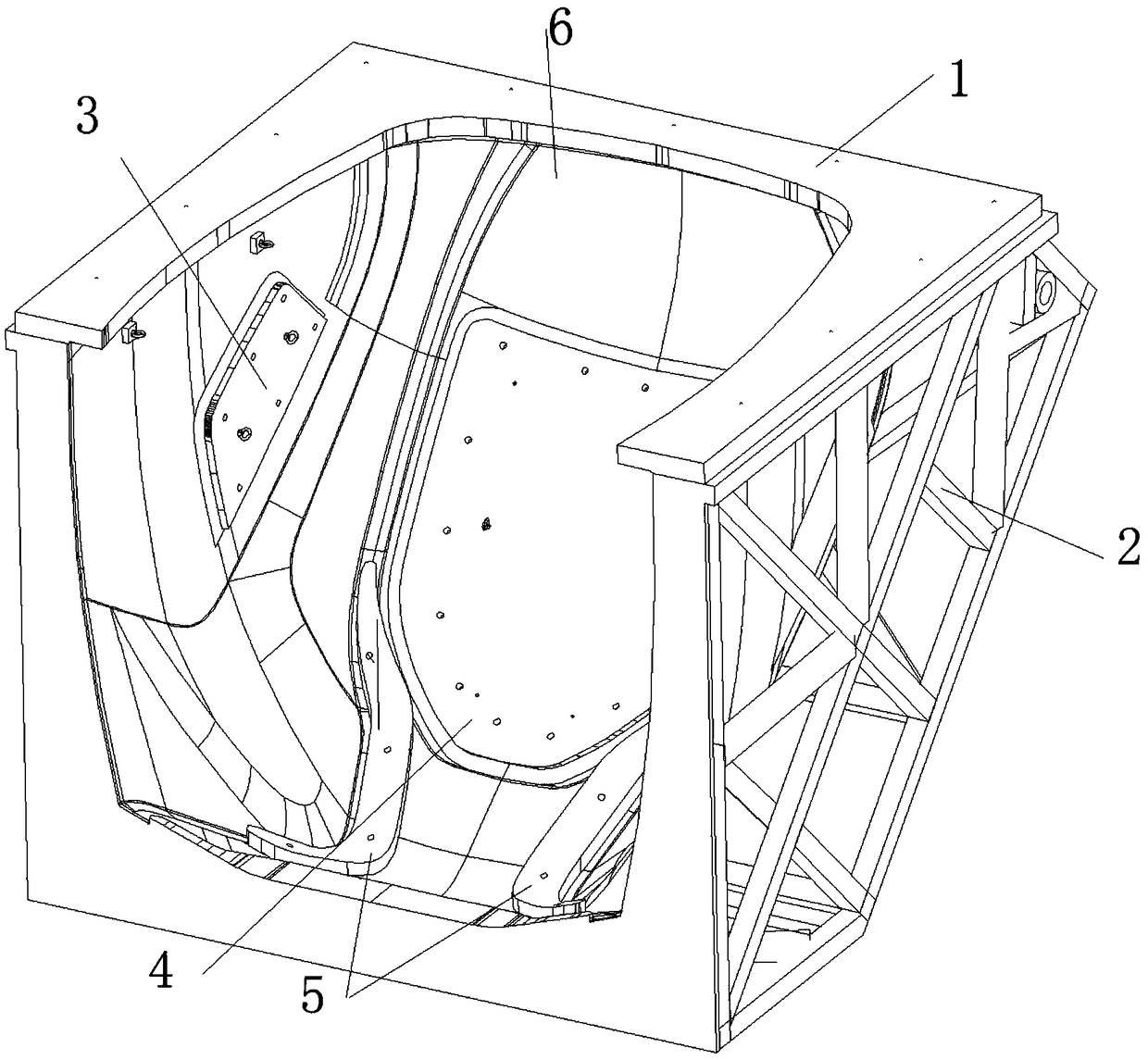

Integral-molded large mold with complicated structure

PendingCN108656410ASmall coefficient of thermal expansionImprove thermal conductivityFiberGlass fiber

The invention relates to an integral-molded large mold with a complicated structure. The large mold comprises a mold body and a mold frame; an upper cover plate is fixed at the upper part of the moldbody; two side inserts are embedded in the two sides of the mold body; a bottom insert is embedded in the bottom of the mold body; a front end insert is embedded in the front end of the mold body; theupper cover plate, the two side inserts, the bottom insert and the front end insert are detachably embedded in the mold body; the mold frame is positioned on the outer side of the mold body; the moldframe and the mold body are bonded through resins, and are reinforced by glass fiber cloth or felt hand paste; the mold body adopts a carbon fiber and glass fiber mixed composite material; and the carbon fiber composite material has the characteristics of low thermal expansion coefficient and excellent heat conductivity. Compared with a metal mold, the weight of the mold with the composite material is greatly reduced; as the product is integrally molded, a lot of operating time is saved, and the appearance flatness and the assembly precision of the product are guaranteed; and through detachable design of the inserts, the reverse buckling of the product is prevented, and the product can be quickly demolded.

Owner:上海晋飞碳纤科技股份有限公司

Structure and method to fabricate finfet devices

InactiveUS20060043502A1Minimizes and eliminates negative effectMinimize and eliminate negative effectTransistorSolid-state devicesSelf limitingEngineering

There is provided a method for fabricating a FinFET in which a self-limiting reaction is employed to produce a unique and useful structure that may be detectable with simple failure analysis techniques. The structure is an improved vertical fin with a gently sloping base portion that is sufficient to reduce or prevent the formation of an undercut area in the base of the vertical fin. The structure is formed via the self-limiting properties of the reaction so that the products of the reaction form both vertically on a surface of the vertical fin and horizontally on a surface of an insulating layer (e.g., buried oxide). The products preferentially accumulate faster at the base of the vertical fin where the products from both the horizontal and vertical surfaces overlap. This accumulation or build-up results from a volume expansion stemming from the reaction. The faster accumulation in the corner areas near the base, limits the reaction first in the base region, thereby etching less material and forming the remaining, un-etched material into the sloping dielectric base.

Owner:GLOBALFOUNDRIES INC

Diamond blade

InactiveUS7100595B2Avoid undercutLittle wobbleRevolution surface grinding machinesMetal sawing toolsEngineeringMechanical engineering

In relation to a blade cutting stone or concrete, a blade, preventing wearing of a core while preventing the core from wobbling, cuttable at a stable speed is provided. In a blade formed by providing slots on the outer peripheral edge of a circular core and fixing a superabrasive layer to a portion of the outer peripheral surface of the core located between the slots, the superabrasive layer consists of a first superabrasive layer having an extension formed by partially extending the superabrasive layer toward the inner periphery of the core and a second superabrasive layer. A reinforcing superabrasive layer extending from the outer periphery toward the inner periphery of the core is formed on the inner peripheral side of the second superabrasive layer while the reinforcing superabrasive layer is located closer to the outer periphery than a radial central portion of the core, and an outer peripheral end of the reinforcing superabrasive layer is located closer to the outer periphery than an inner peripheral end of the extension of the first superabrasive layer. The second superabrasive layer can also be provided with an extension having a relatively short radial length with respect to the extension of the first superabrasive layer.

Owner:ALLIED MATERIAL

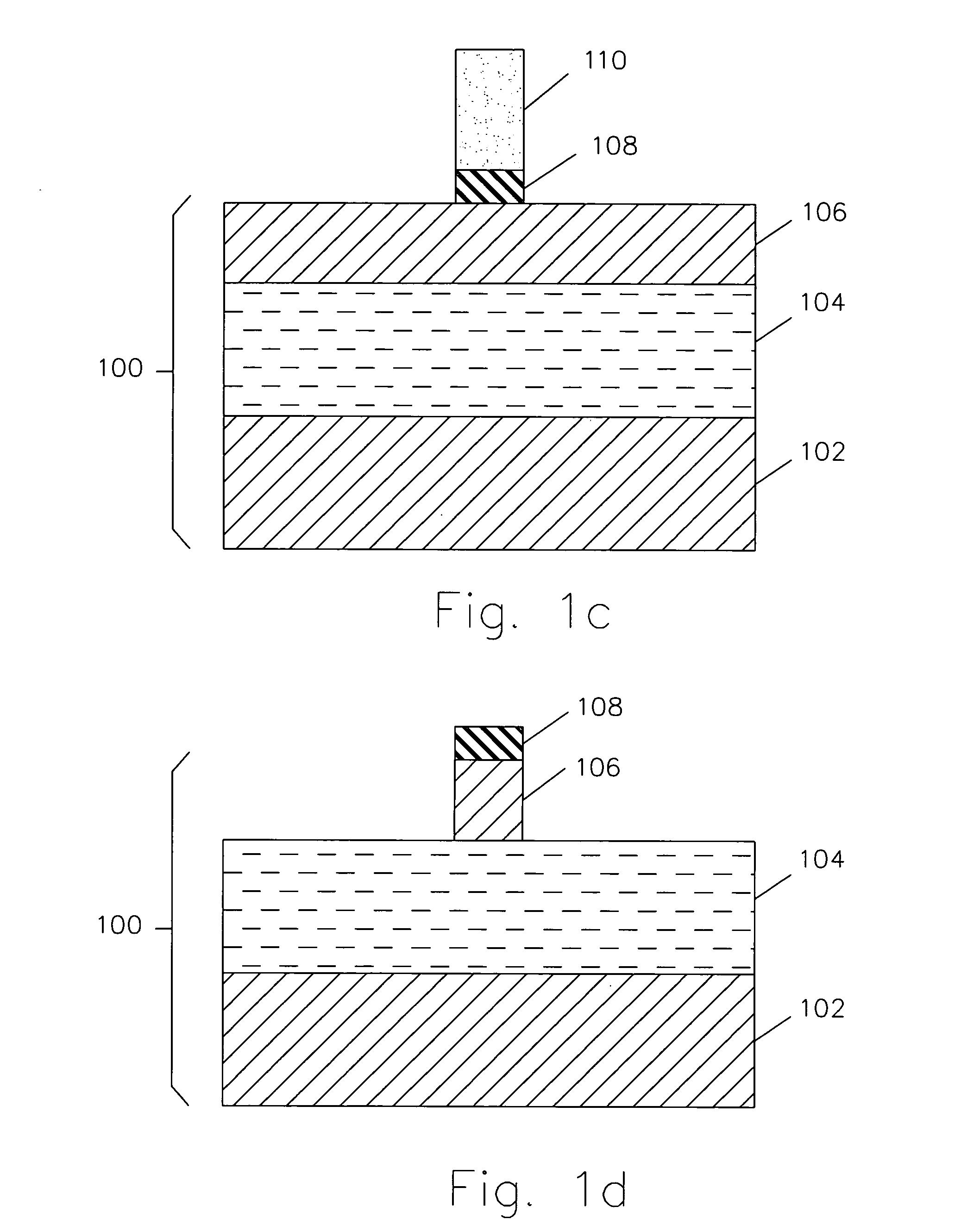

Salient point structure for preventing salient point lateral etching and forming method

ActiveCN103887276AAvoid the problem of undercuttingAvoid undercutSemiconductor/solid-state device detailsSolid-state devicesEtchingSemiconductor structure

The invention relates to a semiconductor structure and manufacturing method thereof, in particular to a salient point structure for preventing salient point lateral etching and a forming method and belongs to the technical field of semiconductor manufacturing. In the technical scheme, the salient point structure for preventing the salient point lateral etching comprises a substrate and an insulating layer located on the substrate. A metal bonding pad is arranged on the insulating layer, an outer ring of the metal bonding pad is provided with a dielectric layer, the dielectric layer covers the insulating layer and the edge of the outer ring of the metal bonding pad. A copper column is arranged right above the metal bonding pad, the bottom end of the copper column sequentially passes through a seed layer and an adhesion layer to be in contact with and electrically connected with the metal bonding pad and is supported on the dielectric layer through the seed layer and the adhesion layer, and welding flux salient points are arranged at the top end of the copper column. The salient point structure for preventing the salient point lateral etching adopts a method for firstly imaging the adhesion layer, the problem that the lateral etching is easily caused during adhesion layer removal after electroplating is solved, and the reliability and yield of machined and manufactured salient points are improved.

Owner:NAT CENT FOR ADVANCED PACKAGING

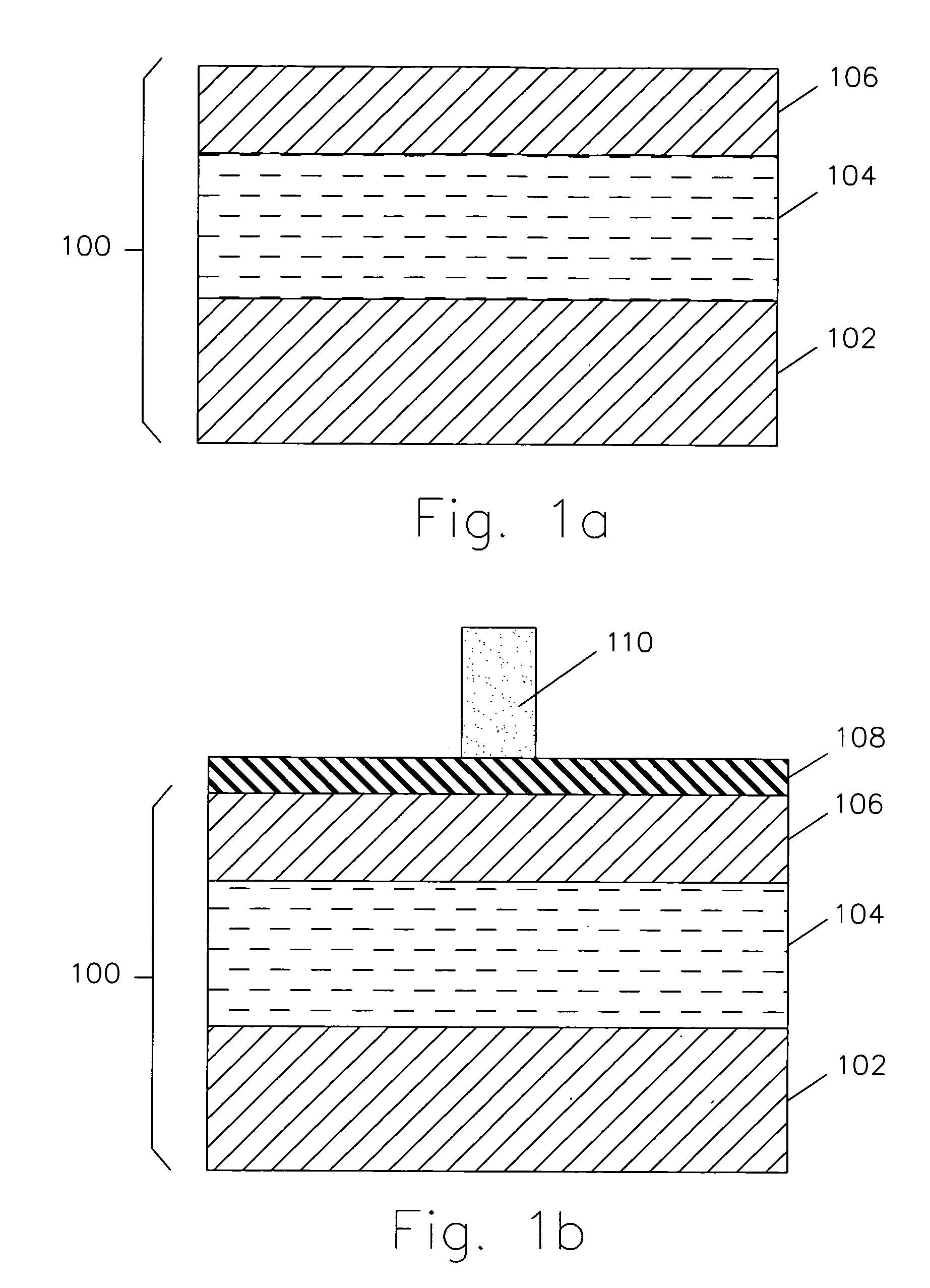

Structure and method to fabricate finfet devices

InactiveUS20050110087A1Eliminate effectPrevent undercutTransistorSolid-state devicesBuried oxideSelf limiting

There is provided a method for fabricating a FinFET in which a self-limiting reaction is employed to produce a unique and useful structure that may be detectable with simple failure analysis techniques. The structure is an improved vertical fin with a gently sloping base portion that is sufficient to reduce or prevent the formation of an undercut area in the base of the vertical fin. The structure is formed via the self-limiting properties of the reaction so that the products of the reaction form both vertically on a surface of the vertical fin and horizontally on a surface of an insulating layer (e.g., buried oxide). The products preferentially accumulate faster at the base of the vertical fin where the products from both the horizontal and vertical surfaces overlap. This accumulation or build-up results from a volume expansion stemming from the reaction. The faster accumulation in the corner areas near the base, limits the reaction first in the base region, thereby etching less material and forming the remaining, un-etched material into the sloping dielectric base.

Owner:GLOBALFOUNDRIES INC