Salient point structure for preventing salient point lateral etching and forming method

A technology of lateral etching and forming methods, which is applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of control limitations of the etching process, and achieve the effect of avoiding lateral undercutting

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below in conjunction with specific drawings and embodiments.

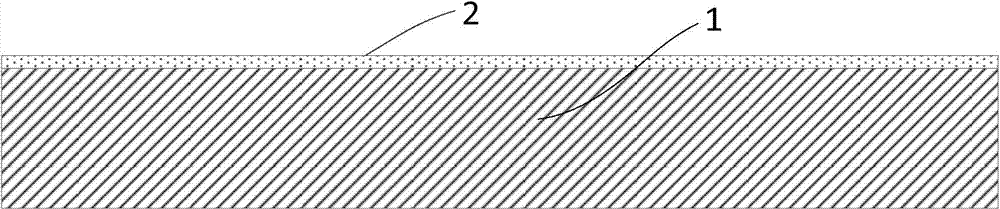

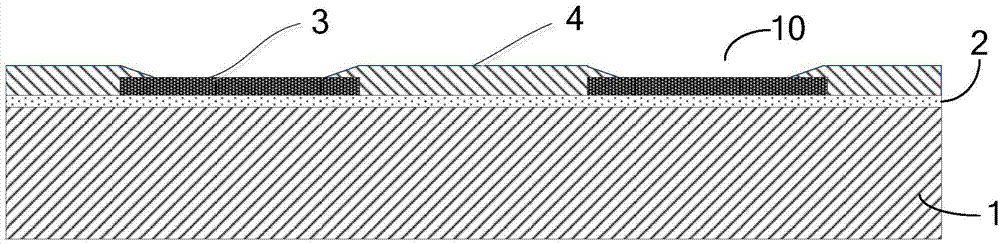

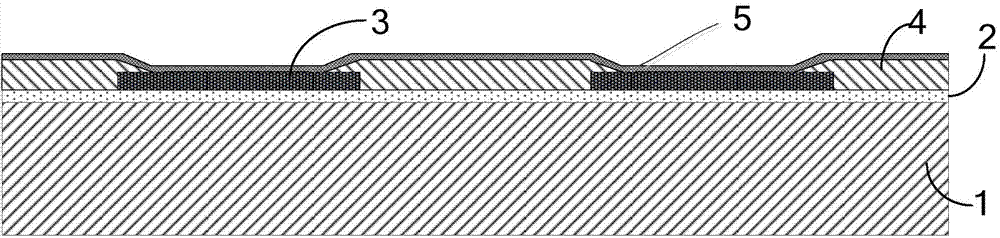

[0037] Such as Figure 10 Shown: In order to avoid the phenomenon of undercutting and improve the reliability and yield rate of micro-bump manufacturing, the present invention includes a substrate 1 and an insulating layer 2 located on the substrate 1; on the insulating layer 2 A metal pad 3 is provided, and the outer ring of the metal pad 3 is provided with a dielectric layer 4, and the dielectric layer 4 covers the insulating layer 2 and covers the edge of the outer ring of the metal pad 3; the metal pad 3 A copper post 8 is provided directly above the copper post 8, and the bottom end of the copper post 8 contacts and is electrically connected to the metal pad 3 through the seed layer 6 and the adhesive layer 5 in turn, and the bottom end of the copper post 8 passes through the seed layer 6 and the adhesive layer 5. The attachment layer 5 is supported on th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More