Manufacturing method of shield gate trench power device

A technology of power devices and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as process hidden dangers, decreased adhesion, photoresist defects, etc., to shorten process time and improve reliability performance, avoiding the effect of undercutting

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

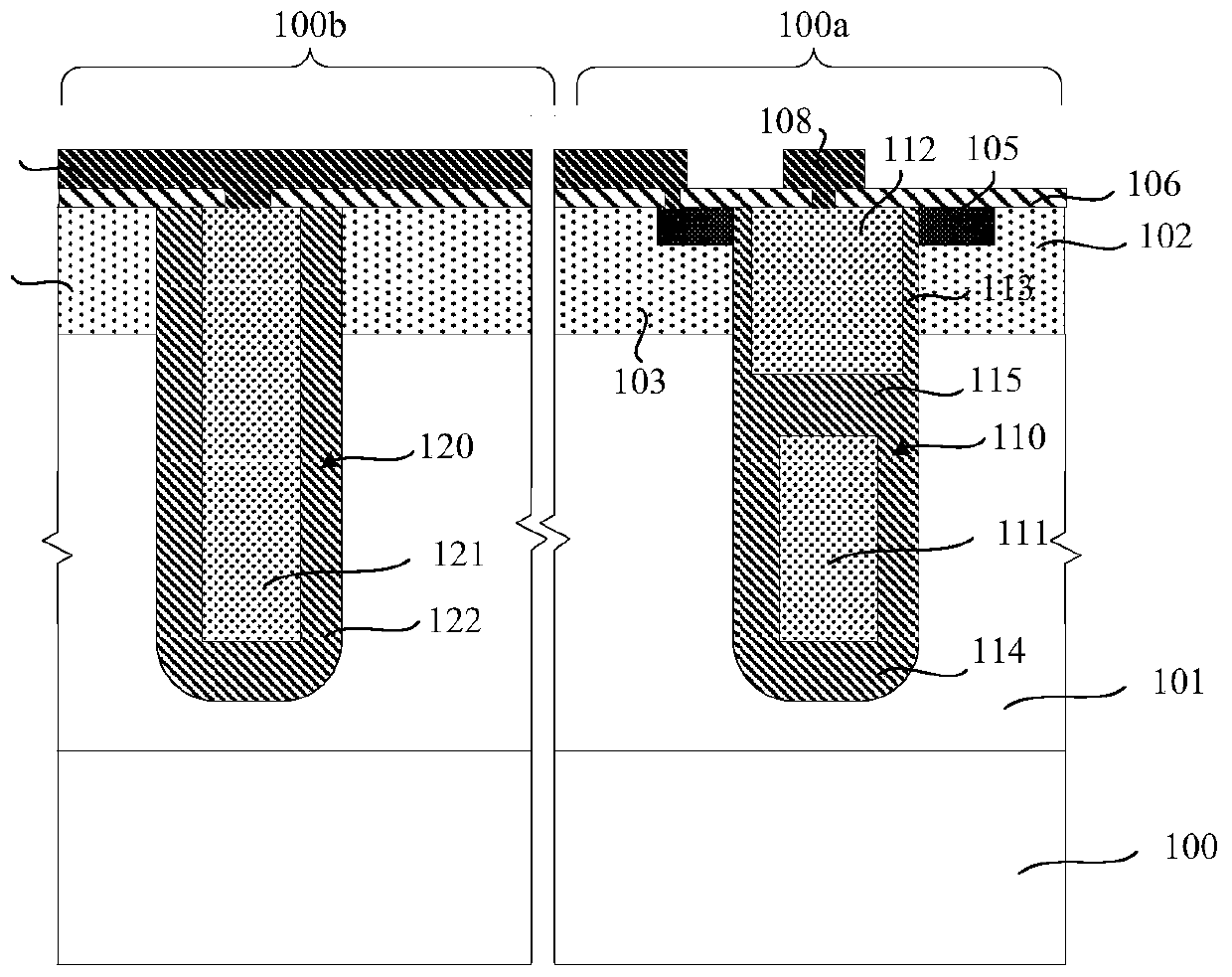

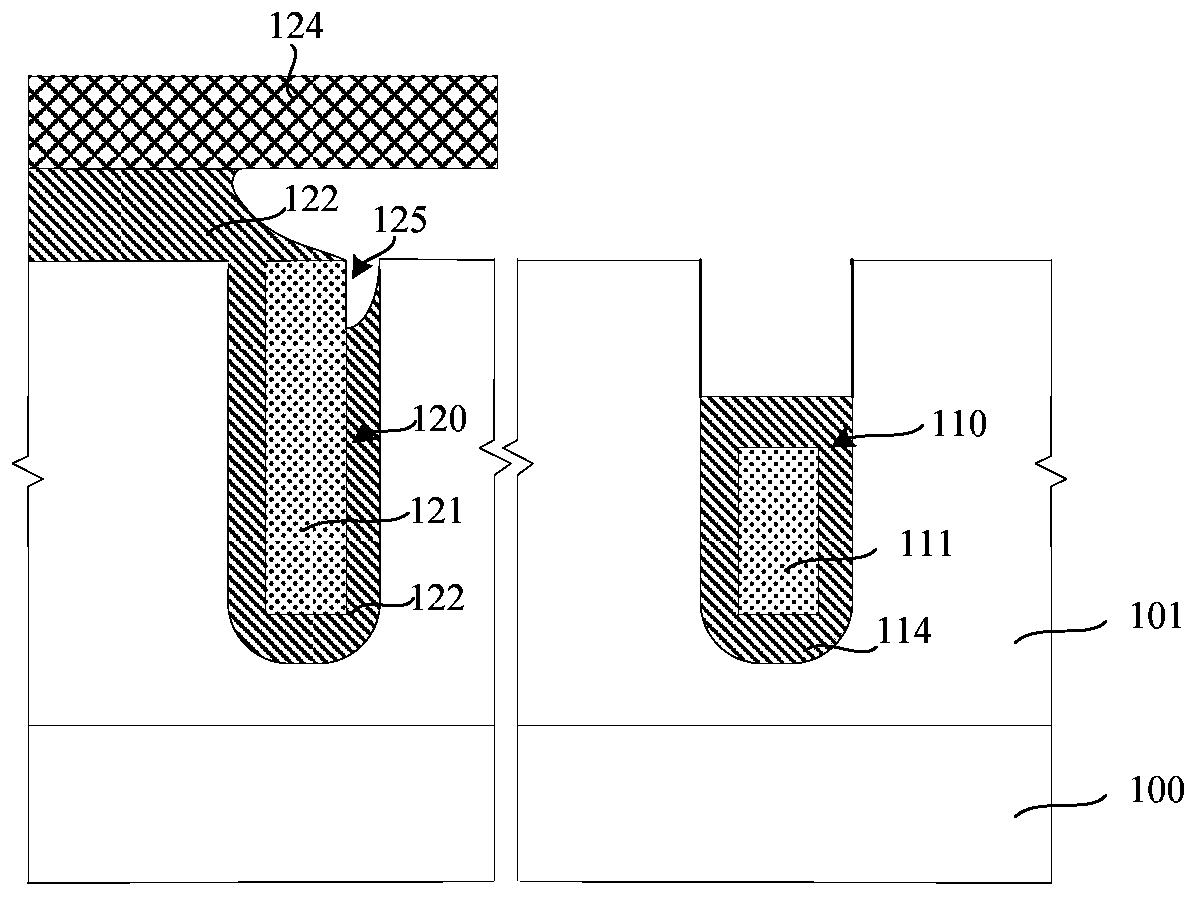

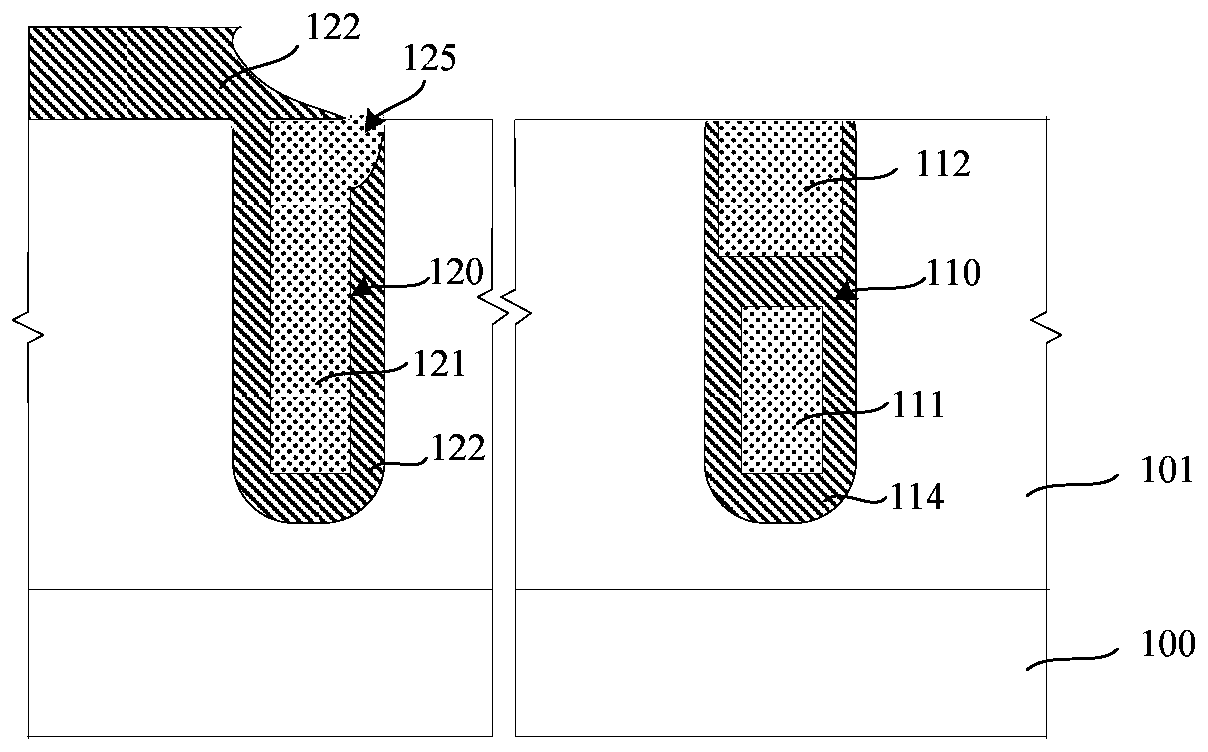

[0057] The manufacturing method of the shielded gate trench power device of the present invention will be further described in detail below with reference to the drawings and specific embodiments. According to the following description and accompanying drawings, the advantages and characteristics of the present invention will be clearer, however, it should be noted that the concept of the technical solution of the present invention can be implemented in many different forms, and is not limited to the specific implementation set forth herein. example. The drawings are all in very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0058] The terms "first", "second", etc. in the specification are used to distinguish between similar elements, and are not necessarily used to describe a specific order or chronological order. It is to be understood that the terms so used...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More