Semiconductor device

A semiconductor, n-type technology, applied in the direction of semiconductor devices, transistors, electric solid devices, etc., can solve the problem of concentration reduction in the anode region

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

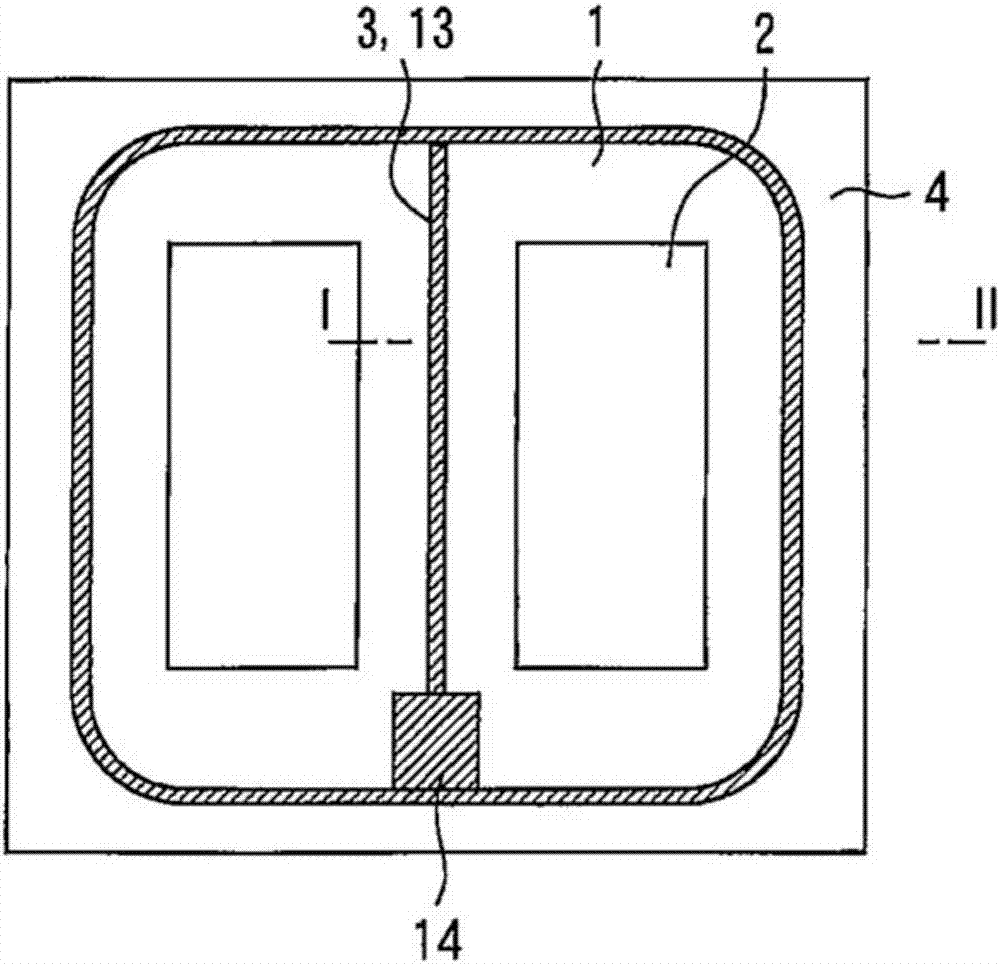

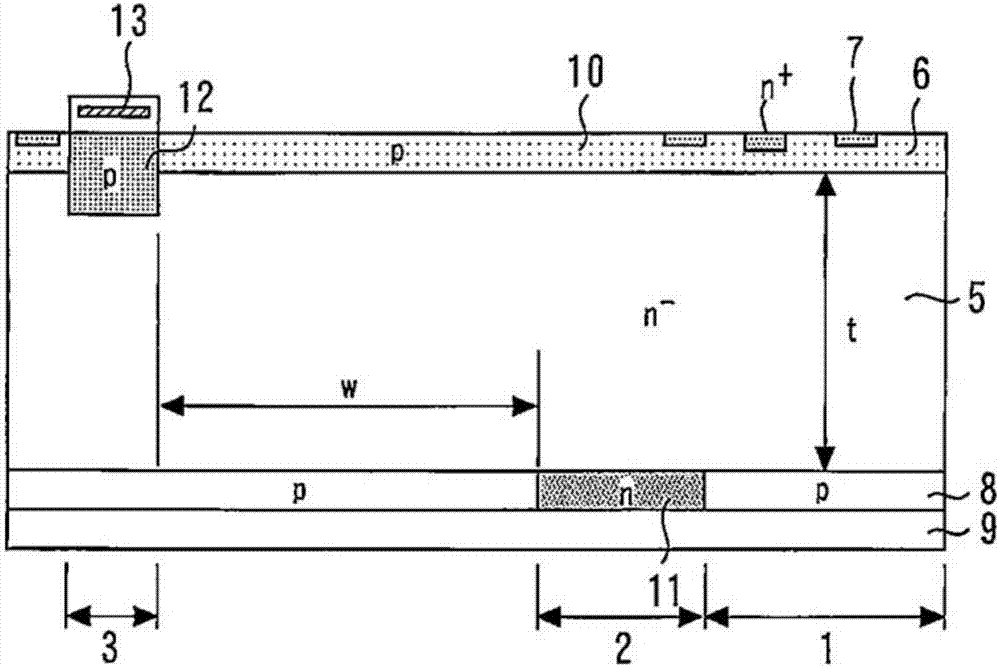

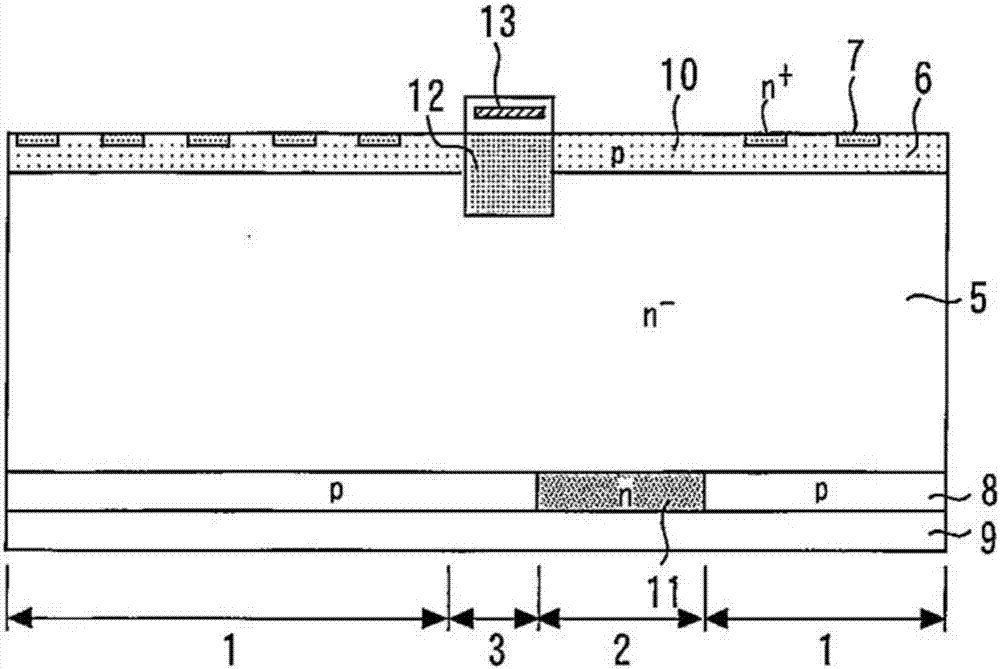

[0024] figure 1 It is a plan view showing the semiconductor device according to Embodiment 1 of the present invention. figure 2 is along figure 1 Sectional view of I-II. This semiconductor device is an RC-IGBT in which IGBT (Insulated Gate Bipolar Transistor) 1 and FWD (Free Wheeling Diode) 2 are formed on one semiconductor substrate. In addition, in the RC-IGBT, there is a wiring region 3 in addition to regions where the IGBT 1 and the FWD 2 operate, and a termination region 4 exists on the periphery of these regions.

[0025] IGBT 1 has: n - Type drift layer 5; p-type base layer 6 and n + type emitter layer 7, they are formed in n - the surface of the drift layer 5; and the p-type collector layer 8, which is formed on the n - type drift layer 5 on the back side. Collector electrode 9 is connected to p-type collector layer 8 . In the MOS structure on the surface side of the IGBT 1, by applying a voltage to the gate, electrons are supplied to the n - Type drift layer...

Embodiment approach 2

[0034] Figure 4 It is a plan view showing the semiconductor device according to Embodiment 2 of the present invention. Figure 5 is along Figure 4Sectional view of I-II. A plurality of trench gates 15 are formed. The IGBT 1 is formed in a region between the wiring region 3 and the termination region 4 and the FWD 2 . By forming the IGBT 1 in the vicinity of the wiring region 3 and the terminal region 4, the recovery loss of the FWD 2 can be reduced without reducing the effective area of the element (the total area of the IGBT 1 and the FWD 2 that can conduct electricity).

Embodiment approach 3

[0036] Figure 6 It is a plan view showing the semiconductor device according to Embodiment 3 of the present invention. IGBT 1 and FWD 2 are repeatedly formed at constant intervals in a region surrounded by gate wiring 13 in plan view. IGBT 1 and FWD 2 inside the RC-IGBT generate heat due to the flow of current. The maximum rated temperature of the element is usually 150 to 175°C. In order to lower the temperature of the heat-generating element, it is necessary to cool the heat dissipation fins in contact with the back side of the RC-IGBT by air cooling or water cooling. In a normal usage method, the period during which the current flows through the IGBT 1 and the period during which the current flows through the FWD 2 are alternated, and the timings at which the temperatures of the IGBT 1 and the FWD 2 reach peak values are shifted. Therefore, by repeatedly forming IGBT 1 and FWD 2 at fixed intervals, the heat generated when one of IGBT 1 and FWD 2 is energized can also b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More