Channel delay simulation device and method

A channel delay and simulation device technology, applied in the field of signal processing, can solve the problem of storage resource consumption, achieve the effects of less sampling data, high channel delay accuracy, and avoid the dependence of high sampling frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

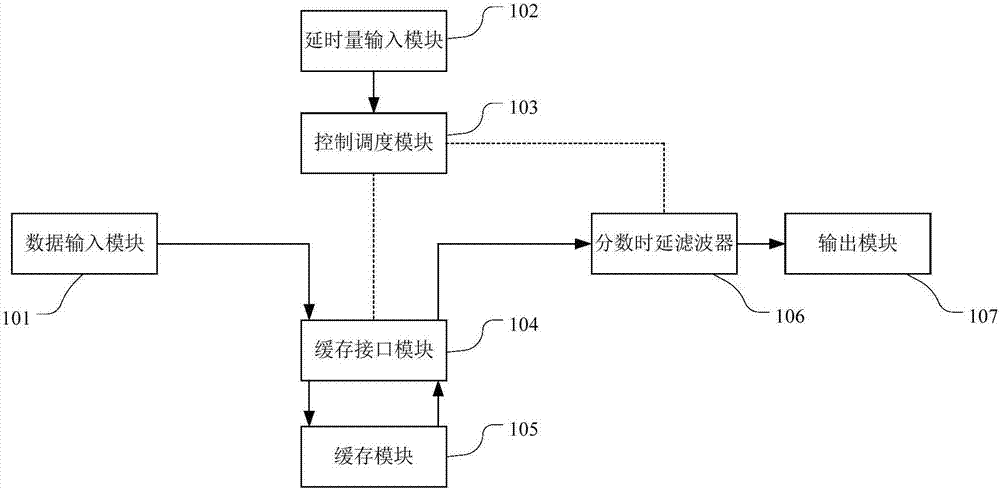

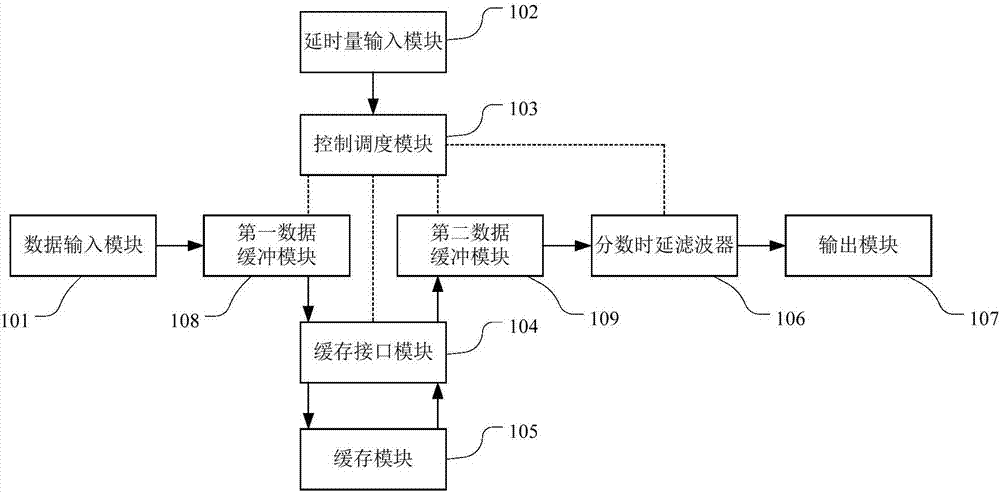

[0061] see figure 1 , is a schematic block diagram of a channel delay simulation device provided by an embodiment of the present invention. The solid line arrows in the figure indicate the flow direction of data, and the dotted line segments indicate the process of control scheduling. The channel delay simulation device may include: a data input module 101 , a delay amount input module 102 , a control scheduling module 103 , a buffer interface module 104 , a buffer module 105 , a fractional delay filter 106 and an output module 107 .

[0062] Preferably, the channel delay simulation device can be implemented on FPGA, which is mainly used for channel delay simulation of navigation satellites.

[0063] The data input module 101 is used for receiving input data to be processed by channel delay.

[0064] The delay amount input module 102 is configured to receive the channel delay amount required by the input data.

[0065] The control scheduling module 103 is respectively connec...

Embodiment 2

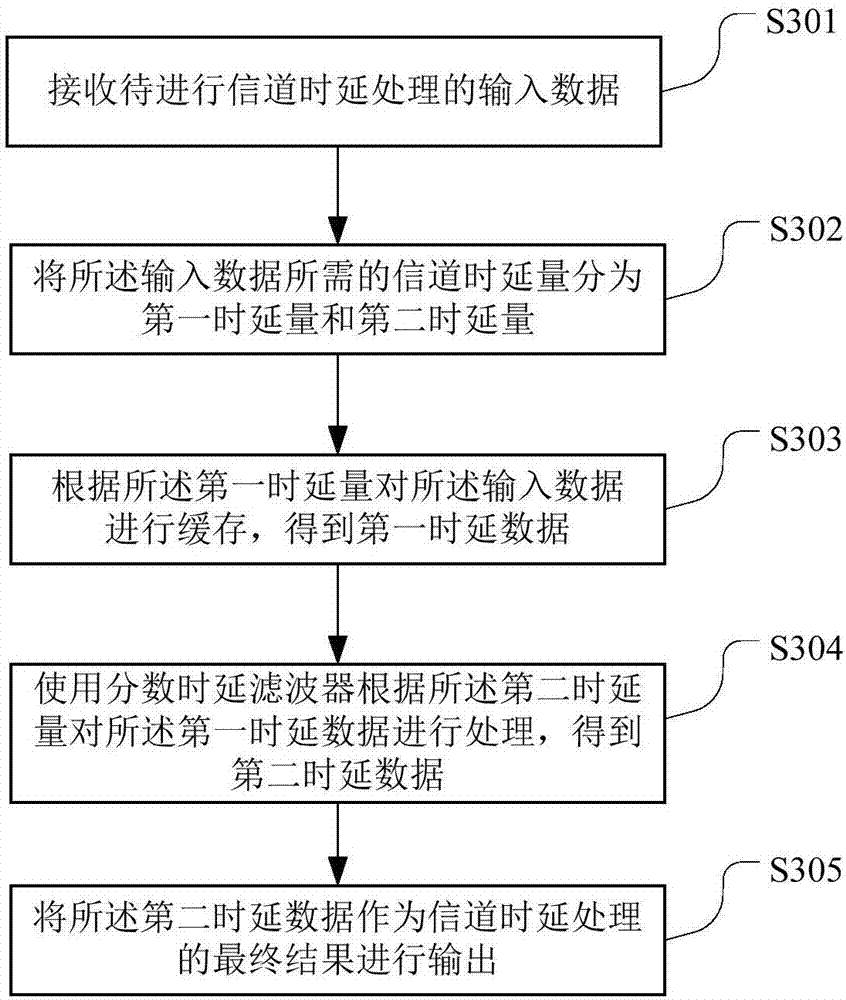

[0102] see image 3 , is a schematic flowchart of a channel delay simulation method provided in an embodiment of the present invention, and the method may include:

[0103] Step S301, receiving input data to be subjected to channel delay processing;

[0104] Step S302, divide the channel delay required by the input data into a first delay and a second delay according to the period of the sampling clock, the first delay is the channel delay relative to An integer part of the period of the sampling clock, and the second delay amount is a fractional part of the channel delay amount relative to the period of the sampling clock;

[0105] Step S303, buffering the input data according to the first delay amount to obtain first delay data;

[0106] Step S304, using a fractional delay filter to process the first delay data according to the second delay amount to obtain second delay data;

[0107] Step S305, outputting the second delay data as a final result of channel delay processin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More