A Two-Stage Switch Structure Implementation Method Based on Adjacent Port Scheduling Information

A technology for switching structure and scheduling information, which is applied in the field of Internet information transmission, and can solve the problems of port rate increase, impossibility, reduction of FMLB high-speed switching capability and scalability, etc., to achieve early scheduling, avoid cell conflicts, and long execution time Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

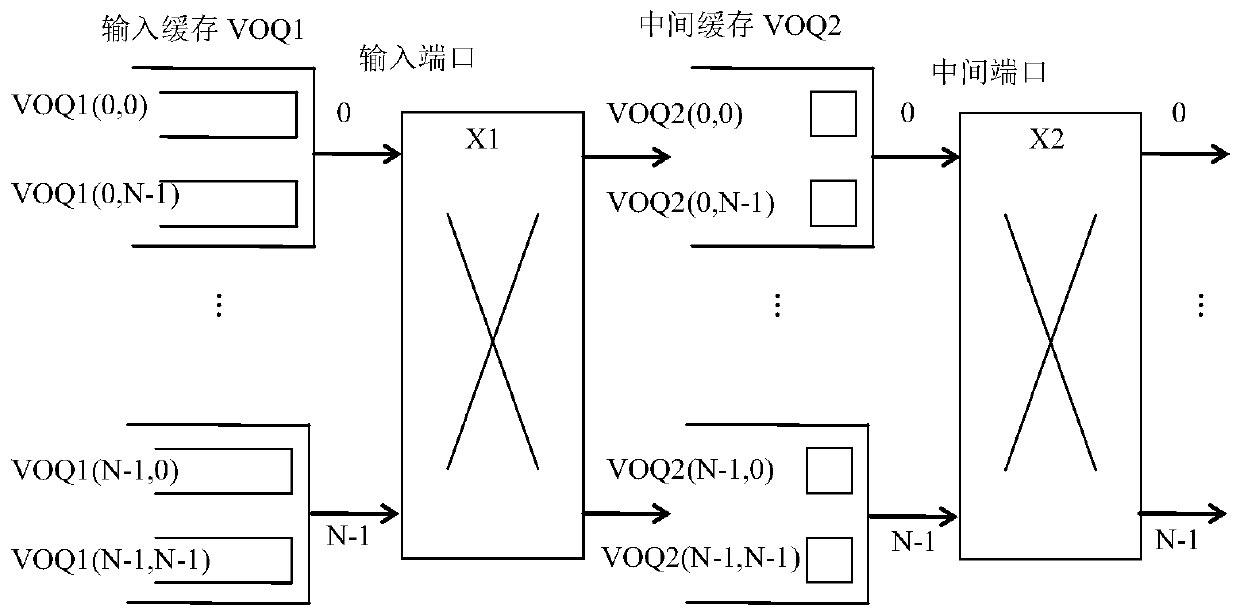

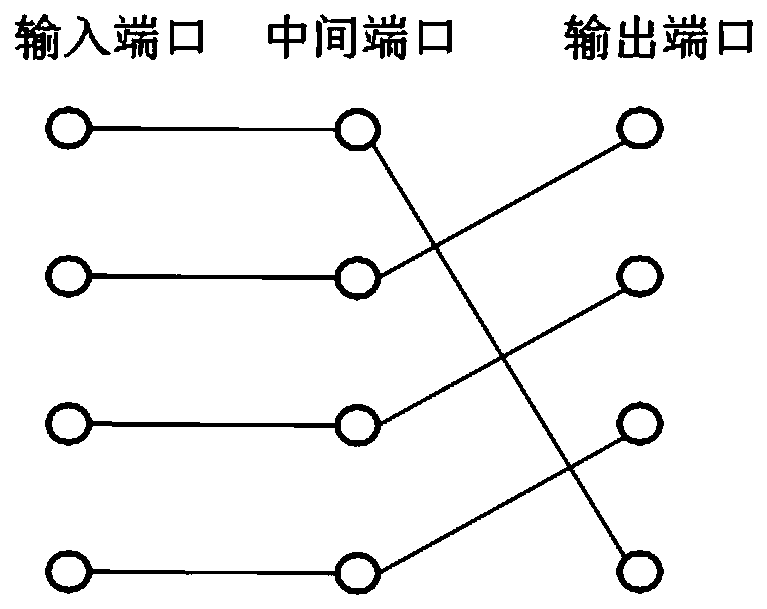

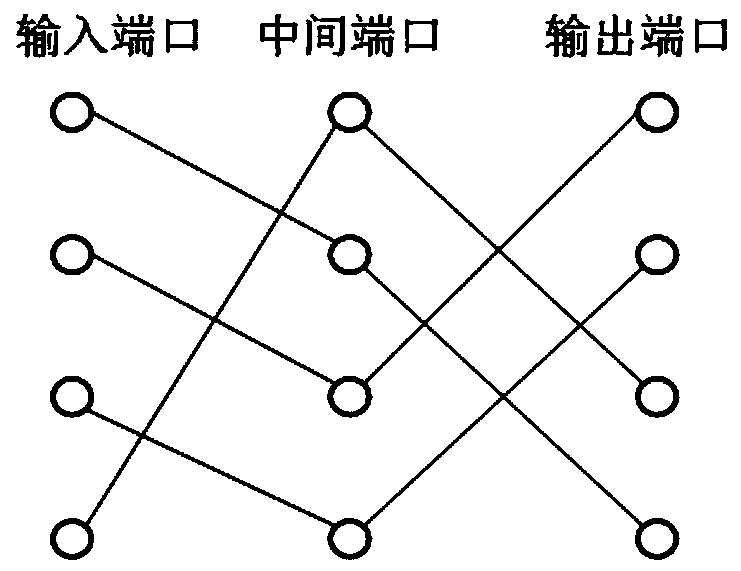

[0049] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. A two-stage switching structure implementation method based on adjacent port scheduling information (ASRLB Adjacent-Scheduling-Results based LoadBalanced two-stage switch architecture), including two-stage crossbar (X1 and X2), and the input buffer before the first-stage crossbar, The intermediate cache between the two levels of crossbar; the input port of the first level crossbar is the input port of the switch structure, the input port of the second level crossbar is the intermediate port, and the output port is the output port; it is set between adjacent input ports Data communication link, before the end of each time slot, each input port will copy the scheduling result information of this time slot to its adjacent input port through the data communication link; and before the end of each time slot, the intermediate port will Its bu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More