Embedded fan-out type silicon pinboard applied to three-dimensional system-level packaging and manufacturing method

A system-in-package, fan-out technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as the inability to further meet the application of multi-layer three-dimensional systems, reduce production costs, and improve product reliability. The effect of shortening the process flow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

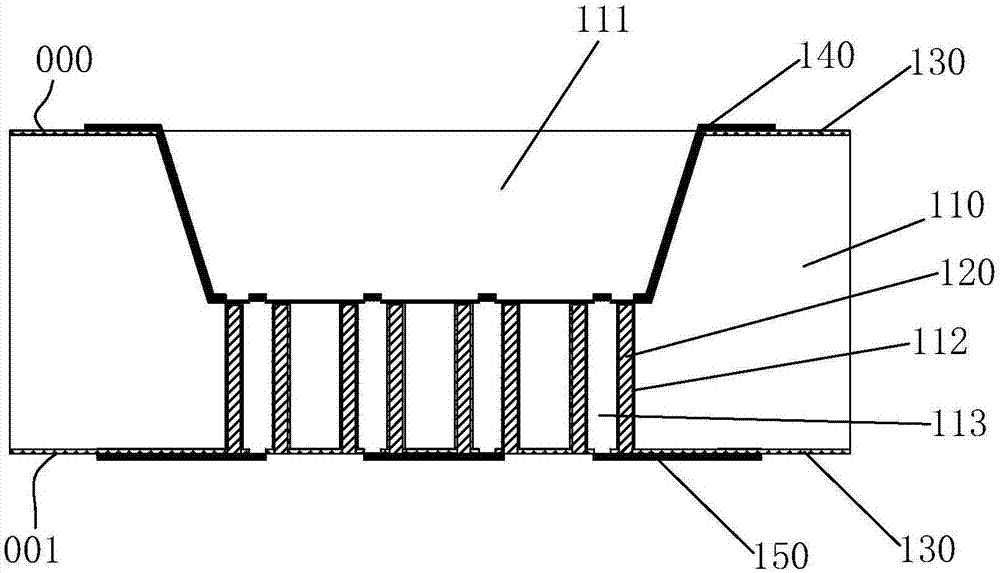

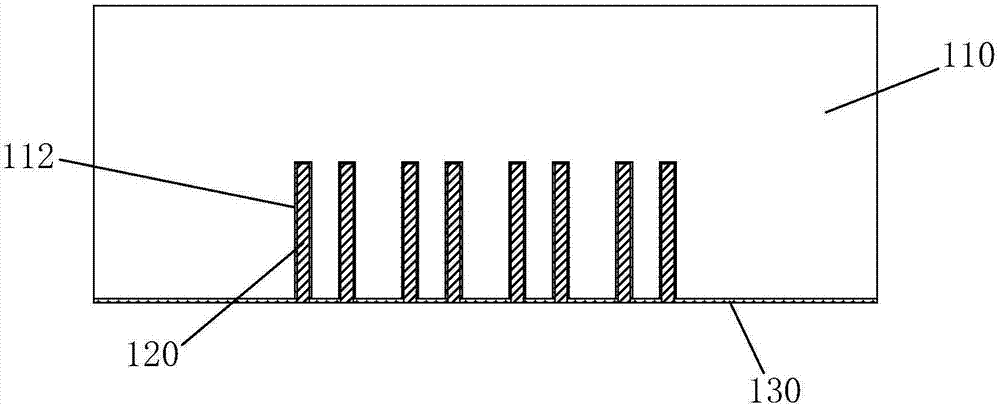

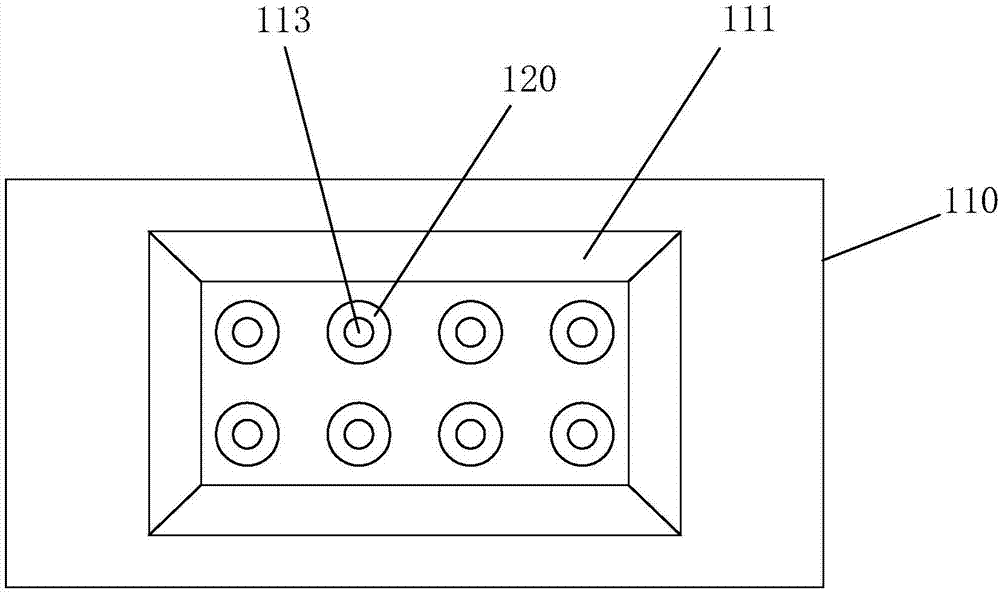

[0046] A new type of embedded fan-out silicon interposer structure for 3D system-in-package applications such as figure 1As shown, it includes a silicon substrate 110 made of low-resistance silicon material (≤0.1Ω·cm). The silicon substrate 110 has a front surface 000 and a back surface 001. The diameter of the cavity 111 gradually decreases from the front to the back), and the back is provided with a vertical interconnection structure extending to the bottom of the cavity 111 . The vertical interconnection structure is formed by the following structure: the back surface 001 of the silicon substrate 110 is provided with several annular grooves 112 extending to the bottom of the cavity 111 and independent of each other, and the annular grooves 112 are filled with insulating materials to form an annular insulating layer 120 The silicon pillars within the inner ring of the annular insulating layer 120 form conductive pillars 113 , that is, several mutually independent conductive ...

Embodiment 2

[0064] A new type of embedded fan-out silicon interposer structure for 3D system-in-package applications such as Figure 6 As shown, it includes a silicon substrate 210 made of high-resistance silicon material (≥1000Ω·cm). The silicon substrate 210 has a front surface 000 and a back surface 001. The front surface is provided with a concave cavity 211 (preferably concave The diameter of the cavity 211 gradually decreases from the front to the back), and the back is provided with a vertical interconnection structure extending to the bottom of the cavity 211. The vertical interconnect structure is formed by the following structure: the back of the silicon substrate 210 is provided with a plurality of through holes 212 extending to the bottom of the cavity 211 and independent of each other, and the through holes 212 are filled with conductive materials to form the conductive pillars 220 . The front and back of the silicon substrate 210 and the surface of the concave cavity are pro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More