Structure for improving stacking mounting of multiple chips and technological method of structure

A process method and multi-chip technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of chip cover, chip breakage, etc., to achieve the effect of convenient layout, improved utilization, and improved process methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

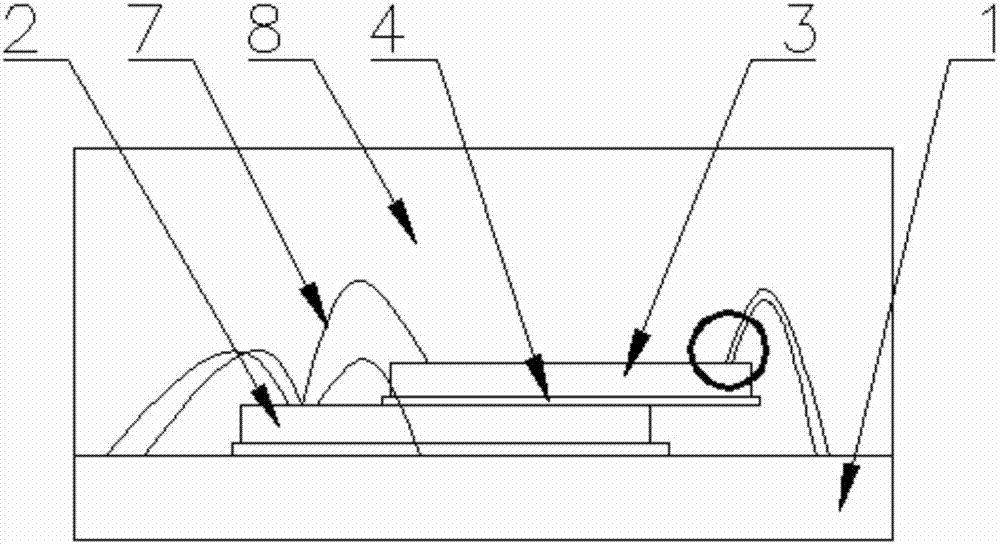

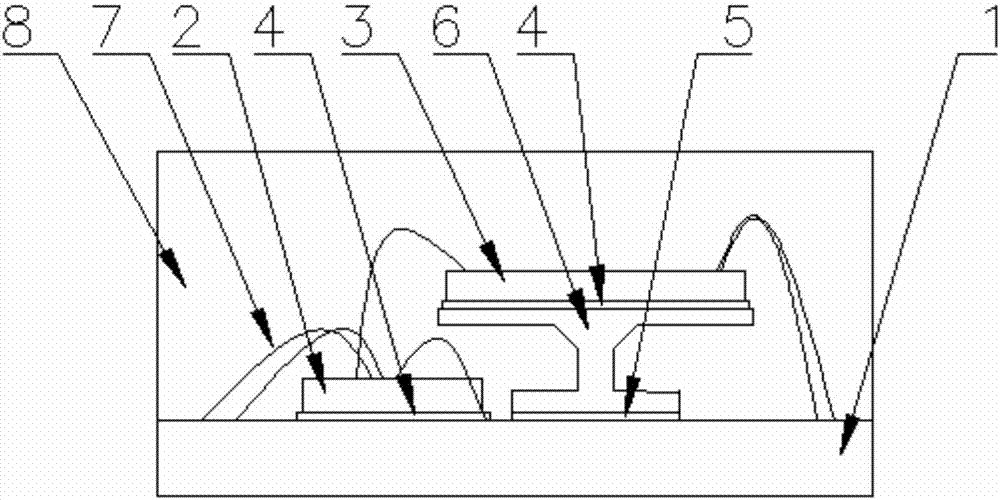

[0047] Such as image 3 As shown, an improved multi-chip stacking structure in this embodiment includes a frame base material 1, and the front side of the frame base material 1 is provided with a lower chip 2 through a die-mounting glue 4, and the frame base material 1 The front side is provided with an "I"-shaped bracket 6 through the film 5, and the front side of the "I"-shaped bracket 6 is provided with an upper chip 3 through a mounting glue 4. The frame substrate 1, the lower chip 2 and the upper chip 3 All are connected by bonding wires 7, and the lower chip 2, the upper chip 3, the "I"-shaped bracket 6 and the bonding wires 7 are encapsulated with a plastic encapsulant 8;

[0048] The "I"-shaped support 6 is an "I"-shaped support with a large top and a small bottom, and the area and height of the top surface and the bottom surface are customized according to the actual chip specifications, package thickness, and wiring capability;

[0049] Part of the area of the low...

Embodiment 2

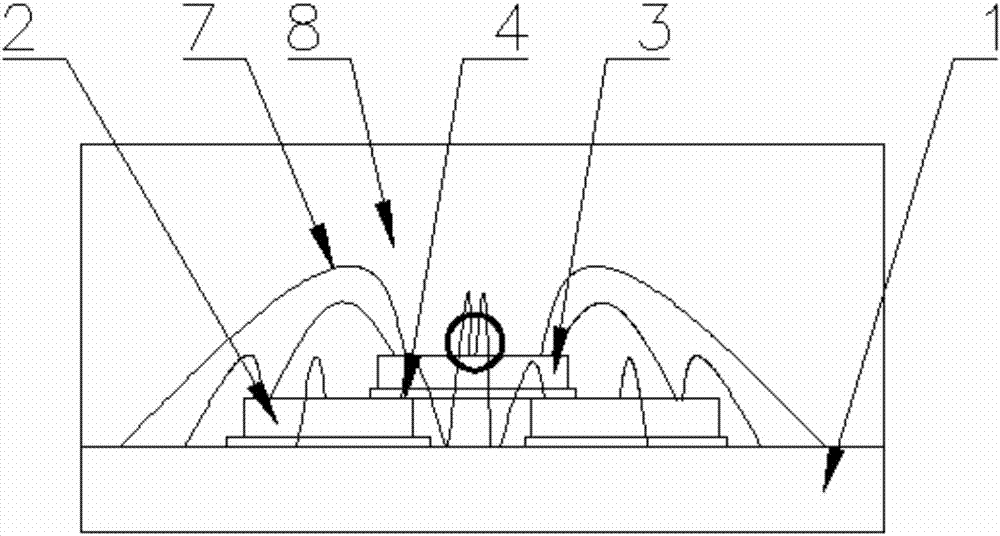

[0063] see Figure 11 The difference between Embodiment 2 and Embodiment 1 is that there are multiple lower-layer chips 2 .

[0064] Its process method comprises the following steps:

[0065] Step 1, see Figure 12 , take a frame substrate;

[0066] Step two, see Figure 13 , mounting multiple lower-layer chips on the frame substrate;

[0067] Step three, see Figure 14 , mount the "I"-shaped bracket on the frame substrate;

[0068] Step 4, see Figure 15 , Mount the upper chip on the "I"-shaped bracket;

[0069] Step five, see Figure 16 , the frame base material, the lower chip and the upper chip are all connected by bonding wires;

[0070] Step six, see Figure 17 , encapsulation.

[0071] Or its processing method comprises the steps:

[0072] Step 1, see Figure 18 , take a frame substrate;

[0073] Step two, see Figure 19 , mounting multiple lower-layer chips on the frame substrate;

[0074] Step three, see Figure 20 , wire bonding operation between the l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More