A high-precision layer-to-layer alignment manufacturing method for a multi-layer circuit board

A technology of a multilayer circuit board and a manufacturing method, which is applied in the direction of multilayer circuit manufacturing, etc., can solve the problems that the alignment accuracy between the layers of the multilayer circuit board cannot meet the production quality requirements and the accuracy error, and avoid multiple punching positions. Influence of precision, effect of improving inter-layer alignment, and reducing inter-layer deviation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The following specific examples will be used to describe the present invention in detail, and the exemplary embodiments and descriptions of the present invention are used to explain the present invention, but not as a limitation to the present invention.

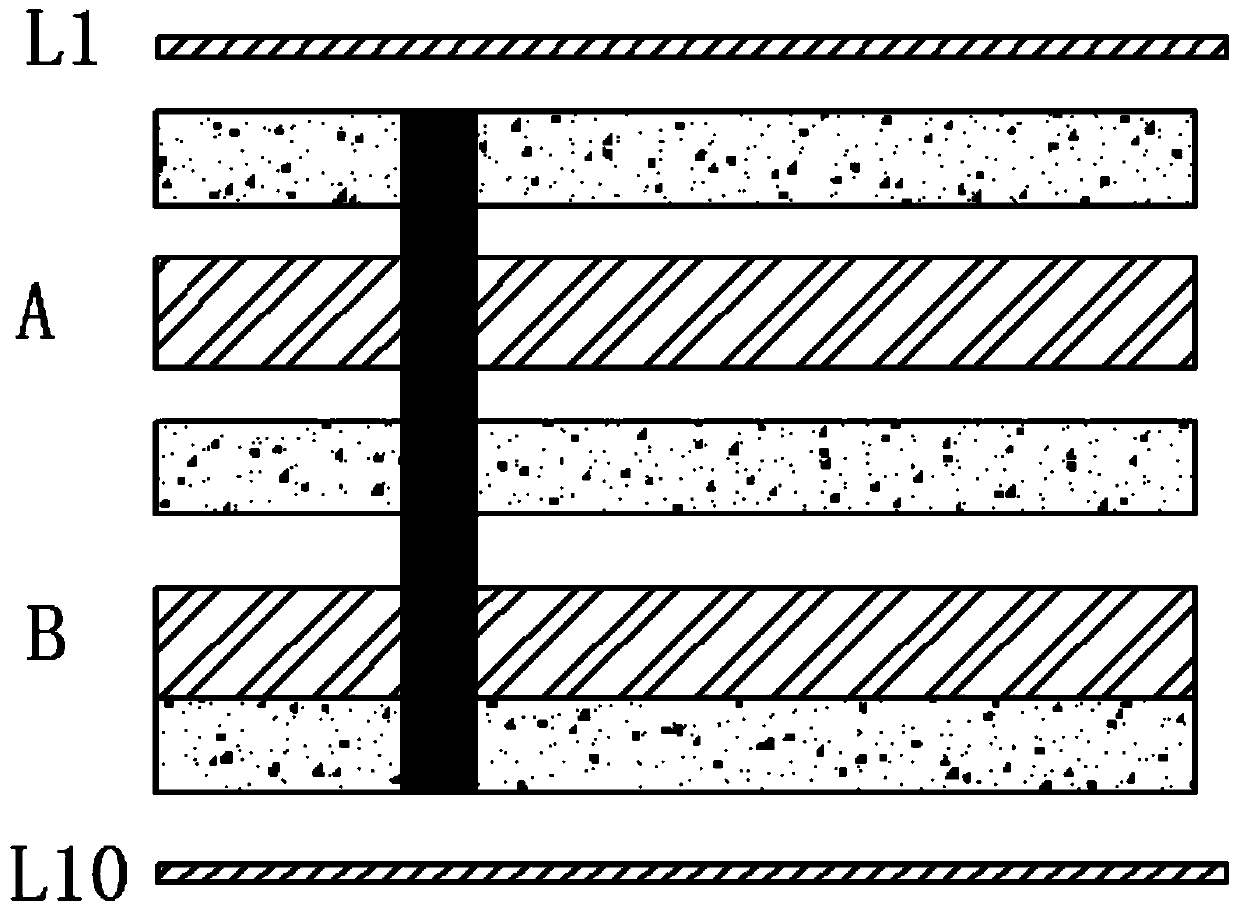

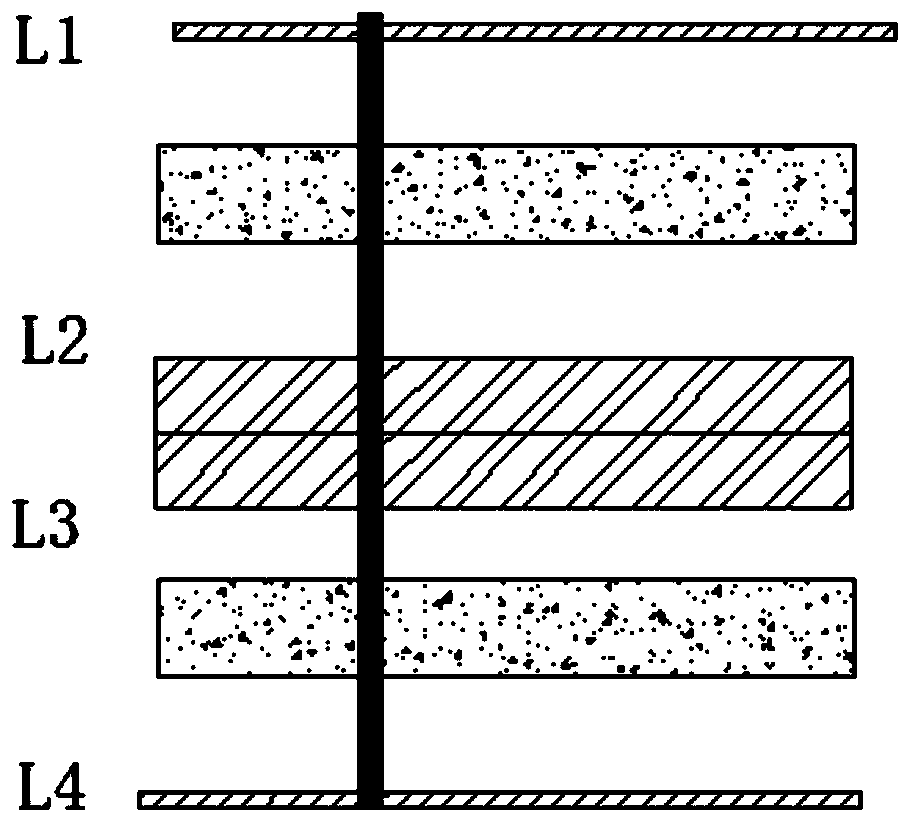

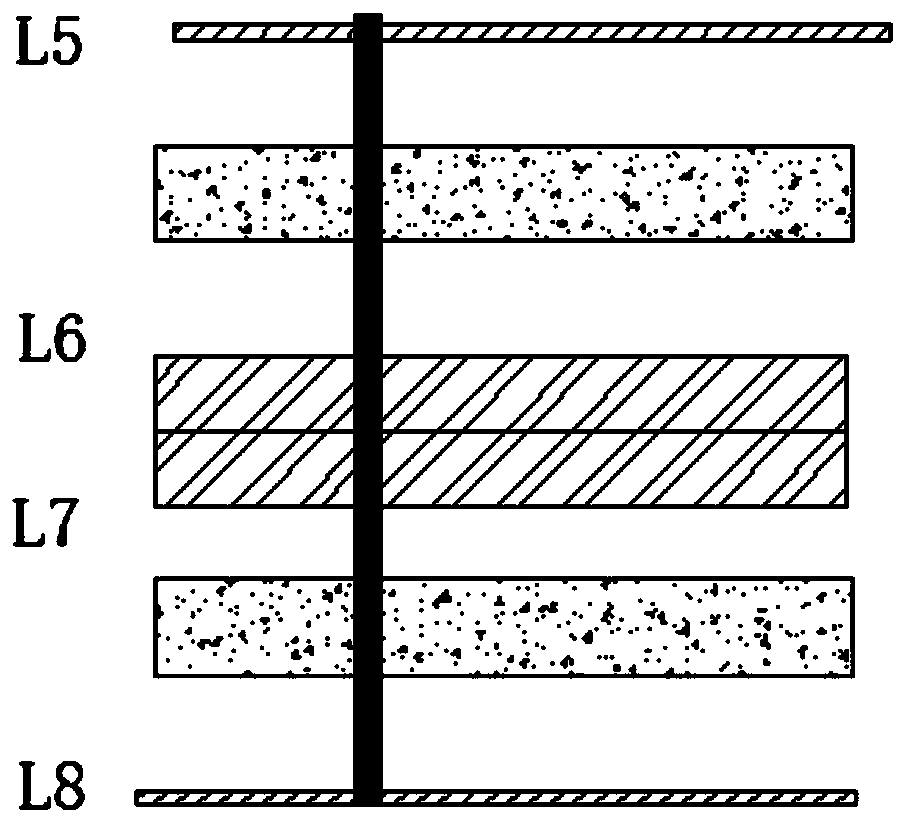

[0030] Such as Figure 1 to Figure 4 As shown, a high-precision layer-to-layer alignment manufacturing method for a multi-layer circuit board,

[0031] (1) It will be necessary to make multi-layer circuit boards for stacking, according to the preset structure of the first sub-board (A board). The structure of the first sub-board (A board) includes at least the first core board (L2 / L3 layer), more than one adhesive sheet, and the outer layer of copper foil (L1 / L4 layer); the first core board is patterned on the inner layer Transfer, develop and etch to make the first layer of CCD fusion positioning block, and then after automatic optical inspection and browning treatment of the inner layer, the first core board is mad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More