Template convolution implementation method and system based on FPGA (Field Programmable Gate Array)

An implementation method and system implementation technology, applied in the field of image processing, can solve the problems that traditional methods can no longer meet the requirements, and achieve the effect of improving convolution processing results and improving processing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

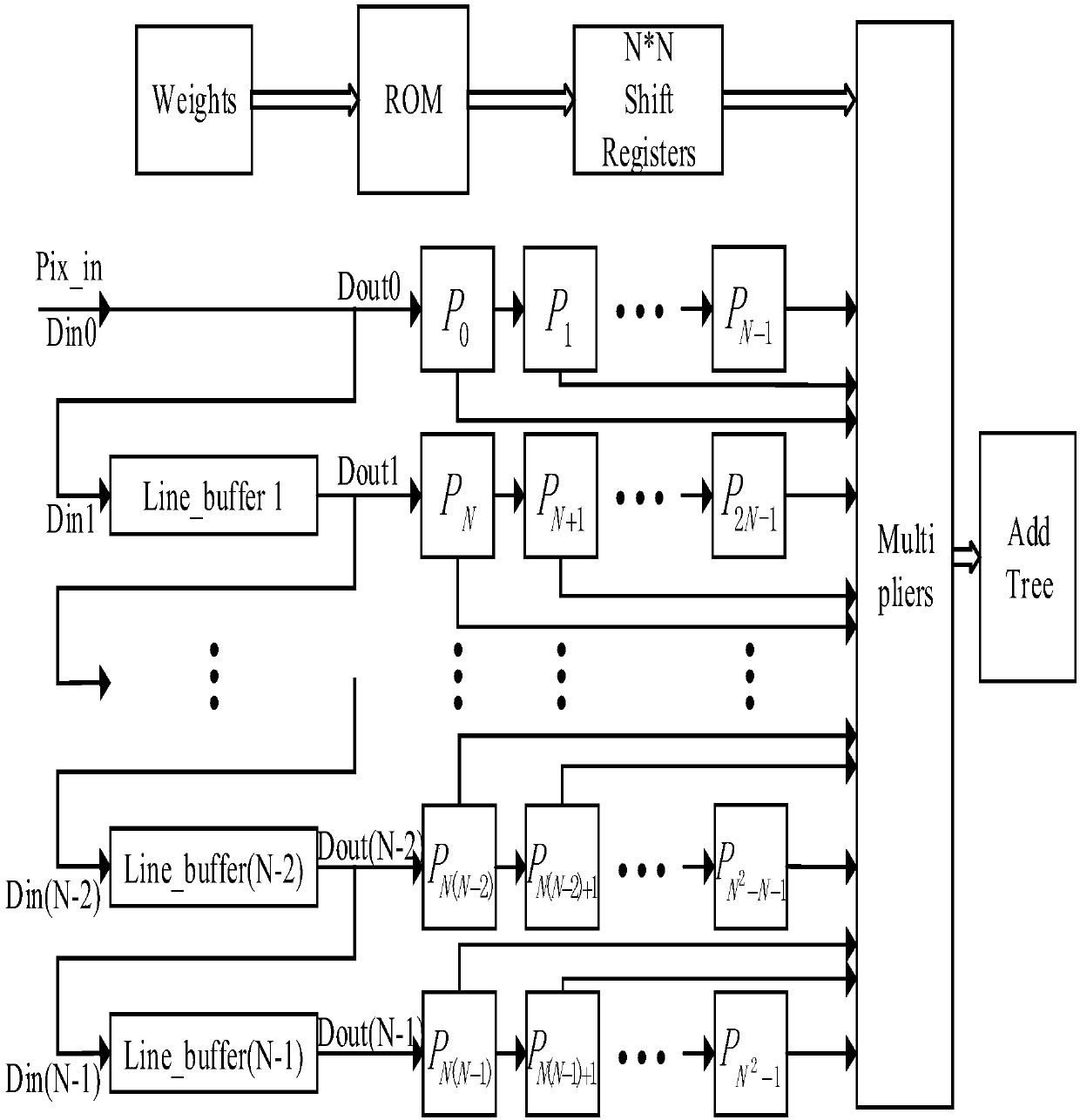

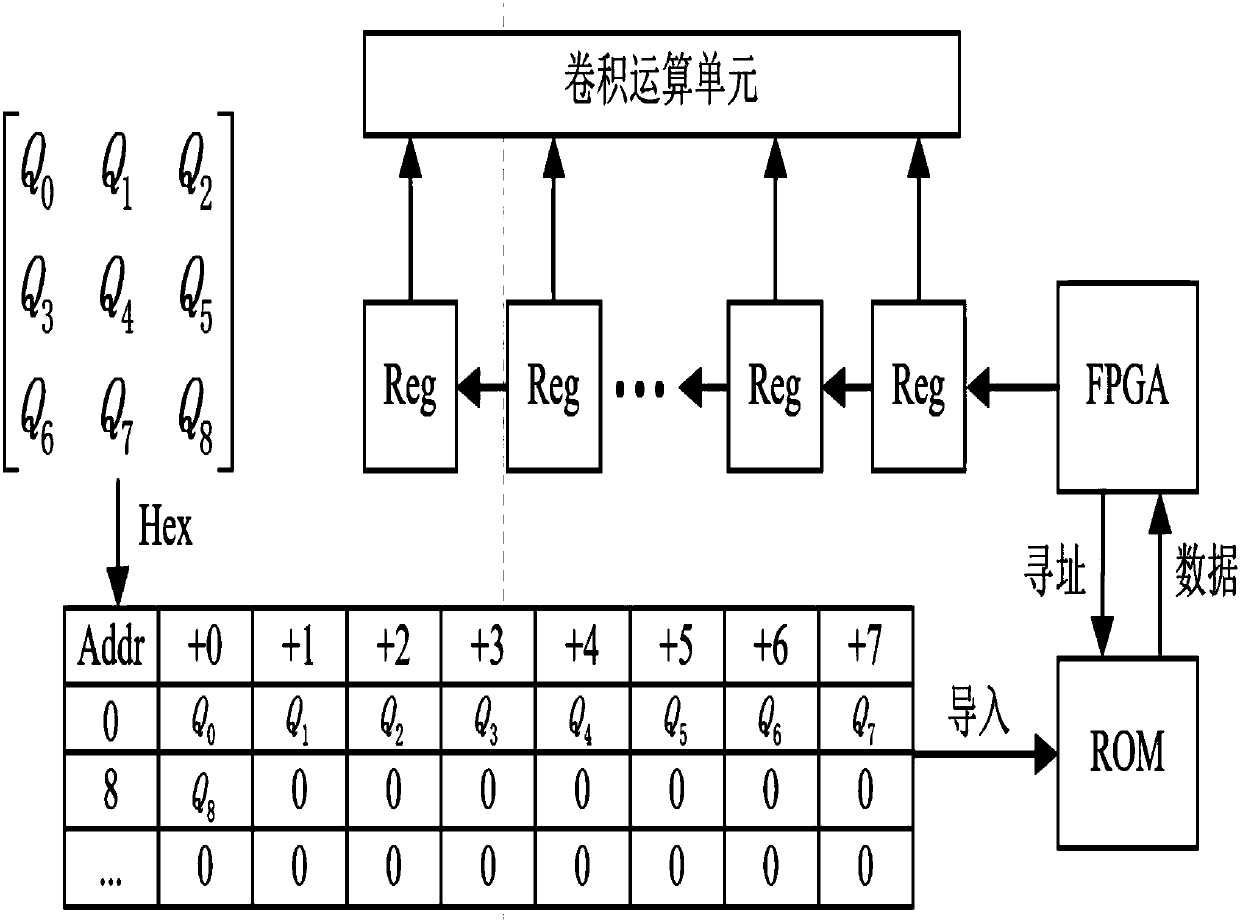

[0020] Embodiment 1 based on the invention, a method for implementing template convolution based on FPGA, comprising the steps of: obtaining the data bit width of the image data, selecting a register set corresponding to the depth based on the data bit width; obtaining the image data and storing it in the The register group is used to obtain the convolution coefficient and store it in ROM; obtain the selection parameters used to associate the register group with the convolution coefficient; extract the data stored in the register group and the corresponding convolution coefficient and perform multiplication, based on the adder group The results of the multiplication operations are summed to implement a convolution operation.

[0021] The method based on the embodiment further includes: selecting a shift register group corresponding to the depth based on the data bit width, the shift register group is used to obtain image data, and the register group obtains image data from the ...

Embodiment 2

[0032] Embodiment 2 based on the invention, a template convolution implementation system based on FPGA, including: a parameter input module, used to obtain the data bit width of the image data, and select a corresponding depth register set based on the data bit width, also used for Obtain the shape and size of the convolution window, and automatically generate a corresponding convolution operation unit based on the parameters; the data input module is used to obtain image data and store it in the register set, obtain the convolution coefficient and import it into ROM; the calculation module uses To obtain selection parameters for associating the register set with the convolution coefficient; the calculation module is also used to extract the data stored in the register set and the corresponding convolution coefficient and perform multiplication, and perform the multiplication operation based on the adder set The results are added together to implement the convolution operation....

Embodiment 3

[0037] Based on the embodiment 3 of the invention, the process of realizing the convolution of FPGA is realized:

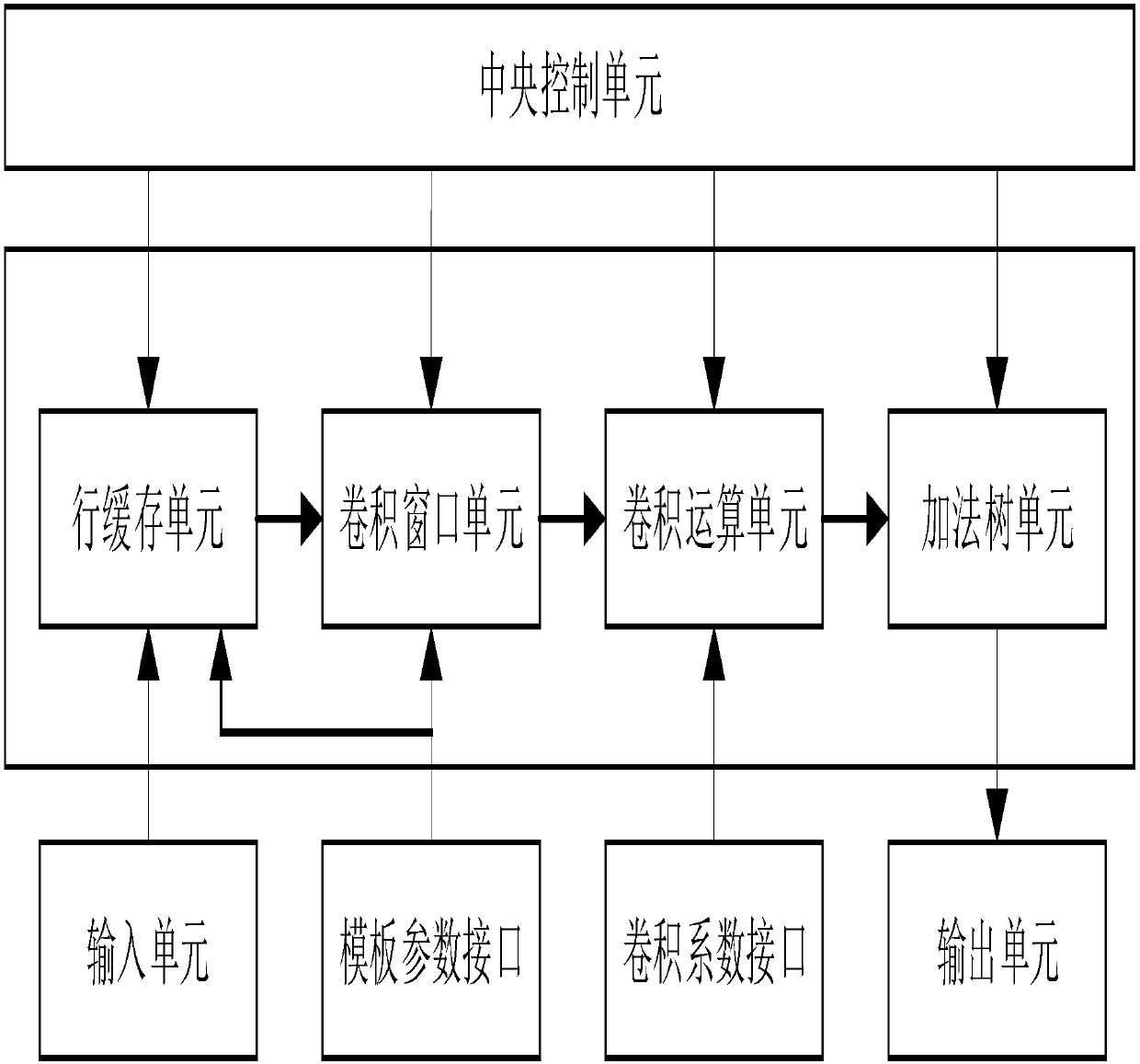

[0038] Such as figure 1 The basic structure of the FPGA shown includes a central control unit, an input unit (that is, a data interface), a line buffer unit (composed of shift registers), a convolution window unit (register bank), and a convolution operation unit (acquiring data from the register bank) and perform multiplication), addition tree unit (adder group), template parameter interface (ie data interface or data input terminal), convolution coefficient interface (ie ROM, used to store multiplication coefficients) and output unit; wherein, the input unit Connect the line cache unit, the line cache unit is connected to the convolution window unit, the convolution window unit is connected to the convolution operation unit, the convolution operation unit is connected to the addition tree unit, and the addition tree unit is connected to the output unit; the temp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com