CPLD-based clock counting method and device, and medium

A clock counting and counting cycle technology, applied in the field of CPLD, can solve problems such as logic units can no longer be used, CPLD work efficiency is reduced, and the number of logic units is in short supply.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

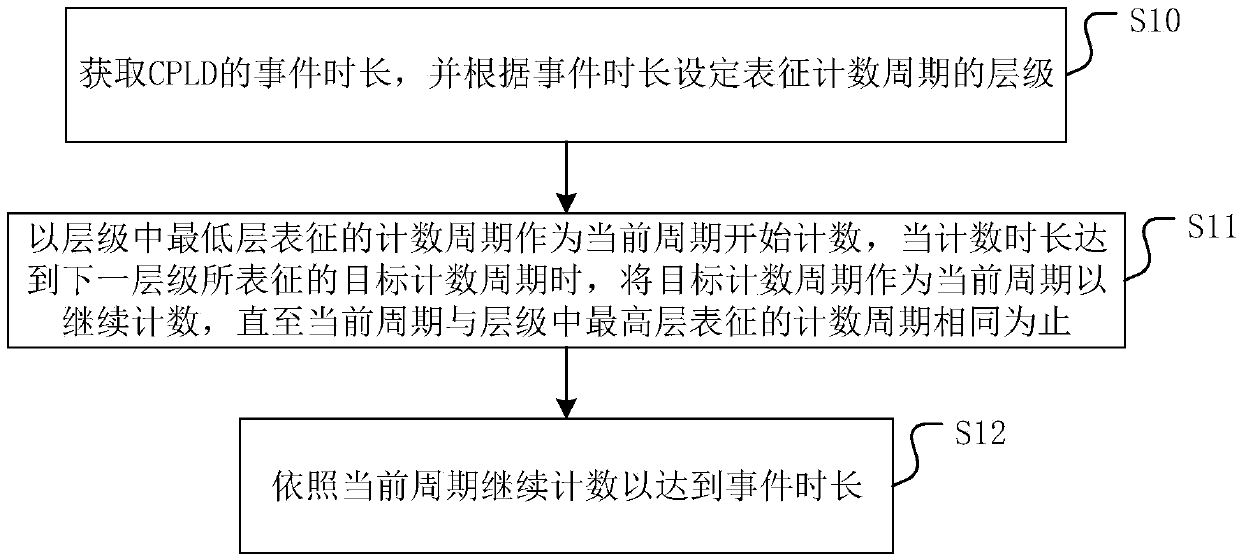

[0039] figure 1 This is a flow chart of a method for counting clocks based on CPLD provided by an embodiment of the present invention. Please refer to figure 1 , the specific steps of the CPLD-based clock counting method include:

[0040] Step S10: Acquire the event duration of the CPLD, and set the level representing the counting period according to the event duration.

[0041] Among them, the hierarchy includes at least two layers, and the lowest layer represents the system period; the duration of the counting period is positively correlated with the level of the hierarchy, and in the adjacent hierarchy, the counting period represented by the higher hierarchy is equal to the counting period represented by the lower hierarchy. integer multiples.

[0042] It should be noted that the "count" in this document refers to the clock count of the CPLD. In this step, the duration of the event executed by the CPLD needs to be obtained first, and then the appropriate level of the co...

Embodiment 2

[0049]On the basis of the above-mentioned embodiment, as a preferred implementation manner, the counting period represented by the lowest level in the hierarchy is used as the current period to start counting, specifically:

[0050] The display look-up table LUT is used as the counter to start counting with the count cycle represented by the lowest layer in the hierarchy as the current cycle.

[0051] It should be noted that the display lookup table LUT is essentially a RAM (memory), which usually has the characteristics of four inputs. Each LUT can represent a four-bit binary number, and the counter is a logical structure composed of one or more LUTs. , the number of LUTs used should be determined according to the number of digits required for the count, which is not specifically limited here. Since LUT is a common component in CPLD, better compatibility with CPLD can be achieved by using LUT as a counter, thereby ensuring the stability of counting.

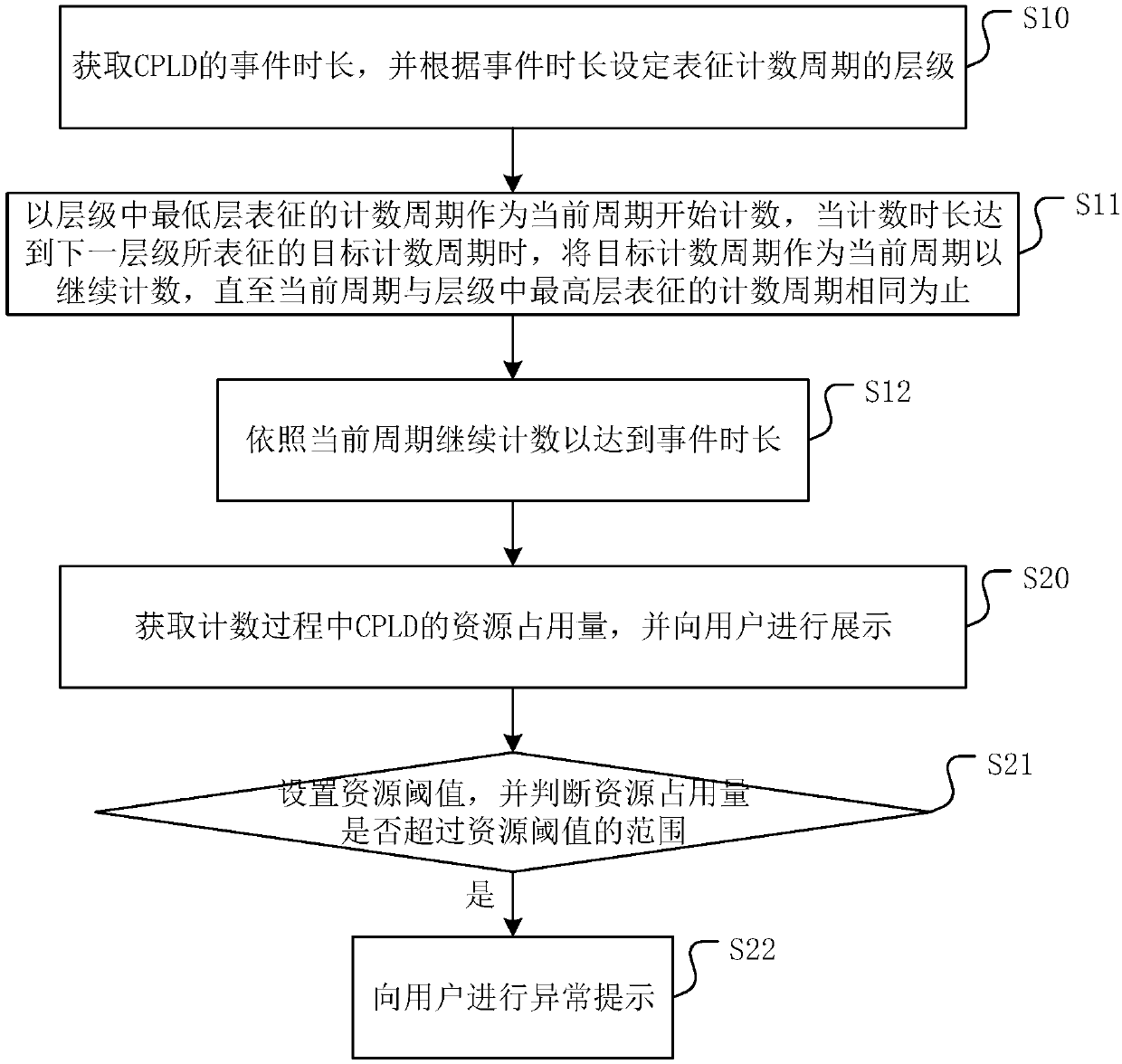

[0052] figure 2 This ...

Embodiment 3

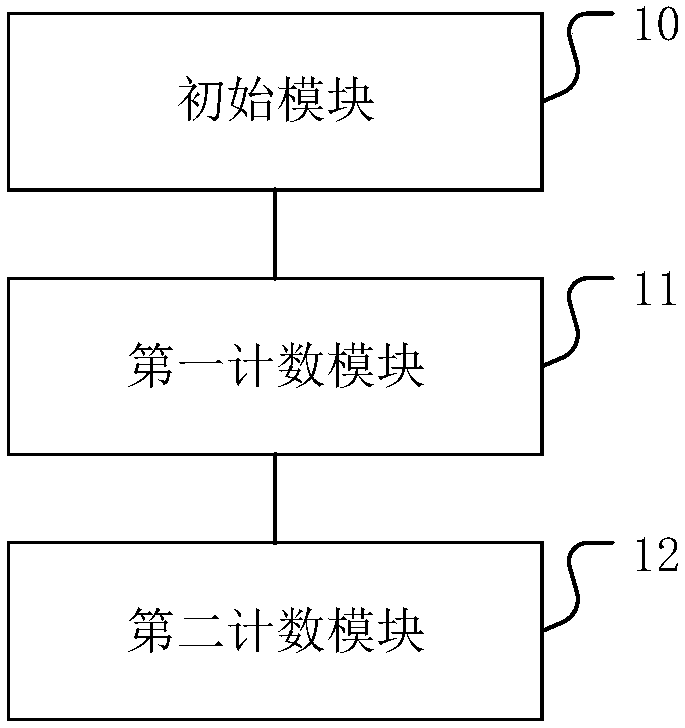

[0066] The embodiment of a CPLD-based clock counting method has been described in detail above. The present invention also provides a CPLD-based clock counting device. Since the embodiment of the device part corresponds to the embodiment of the method part, therefore For the embodiments of the apparatus part, please refer to the description of the embodiments of the method part, and details are not described here for the time being.

[0067] image 3 A structural diagram of a CPLD-based clock counting device provided by an embodiment of the present invention. like image 3 As shown, a CPLD-based clock counting device provided by an embodiment of the present invention includes:

[0068] The initial module 10 is used for acquiring the event duration of the CPLD, and setting the level representing the counting period according to the event duration.

[0069] The first counting module 11 is used to start counting with the counting period represented by the lowest level in the h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More