A three-valued static memory using word operation circuit and cnfet

A technology of static memory and arithmetic circuit, applied in static memory, digital memory information, information storage, etc., can solve the problems of increasing circuit power consumption, high power consumption of ternary static memory, large short-circuit current, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

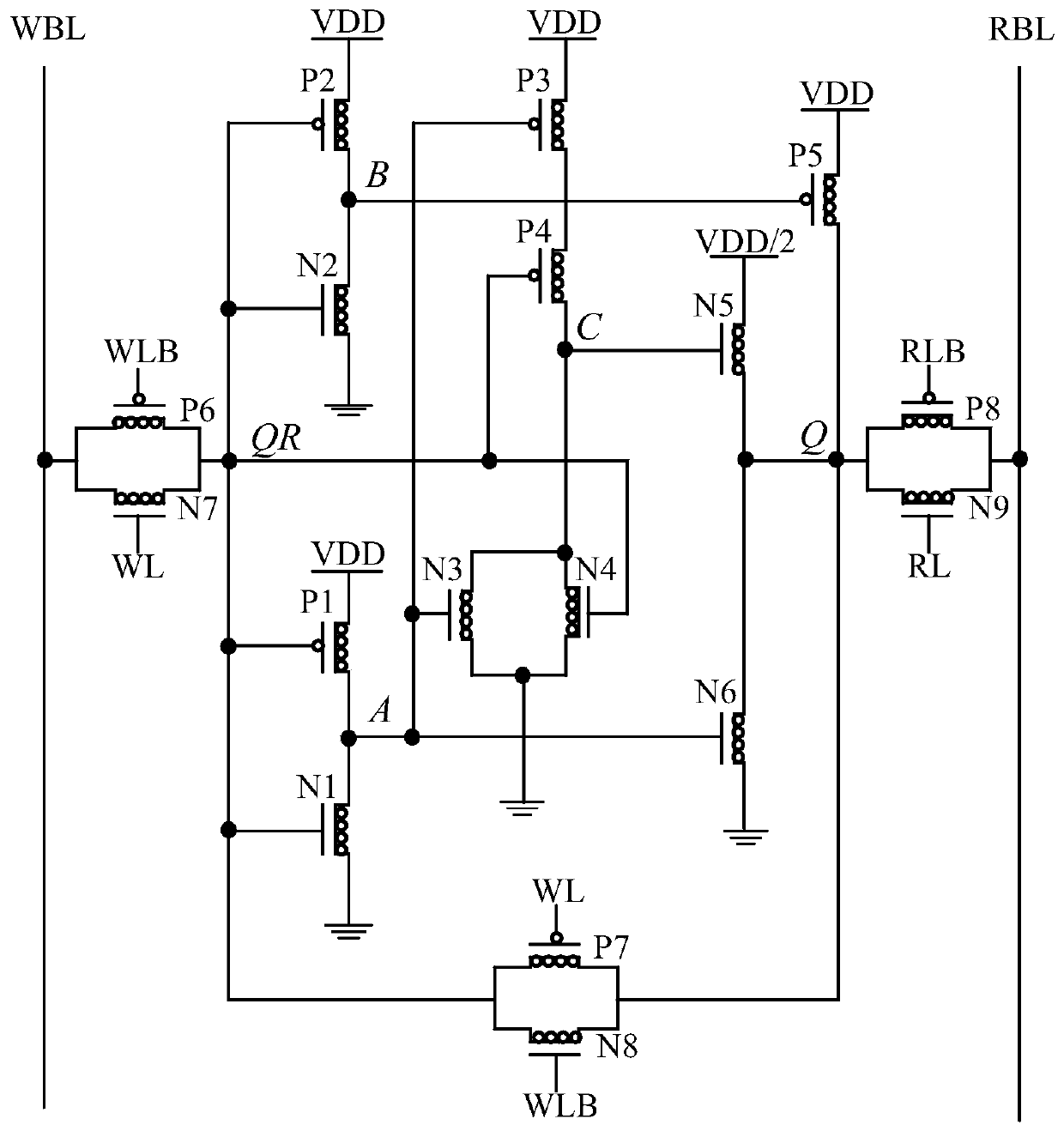

[0015] Example: such as image 3As shown, a three-valued static memory using a word operation circuit and CNFET includes a first P-type CNFET tube P1, a second P-type CNFET tube P2, a third P-type CNFET tube P3, a fourth P-type CNFET tube P4, The fifth P-type CNFET tube P5, the sixth P-type CNFET tube P6, the seventh P-type CNFET tube P7, the eighth P-type CNFET tube P8, the first N-type CNFET tube N1, the second N-type CNFET tube N2, the third N-type CNFET tube N3, fourth N-type CNFET tube N4, fifth N-type CNFET tube N5, sixth N-type CNFET tube N6, seventh N-type CNFET tube N7, eighth N-type CNFET tube N8, ninth N-type tube CNFET tube N9, write bit line WBL, read bit line RBL, write word line WL, inverted write word line WLB, read word line RL, and inverted read word line RLB; the source of the first P-type CNFET tube P1, the second P The source of the third P-type CNFET P2, the source of the third P-type CNFET P3 and the source of the fifth P-type CNFET P5 are all connected...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More