Method of forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve problems such as performance to be improved, and achieve the effects of easy process control, reduced over-etching, and reduced etching loss.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] As mentioned in the background, the performance of semiconductor devices formed in the prior art needs to be improved.

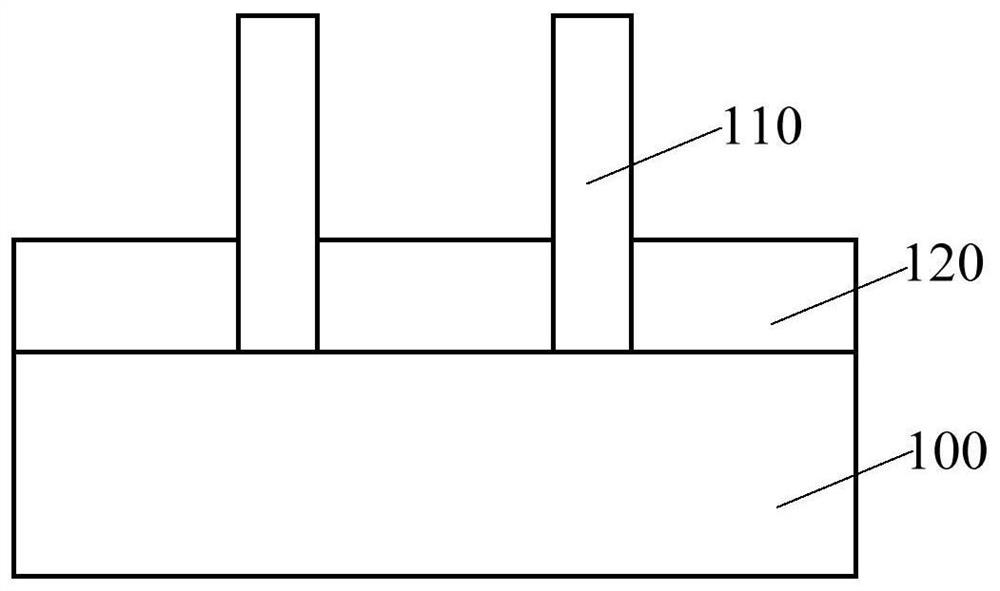

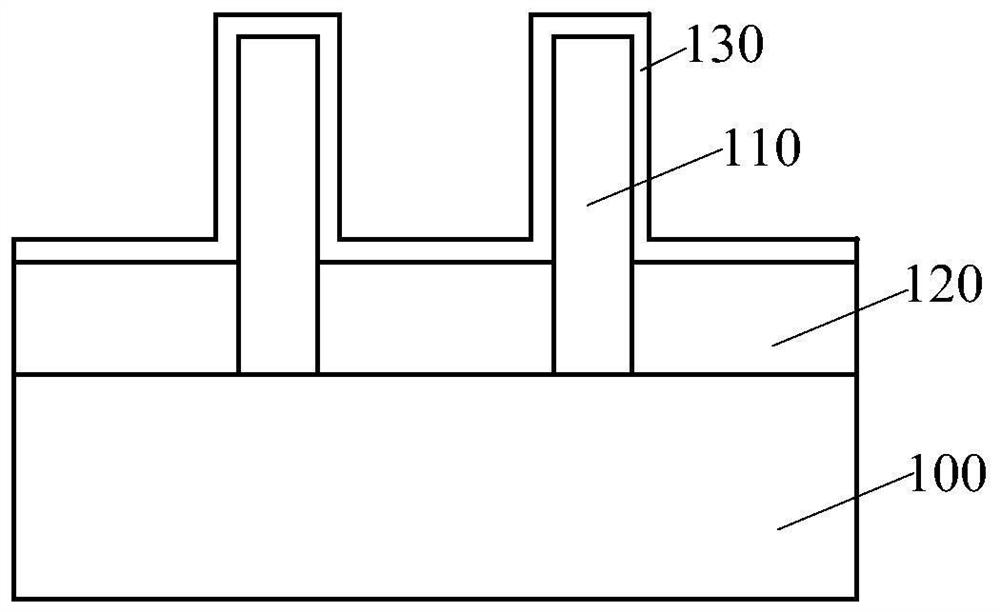

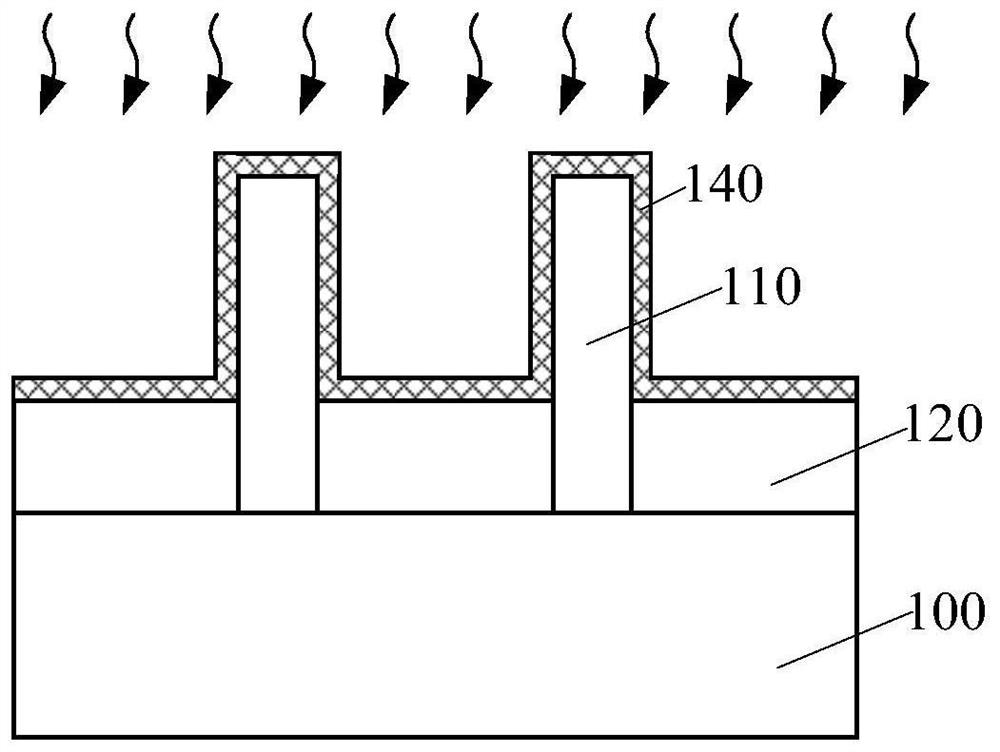

[0025] A method for forming a semiconductor device includes: providing a semiconductor substrate having a fin and an isolation structure covering part of the sidewall of the fin; using a plasma chemical vapor deposition process to form Dummy gate dielectric material layer; forming a dummy gate electrode material layer on the dummy gate dielectric material layer; patterning the dummy gate electrode material layer and the dummy gate dielectric material layer to form the dummy gate dielectric layer and the dummy gate electrode on the dummy gate dielectric layer layer, the dummy gate dielectric layer covers the top surface and sidewall surface of part of the fin; an interlayer dielectric layer covering the sidewall of the dummy gate dielectric layer and the dummy gate electrode layer is formed on the semiconductor substrate and the fin; forming a layer Af...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More