A method for equivalence testing of combinational logic circuits

A combination logic circuit and combination circuit technology, applied in the field of detection, can solve problems such as memory explosion and lack of operability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0038] Embodiment: a kind of combinatorial logic circuit equivalence detection method comprises the following steps:

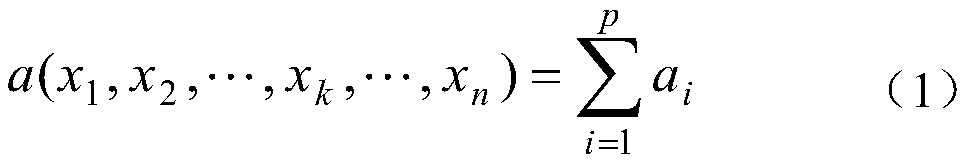

[0039] (1) Record the two combined circuits to be detected as a and b, where the logical expression of a is:

[0040]

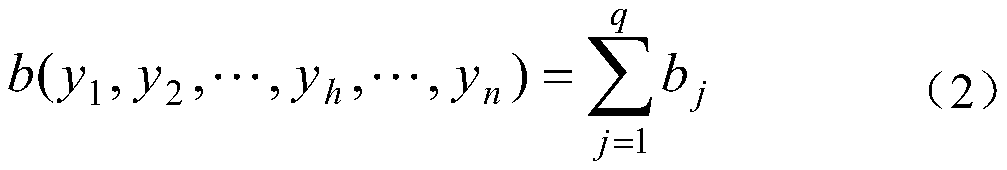

[0041] The logical expression of b is:

[0042]

[0043] Among them, n is the variable number of combinational circuits a and b, ∑ is the summation symbol, p is the number of product terms of combinational circuit a, q is the number of product terms of combinational circuit b, a i is the i-th product term of the combinational circuit a, a i =x' i1 x' i2 ... x' ik ... x' in , k is an integer greater than or equal to 1 and less than or equal to n, x' ik is the product term a i The text variable of the k-th place, indicating the corresponding input variable x k in the product term a i The appearance of the kth bit, x' ik ∈{0,1,-}, when x′ ik = 0, x k with its inverse variable appears in the product term a of the form i The k...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More