An analysis method, system and device suitable for guiding parallelization of association algorithms

A technology of correlation algorithms and analysis methods, applied in computing, instrumentation, error detection/correction, etc., can solve the problems of large unit granularity, lack of real-time flexibility, lack of guidance model for parallelization of correlation algorithms, etc., to achieve the effect of speeding up

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

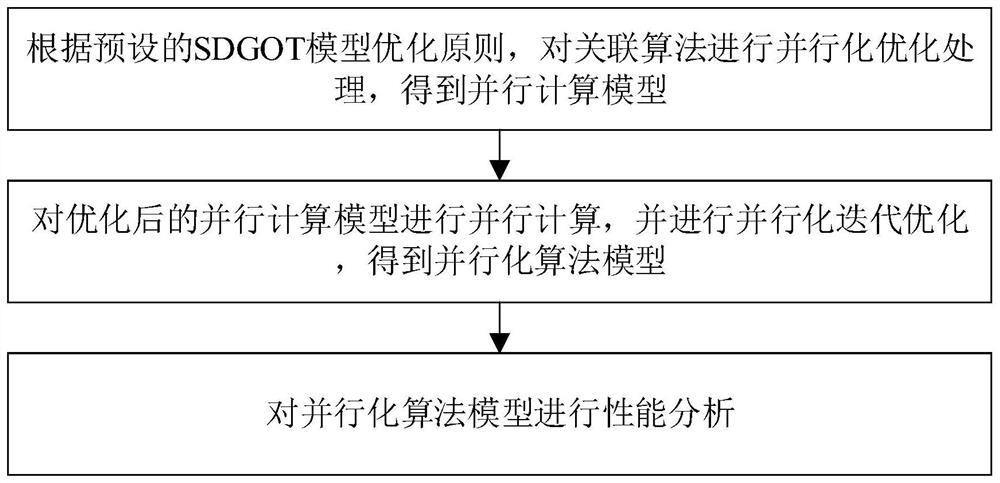

[0058] refer to figure 1 , an analysis method suitable for instructing the parallelization of an association algorithm of the present invention, comprising the following steps:

[0059]According to the preset SDGOT model optimization principle, perform parallel optimization processing on the associated algorithm to obtain a parallel computing model;

[0060] Perform parallel computing on the optimized parallel computing model, and perform parallel iterative optimization to obtain a parallel algorithm model;

[0061] Perform performance analysis on the parallelized algorithm model.

[0062] Further as a preferred embodiment, it also includes the following steps:

[0063] According to the result of the performance analysis, it is judged whether it meets the preset requirements. If so, the optimization calculation is no longer performed; otherwise, the parallelization algorithm model is iteratively optimized again.

[0064] Among them, when the performance analysis results mee...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More