A Method for Reducing Computational Complexity of Equations in Integrated Circuit Design

A computing complexity, integrated circuit technology, applied in CAD circuit design, complex mathematical operations, special data processing applications, etc., can solve the problems of low optimization efficiency of capacitor devices and insufficient optimization of equations, shortening simulation time, The effect of reducing coupling and reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

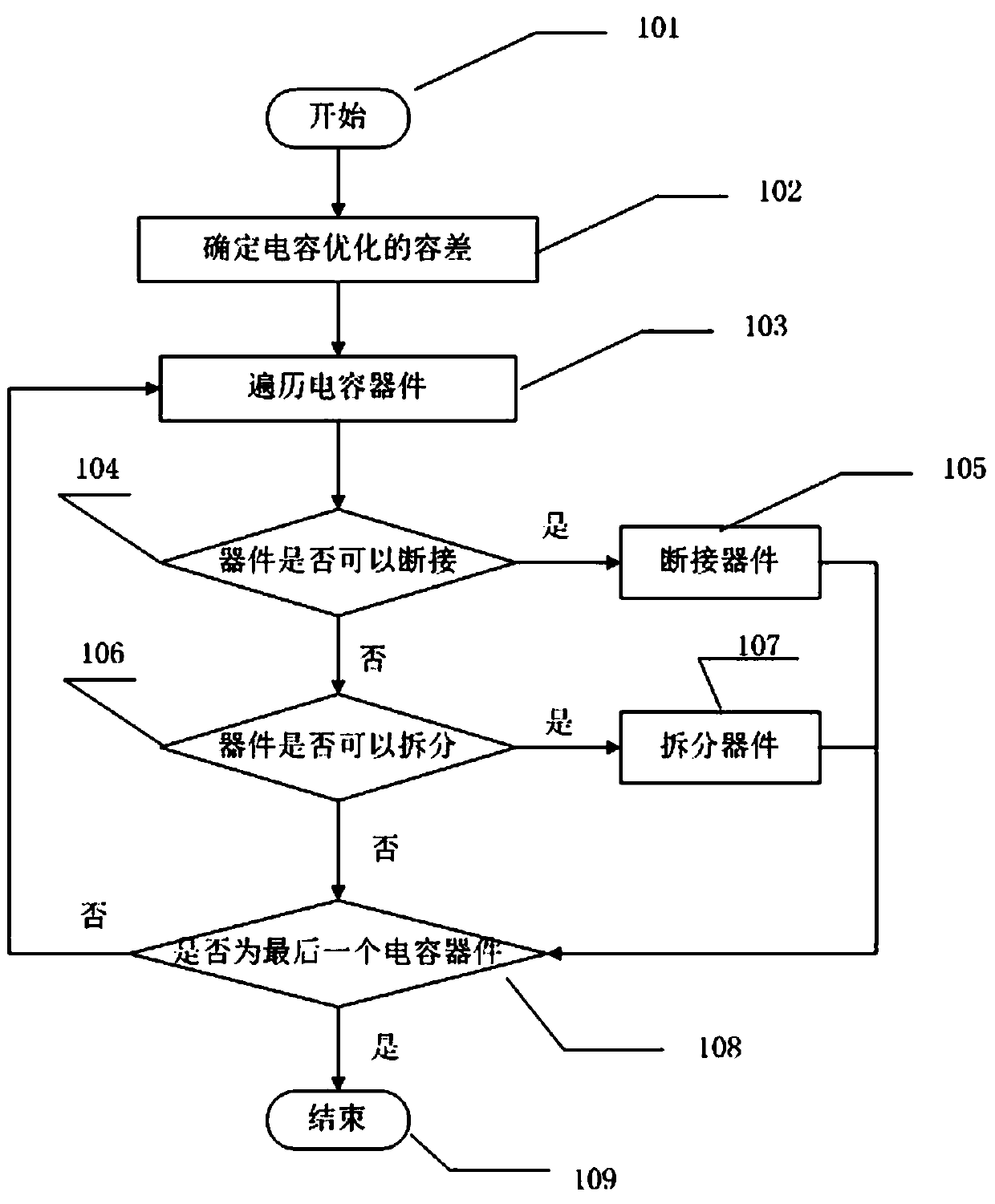

[0020] figure 1 It is a working flowchart of the method for reducing the computational complexity of equations in integrated circuit design according to the present invention. The following will refer to figure 1 , to describe the method for reducing the computational complexity of the equation system in the integrated circuit design of the present invention.

[0021] First, in step 101, start to optimize and enter into an optimization program.

[0022] At step 102, a tolerance for capacitance optimization is determined.

[0023] In this step, all capacitive devices to be optimized are traversed first, the properties of the modules where they are located are judg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More