System and method for evaluating performance of chip through collaboration of multiple processors

A chip performance, multi-processor technology, applied in the direction of electrical digital data processing, instruments, electronic circuit testing, etc., can solve the problems of increasing maintenance difficulty, inability to accurately test chips, and restricting test efficiency, so as to achieve the effect of improving test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

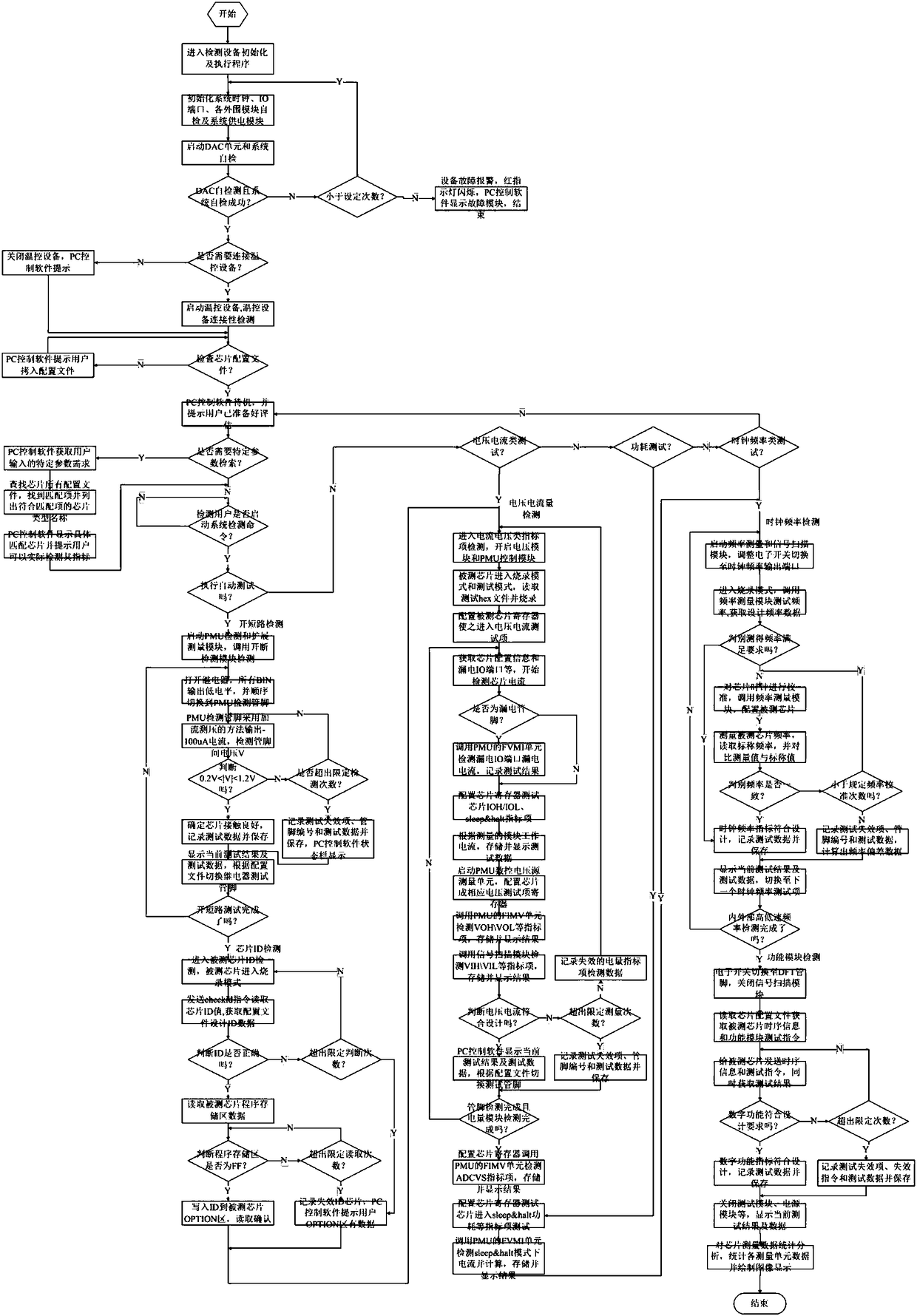

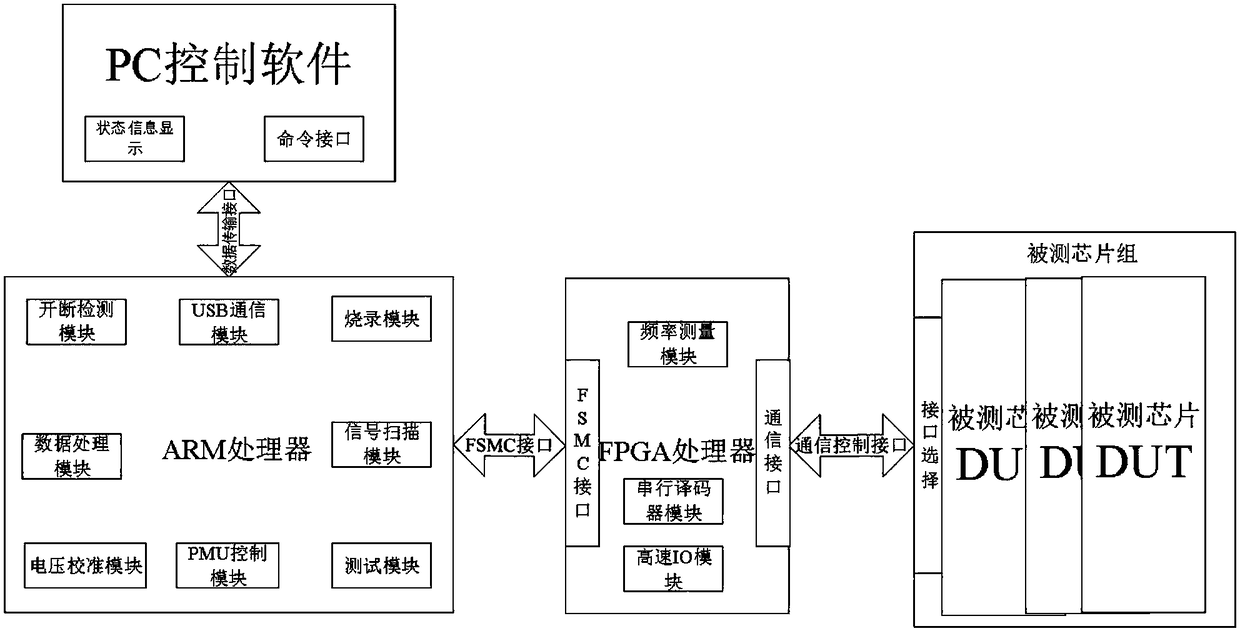

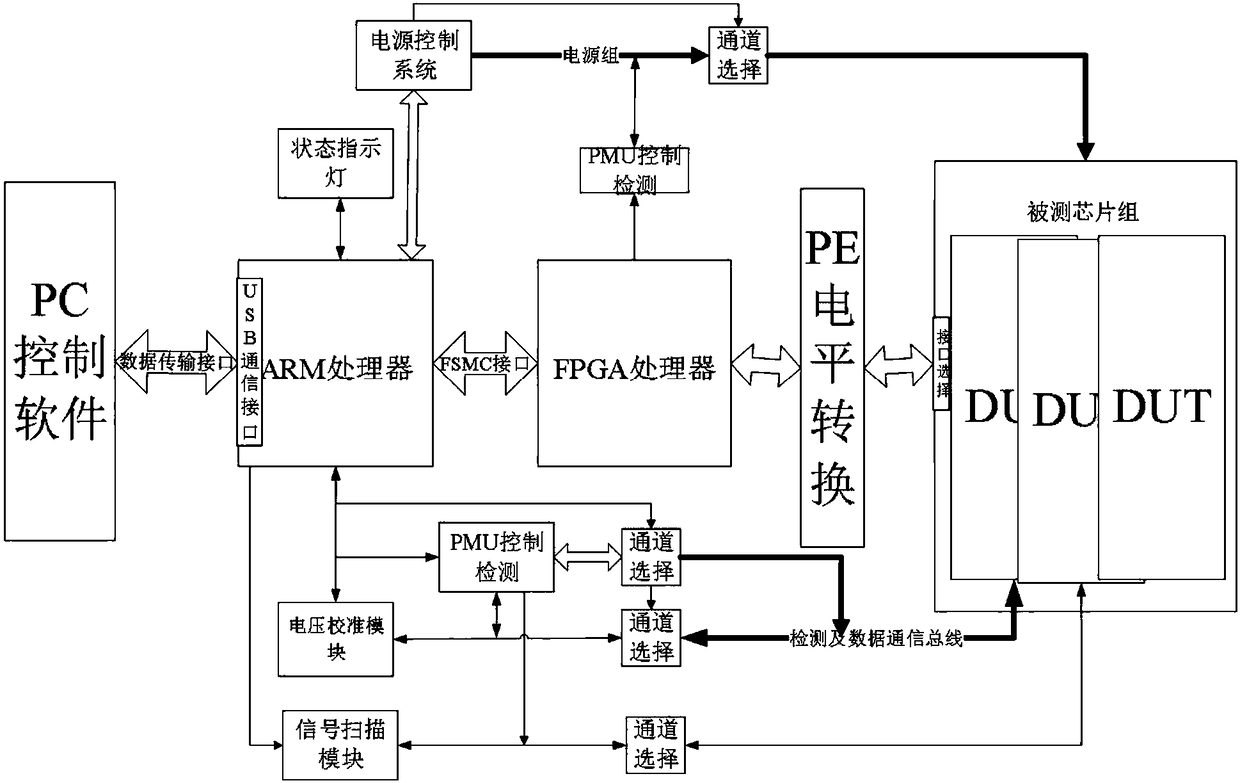

[0066] figure 1 , figure 2 As shown, it is the multi-chip performance index evaluation system of multi-processor coordinated control realized by the present invention. The system can control multi-chips to perform performance index parameter test and evaluation in the R&D and design stage, and use PC control software as the man-machine interface. The test method integrates various types of index tests in a system to test and evaluate the chip, which greatly improves the test efficiency. The system consists of open and short circuit detection module, USB communication processing module, PMU contr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More