A method for testing the interface state of a three-port silicon carbide-based power device

A port silicon carbide and testing method technology, which is applied in the direction of single semiconductor device testing, semiconductor working life testing, instruments, etc., can solve the problem that it is difficult to measure the interface state reliably and accurately

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

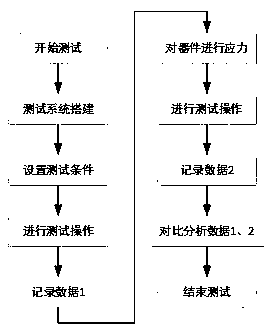

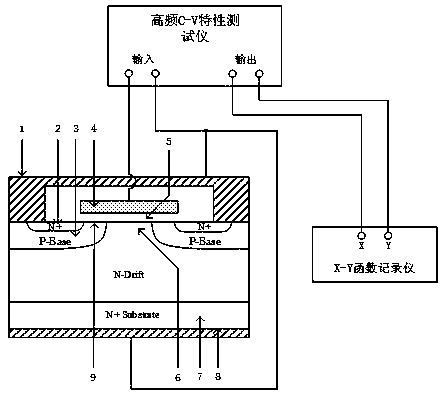

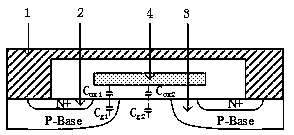

[0029] A method for testing an interface state of a three-port silicon carbide-based power device, comprising the following test steps:

[0030] a) Test system construction: the source 1 of the power device is externally connected to a reverse bias voltage source, the positive pole of the voltage source is connected to the drain 8 of the power device, and the negative pole of the voltage source is connected to the source 1 of the power device, so that the P-type base region 3 and the junction The PN junction of the type field effect region 6 is reverse-biased, and the drain 8 is used as a test current lead-out port to connect an ammeter and the ammeter is connected in series in a circuit composed of the drain 8, the voltage source and the source 1, and the gate 4 is connected with a pulse voltage , the test instrument that the present invention adopts is the Keithley 4200 semiconductor characteristic analyzer of Keithley Company;

[0031] b) Test operation: add a grid pulse vo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More