Two-way positive-end current sampling module and circuit, switch circuit and current sampling method

A current sampling and switching circuit technology, which is applied in the direction of electronic switching, measuring current/voltage, measuring electricity, etc., can solve the problems of low precision, inability to guarantee the consistency of output branch current sampling, complex sampling circuit structure, etc., to ensure consistency The effect of realizing high-precision multi-channel positive terminal current sampling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with specific drawings and embodiments.

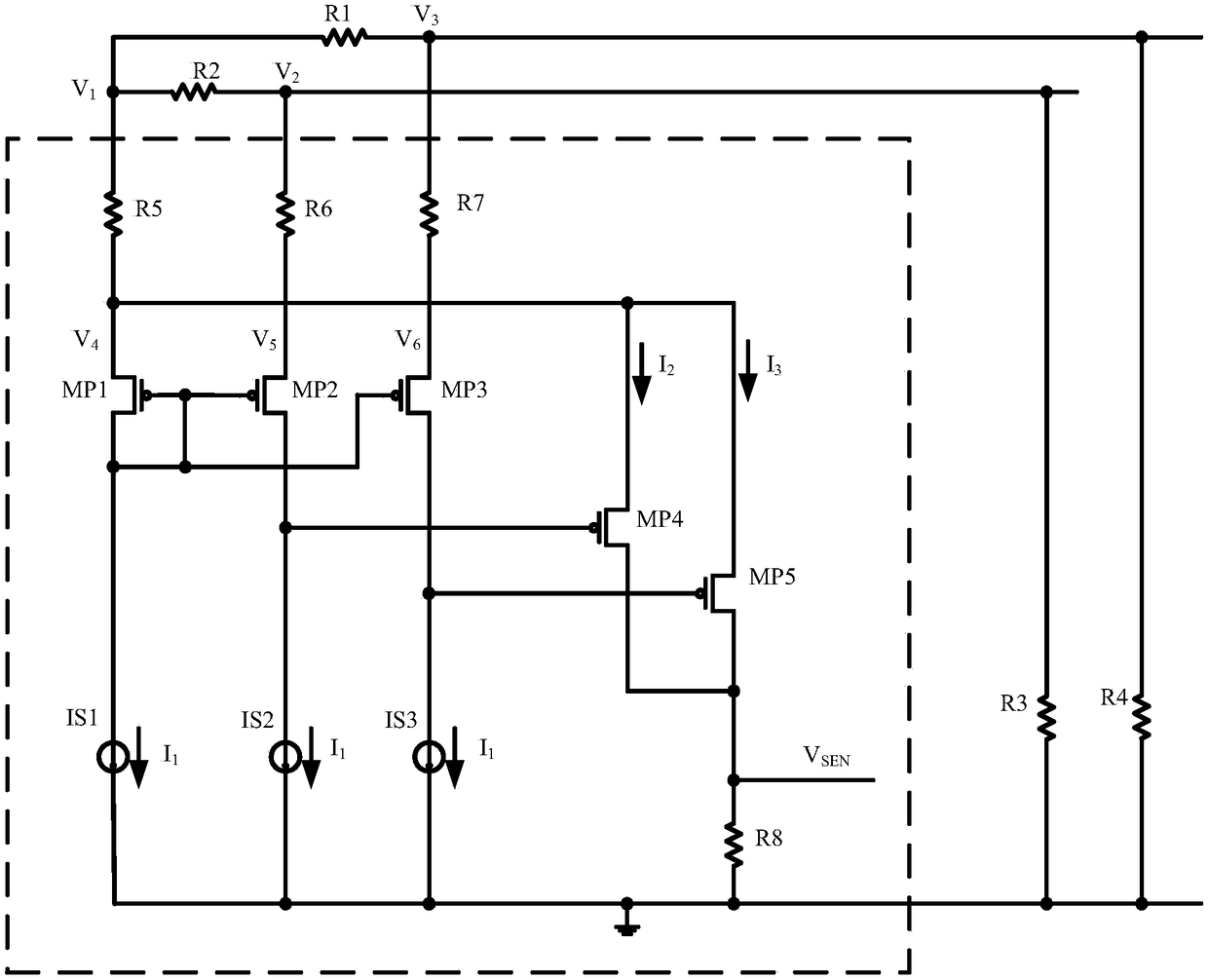

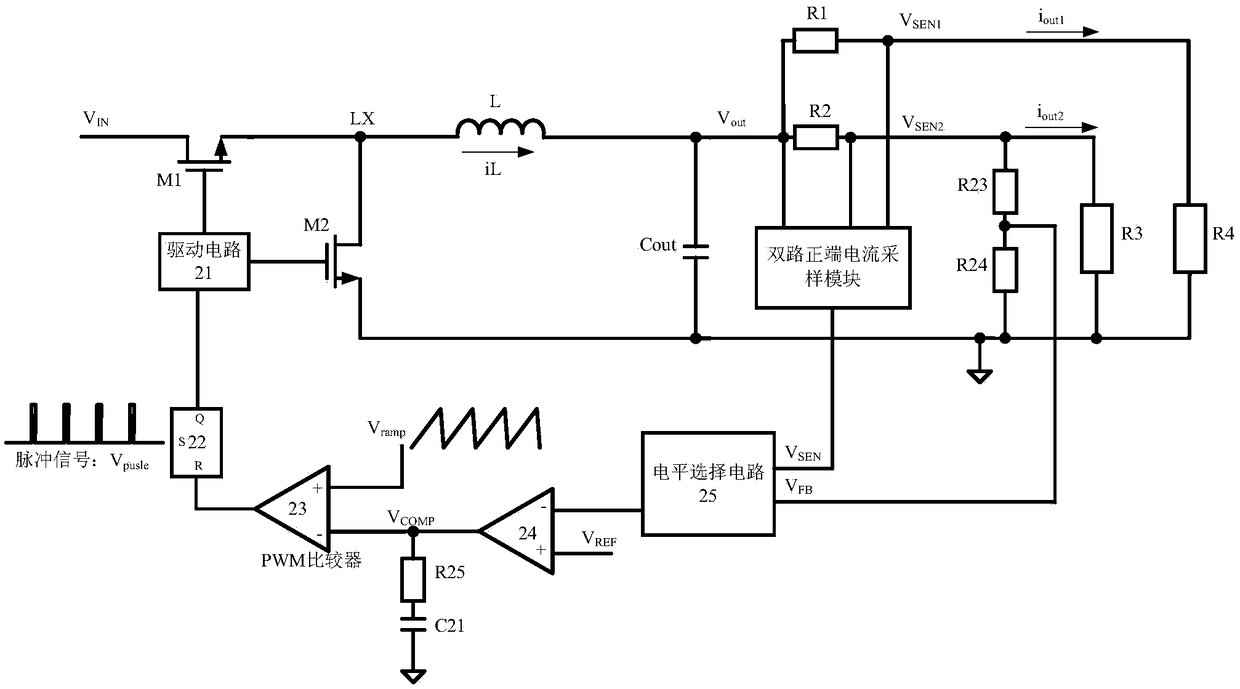

[0031] The present invention provides a high-precision dual-channel positive-terminal current sampling module, and a dual-channel positive-terminal current sampling circuit such as figure 1 As shown; the dotted box part is a dual positive terminal current sampling module, which can be made into a chip;

[0032] The dual-channel positive terminal current sampling module includes resistors R5, R6, and R7 with the same resistance value, the same PMOS transistors MP1, MP2, and MP3, the same PMOS transistors MP4 and MP5, resistor R8, and current sources IS1, IS2, and IS3 with equal currents. ; Among them, MP1, MP2, and MP3 are low-voltage PMOS tubes, and MP4 and MP5 are thin-gate oxide high-voltage PMOS tubes; outside the dotted line frame are the peripheral devices of the chip, which form a dual-channel positive terminal current sampling circuit with the chip; wher...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com