Combined mask plate, semiconductor device, and forming method of same

A mask and mask layer technology used in the field of semiconductors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

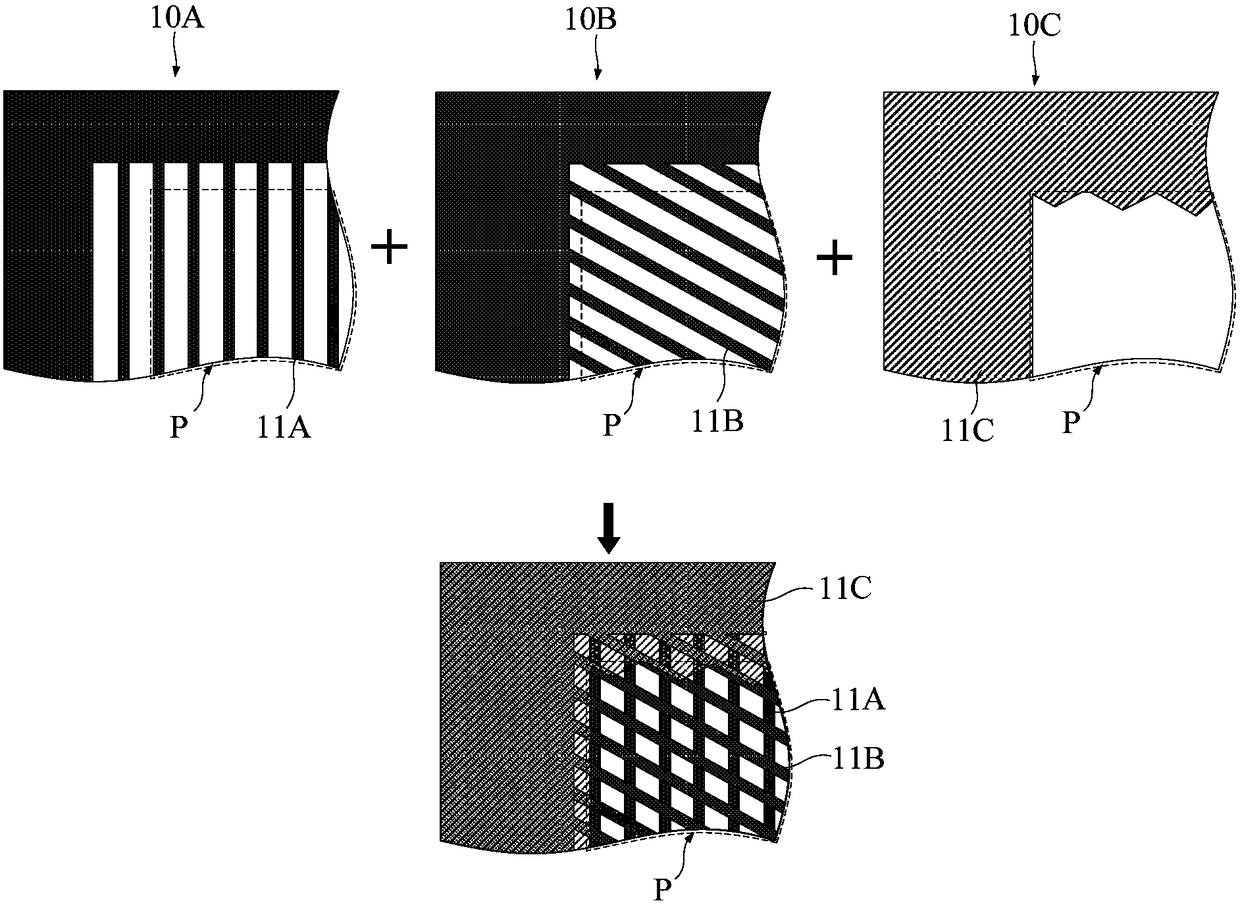

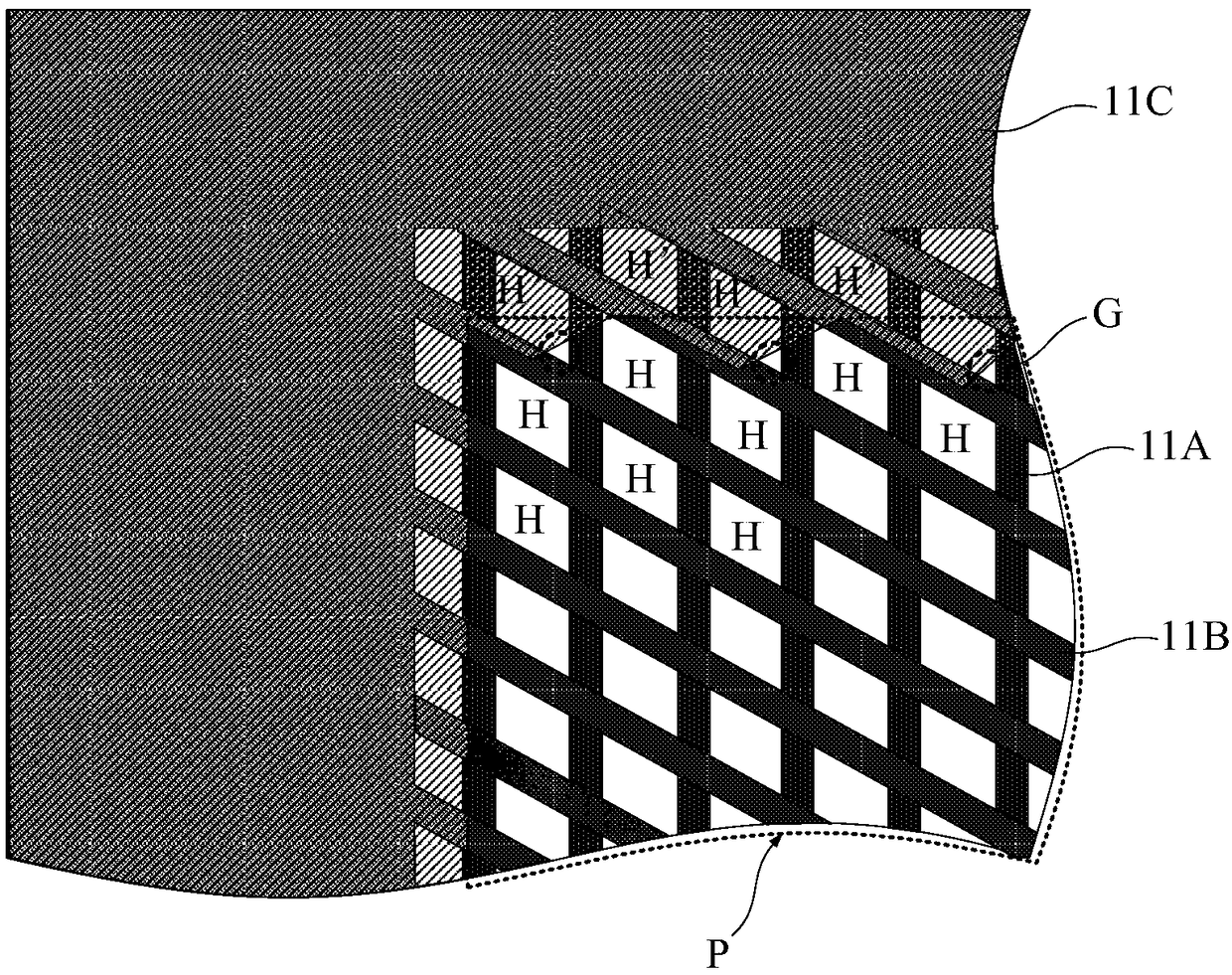

[0087] Figure 3a It is a schematic structural diagram of the combined mask plate in the first implementation of the present invention, Figure 3b for Figure 3a The mask pattern of the combined mask in Embodiment 1 of the present invention, where the first mask and the second mask are superimposed on each other, Figure 3c for Figure 3a Shown is the mask pattern of the combined mask in Embodiment 1 of the present invention after the three masks are superimposed on each other. combine Figure 3a ~ Figure 3c As shown, the combined mask includes:

[0088] The first mask plate 100A is formed with a plurality of parallel first lines 110A extending along the first direction (Y direction), and the first lines completely correspond to the array region P;

[0089] The second mask plate 100B is formed with a plurality of parallel second lines 110B extending along the second direction (Z direction), and the second lines 110B correspondingly pass through the array area P and extend...

Embodiment 2

[0118] The difference from Embodiment 1 is that in this embodiment, the extension direction of the first line of the first mask is not parallel to the straight edge of the first exposed area of the third mask, nor is it parallel to the straight edge of the third mask. The straight edge of the second exposed area of the second mask; the second line of the same second mask is not parallel to the straight edge of the first exposed area of the third mask, nor parallel to the straight edge of the second exposed area of the third mask side. In this way, in the inner array defined by the first lines and the second lines, all the boundaries are non-linear boundaries (for example, wavy boundaries).

[0119] Figure 4a It is a schematic structural diagram of the combined mask plate in the second implementation of the present invention, Figure 4b for Figure 4a The mask pattern of the composite mask in the second embodiment of the present invention after the first mask and th...

Embodiment 3

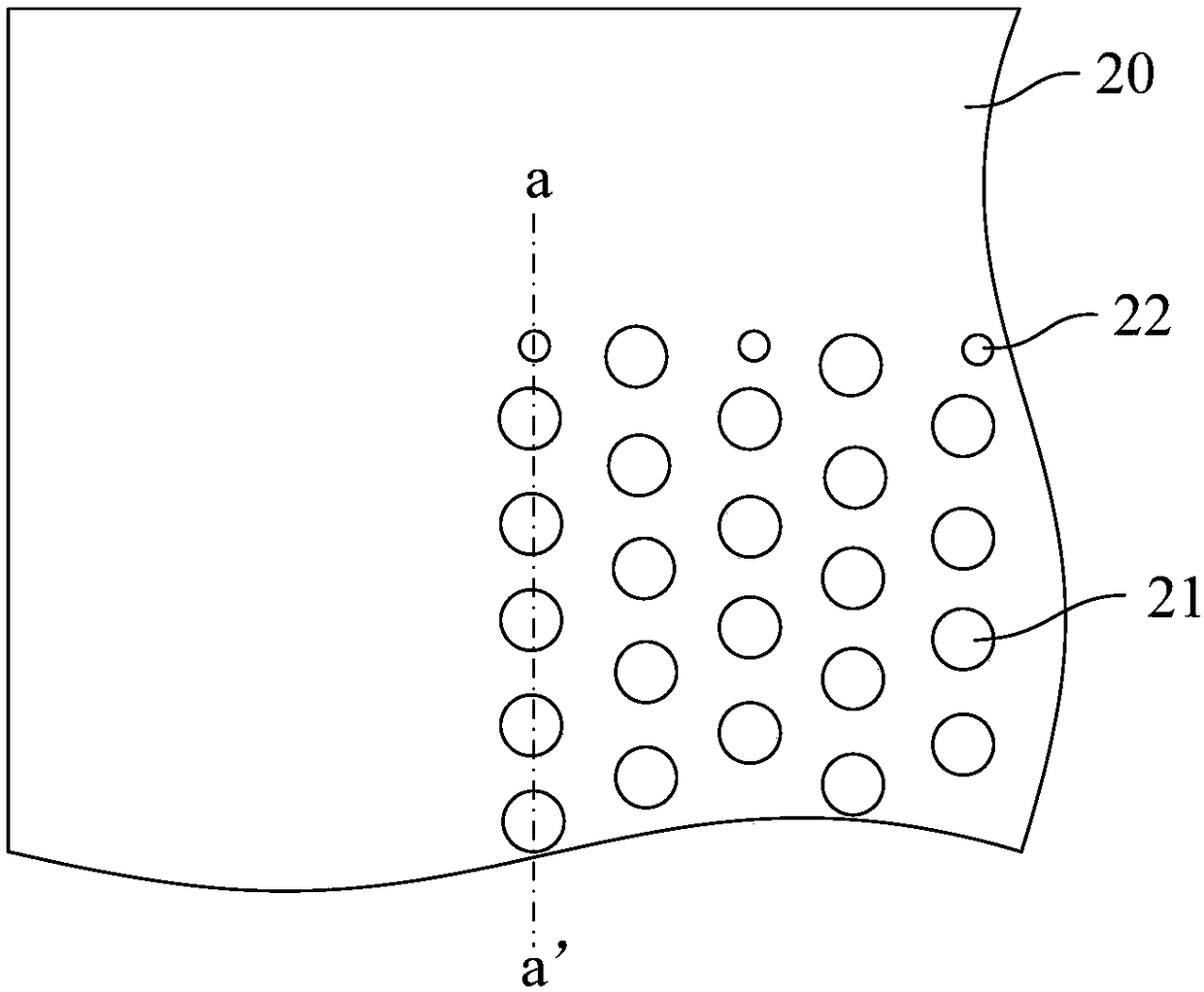

[0125] Based on the above combined mask, the present invention also provides a method for forming a semiconductor device. Figure 5 It is a schematic flowchart of a method for forming a semiconductor device in Embodiment 3 of the present invention. Such as Figure 5 As shown, in this embodiment, the method for forming the semiconductor device includes:

[0126] Step S100, providing a substrate on which a mask layer is formed;

[0127] Step S200, performing a photolithography process using the combined mask as described above to form an array of openings in the mask layer, and the pattern of the array of openings is defined by the overlapping of the combined mask;

[0128] Step S300 , using the mask layer formed with the array of openings as a mask to etch the substrate, so as to form an array of through holes corresponding to the array of openings in the array region of the substrate.

[0129] Since the combined mask as described above can be used to define the grid corresp...

PUM

| Property | Measurement | Unit |

|---|---|---|

| hardness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More