Package stack structure and manufacturing method thereof

A technology of packaging stacking and packaging structure, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problems of increasing the thickness of the overall stacked packaging structure and manufacturing costs, and improve product yield. , the effect of reducing size and manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

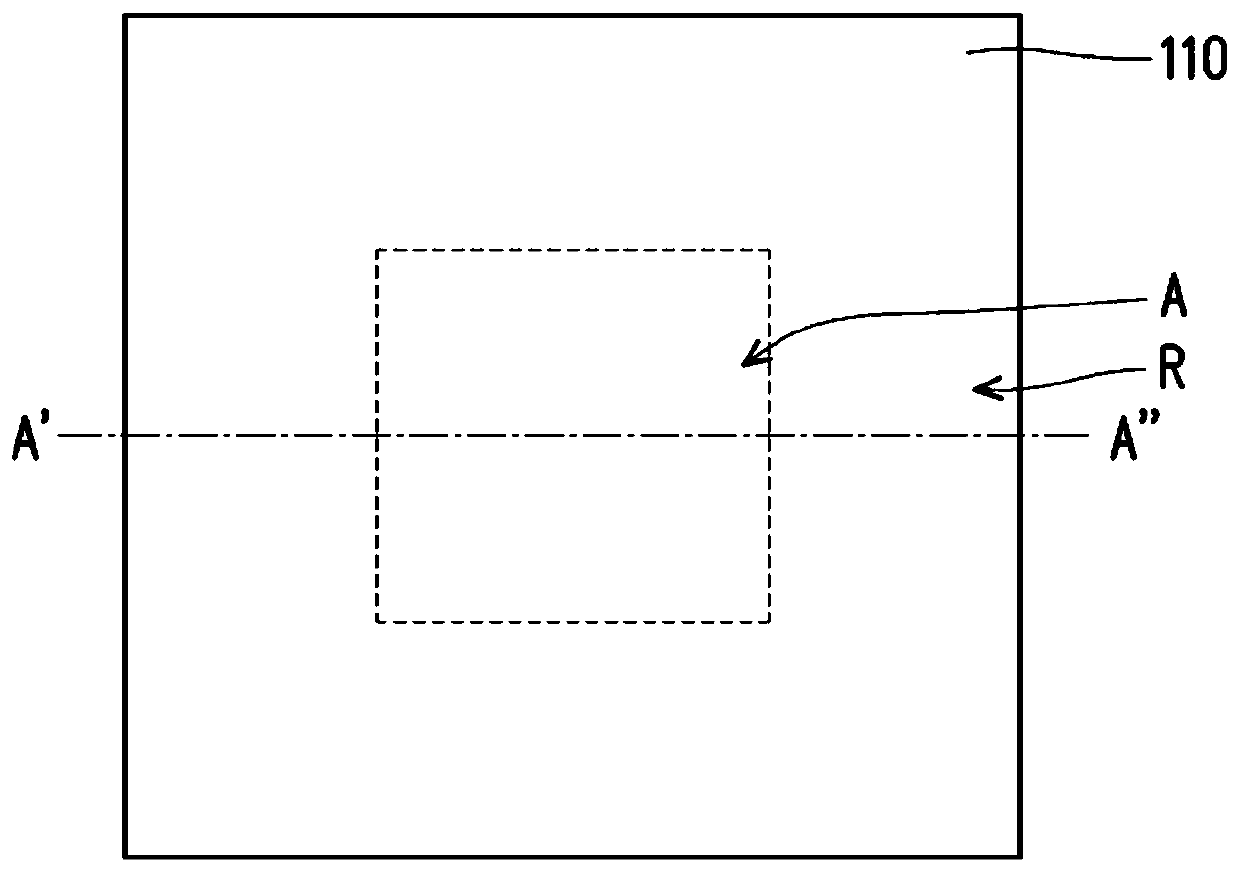

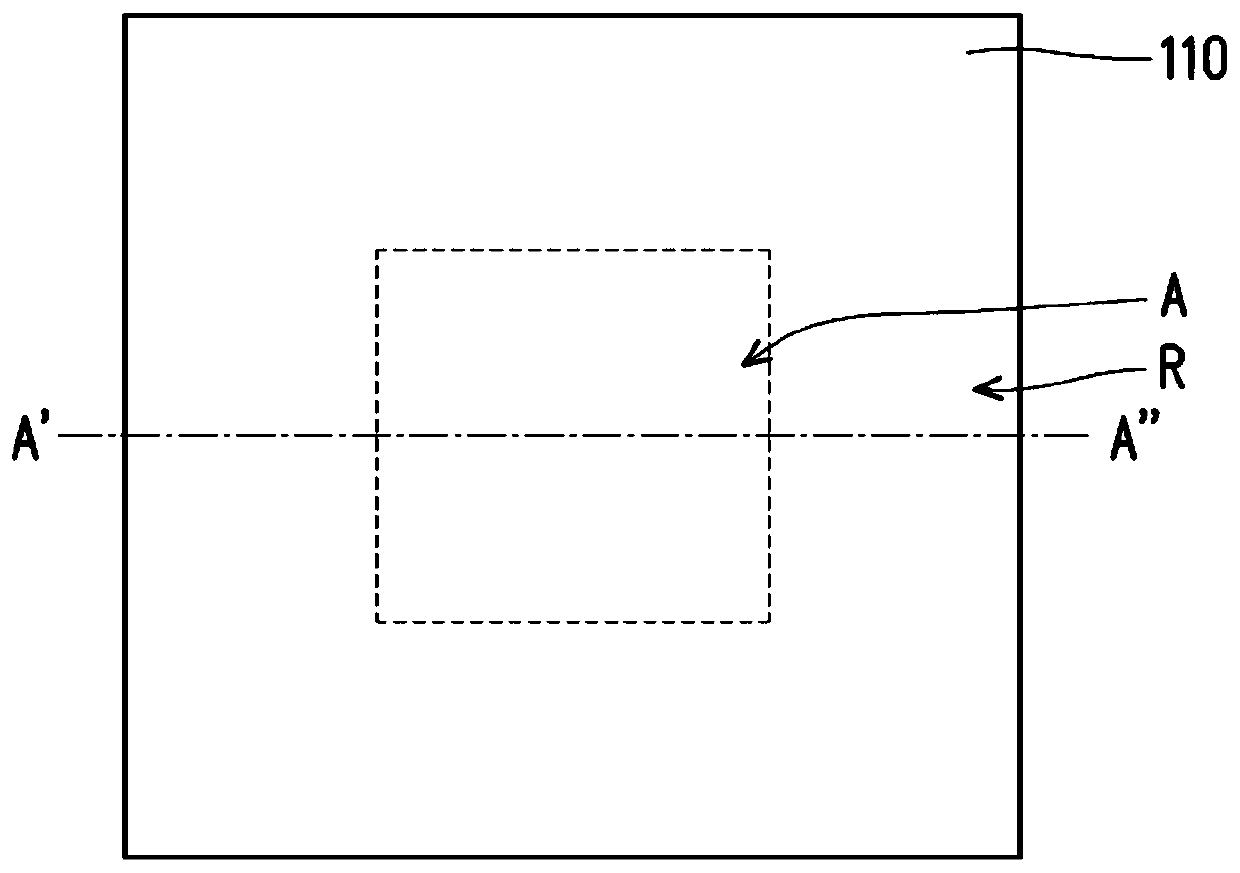

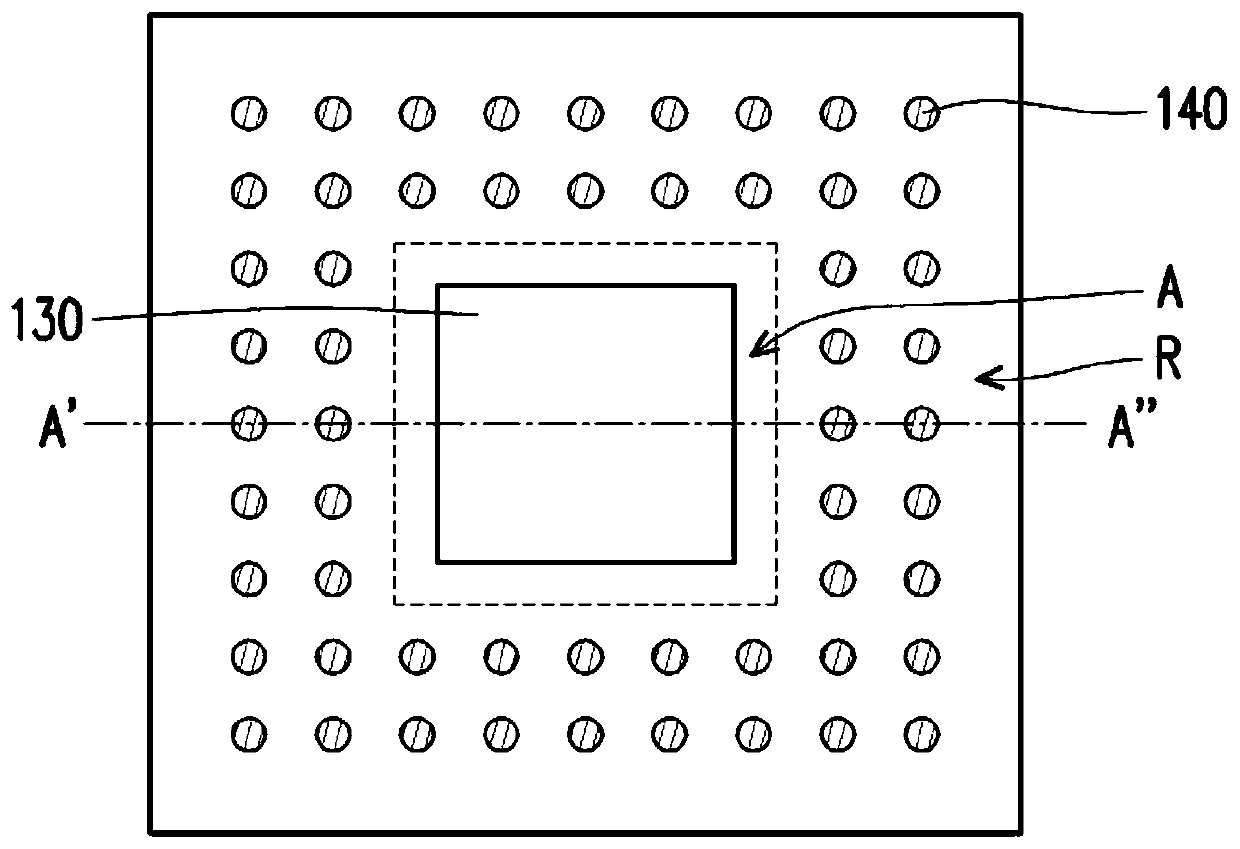

[0060] Figure 1A to Figure 1G is a simplified top view of the manufacturing process of a package stack structure 10 according to an embodiment of the present invention. Figure 2A to Figure 2G is along Figure 1A to Figure 1G The cross-sectional schematic diagram of the section line A'-A", Figure 2H is along Figure 1G The cross-sectional schematic diagram of the section line B'-B".

[0061] Please refer to Figure 1A and Figure 2A ,in Figure 1A omitted to show Figure 2AThe first circuit layer 114 in. Firstly, a first carrier 110 is provided. The first carrier 110 has a first surface S1 and a second surface S2 opposite to the first surface S1 . The first carrier 110 includes a first core layer 112 , a first wiring layer 114 on the first surface S1 , a second wiring layer 116 on the second surface S2 , and a plurality of via holes 118 . The first core layer 112 is the middle layer of the first carrier 110, and its material includes, for example, glass, epoxy resin,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More