FPGA verification system of PD (USB Type-C Power Delivery) protocol chip

A protocol chip and verification system technology, which is applied in the field of FPGA verification system, can solve problems such as unsatisfactory interfaces, and achieve the effect of being suitable for popularization and application, realizing speed and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010] The technical solutions in the embodiments of the present invention will be described in detail below with reference to the drawings in the embodiments of the present invention. It should be understood that the specific embodiments described below are only used to explain the present invention, not to limit the present invention.

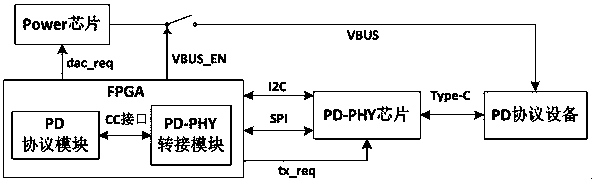

[0011] Such as figure 1 As shown, an FPGA verification system for a PD protocol chip includes an FPGA verification board, a Power chip and a PD-PHY chip. The Power chip is connected to the PD protocol device. The FPGA verification board is connected to the Power chip and the PD-PHY chip respectively. The PD-PHY chip is connected to the PD protocol device through a Type-C interface. Wherein, the FPGA verification board includes a PD protocol module and a PD-PHY transfer module connected to each other.

[0012] The PD protocol module is connected to the Power chip, and is used to send a voltage control signal dac_req to the Power chip to co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More