Universal full-hardware one-step 1588 clock synchronization device and method

A clock synchronization and all-hardware technology, applied in the field of communication, can solve problems such as the inability to guarantee the clock stability of network equipment, the poor versatility and portability of synchronization platforms, and CPU processing congestion, so as to eliminate delay uncertainty and achieve accurate arrival Timestamp, the effect of low hardware requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with the accompanying drawings.

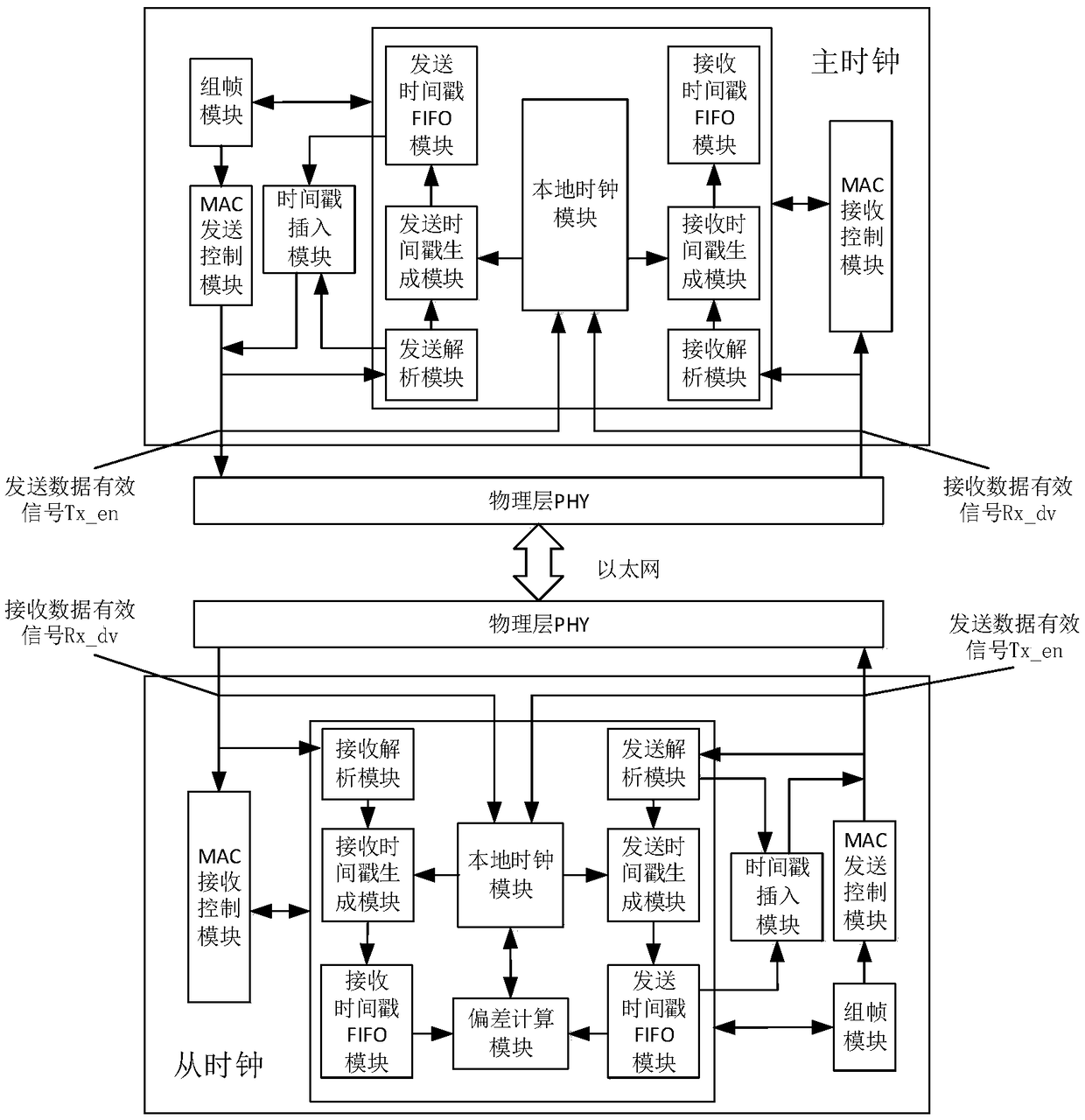

[0043] Refer to attached figure 1 The block diagram of the device further describes the device of the present invention.

[0044] The device of the present invention has a framing module 1, a MAC sending control module 2, a MAC receiving control module 3, an analysis module 4, a timestamp generation module 5, a first-in-first-out queue timestamp FIFO module 6, a local clock module 7, and a deviation calculation module 8, Timestamp insertion module 9; the output end of the framing module 1 is connected to the input end of the MAC transmission control module 2; the output end of the MAC transmission control module 2 is connected to the input end of the analysis module 4; the output end of the analysis module 4 is connected to the timestamp generation module 5 The input end is connected; the output end of the timestamp generation module 5 is connected with the first-in-f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More