Array substrate and display panel

An array substrate and display panel technology, applied in optics, instruments, electrical components, etc., can solve problems such as abnormal resistance, open circuit or short circuit, and affect the yield rate of thin film transistor liquid crystal display products, so as to reduce the probability of electrostatic damage, The effect of improving product yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

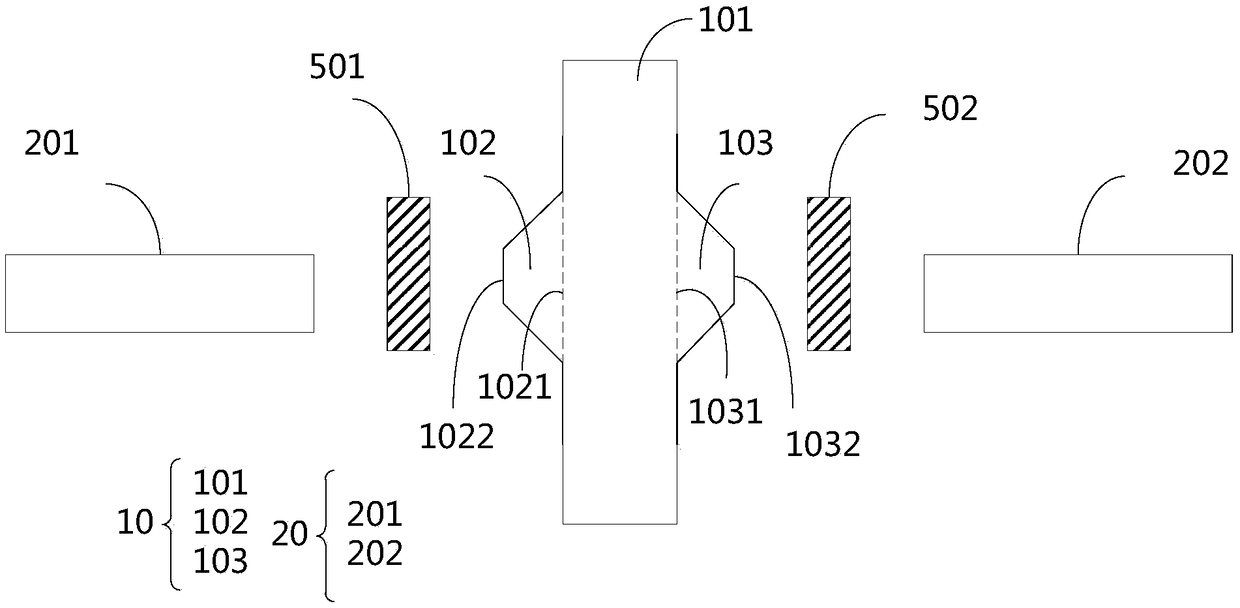

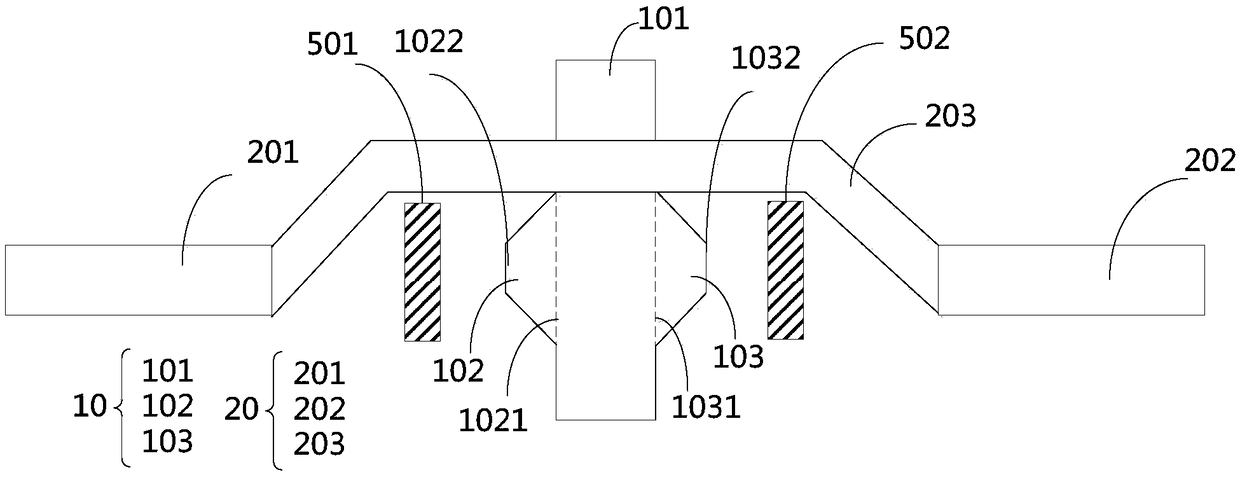

[0023] see figure 1 , figure 1 Schematic diagram of the wiring plane structure of the array substrate provided for the embodiment of the present invention Figure 1 . An embodiment of the present invention provides an array substrate, including:

[0024] The first trace 10 and the second trace 20; wherein, the first trace 10 includes a main body 101 and a first protruding portion 102, and the first protruding portion 102 is arranged on the main body 101 close to the second trace On one side of the wire 20; the second wire 20 is arranged opposite to the first protruding portion 102, and a first electrostatic protection electrode 501 is arranged between the second wire 20 and the protruding portion 102, So that electrostatic damage occurs on the first electrostatic protection electrode 501 .

[0025] The first routing 10 separates the second routing 20 into a first part 201 and a second part 202, the first routing further includes a second protrusion 103, and the first protr...

Embodiment 2

[0035] The array substrate according to the first embodiment will be further described in detail below with an example.

[0036] The array substrate provided by the embodiments of the present invention may be implemented in combination with one or more first wirings and one or more second wirings.

[0037] In this embodiment, it will be described by taking that there is one first wiring and two second wirings on the array substrate as an example.

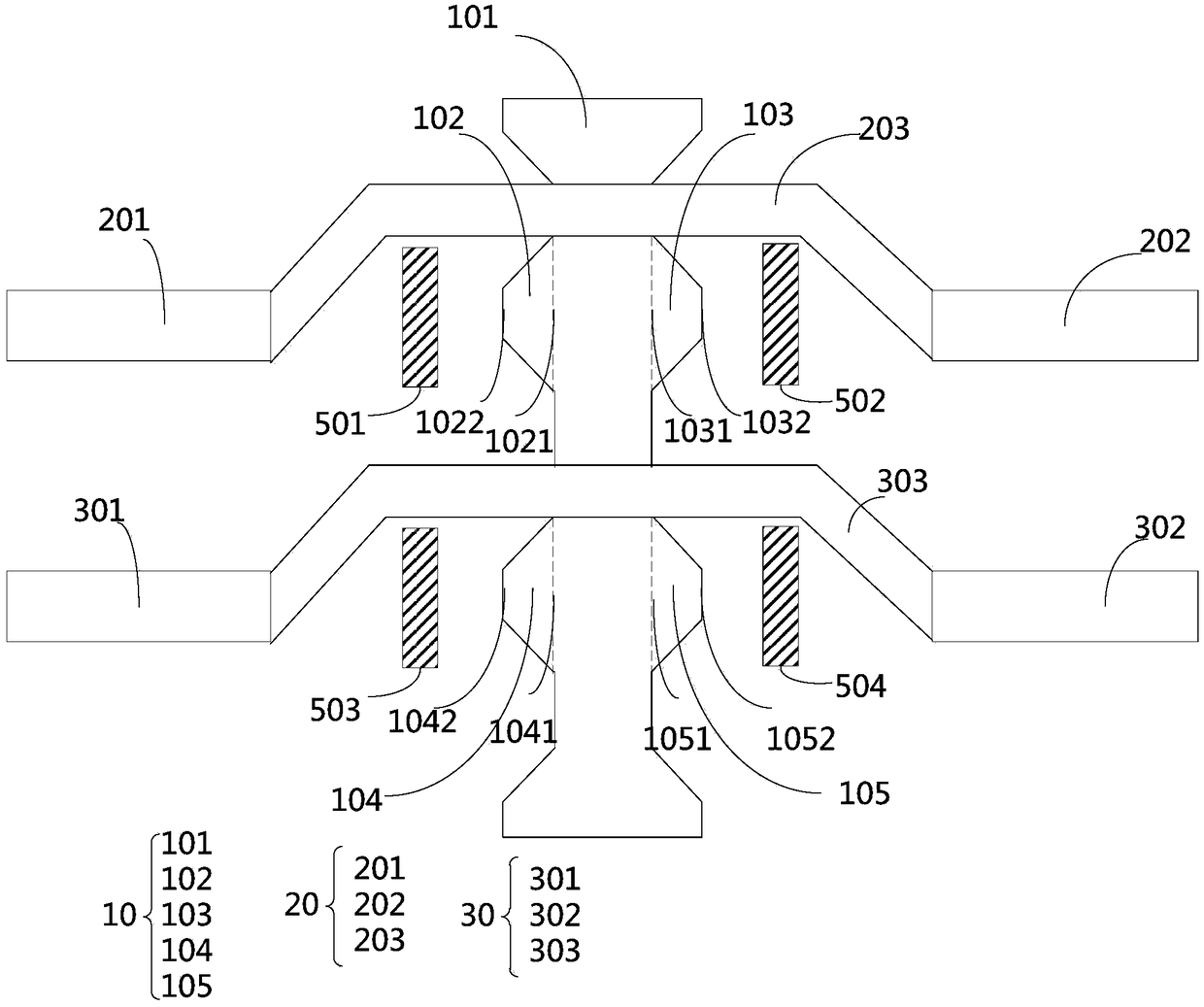

[0038] see image 3 , image 3 A schematic plan view of a partial wiring area of an array substrate provided by a preferred embodiment of the present invention.

[0039] An embodiment of the present invention provides an array substrate, including:

[0040]The first wiring 10, the second wiring 20 and the third wiring 30;

[0041] Specifically, the first wiring 10 may be a peripheral wiring or a common electrode line, the second wiring 20 may be a scanning line or a common electrode line, and the third wiring 30 may be a scann...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More